在数字化高速发展的当下,人工智能、大数据处理、物联网等前沿技术日新月异,现代计算需求面临着严峻挑战。海量数据的爆发式增长,让传统计算架构在处理大规模数据时显得力不从心,效率低下、能耗过高、处理速度瓶颈等问题愈发突出。以人工智能领域为例,深度学习模型训练需要进行海量矩阵运算和复杂的神经网络计算,对计算设备的计算能力和并行处理能力要求极高;在大数据分析场景中,快速处理TB甚至PB级数据,传统架构难以在可接受时间内完成任务。这些挑战迫切需要计算架构创新,以突破现有局限,满足不断增长的计算需求。

为应对上述难题,向量扩展(Vector Extension,RVV)作为RISC-V指令集架构的重要拓展被正式引入。RISC-V指令集架构以其开源开放特性著称,赋予了开发者在设计处理器时极大的灵活性与可扩展性,可针对不同应用场景进行定制化设计。RVV向量扩展通过引入向量指令,实现了对多个数据元素的并行处理,为提升计算性能提供了全新的途径。相较于传统的标量计算模式,向量计算在多媒体数据处理、科学计算等领域展现出显著优势,能够有效减少指令执行次数,进而降低计算延迟,全面提升系统整体性能。RVV的出现,为开发者提供了一种高效、灵活且具有成本效益的解决方案,有力推动了计算架构的创新发展,在诸多领域呈现出巨大的应用潜力。在RVV发展浪潮中,赛昉科技昉·天枢-83(Dubhe-83) CPU IP 崭露头角。

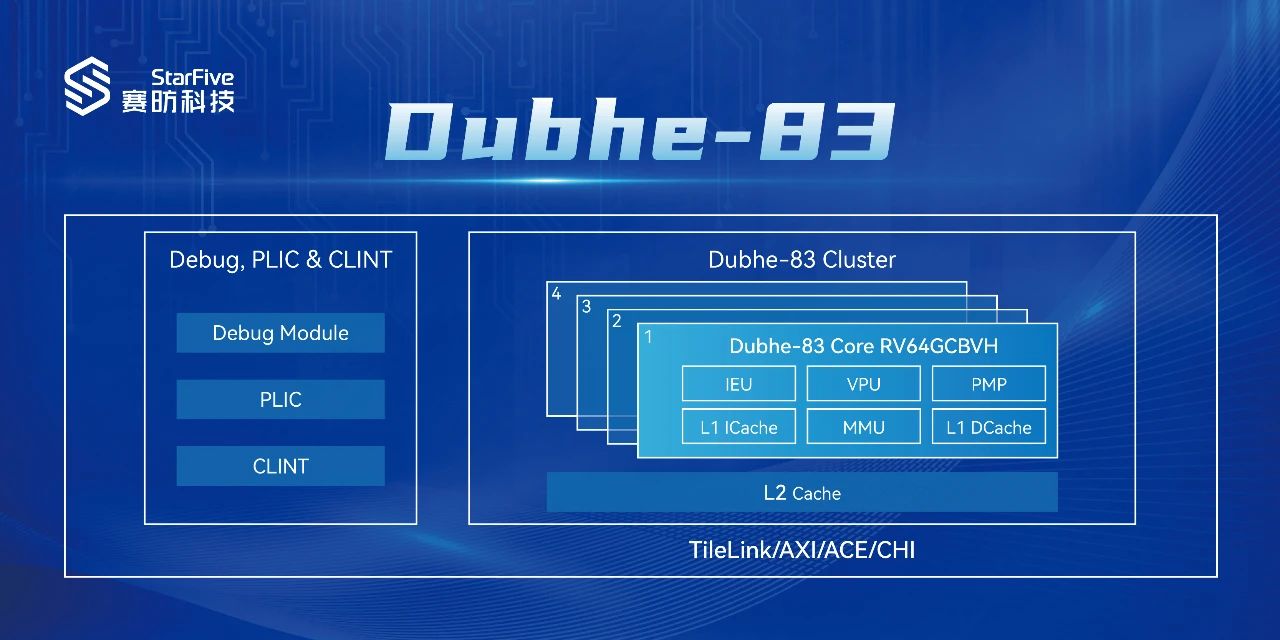

昉·天枢-83 RISC-V CPU IP

Dubhe-83是一款能效卓越的处理器,具备诸多先进特性:

1. 指令集支持

全面兼容RVA23与RVV Crypto指令集,赋予芯片卓越的指令处理能力,从容应对复杂计算任务。在加密应用场景中,RVV Crypto指令集提供硬件级加密加速,极大提升数据加密与解密效率,为数据安全提供坚实保障。

2. 前端取指和分支预测策略

前端取指和分支预测采用Decouple策略,将取指和分支预测两个关键操作解耦,更高效地处理指令流。同时,分支预测采用业界先进的TAGE-Style算法,能更精准预测程序分支走向,减少因分支预测错误导致的流水线停顿,提升处理器执行效率。

3. 流水线设计

拥有10-14 Stage的Pipeline,合理的流水线深度设计在保障指令处理效率的同时,兼顾硬件复杂度与成本。通过多级流水线操作,指令可在不同阶段并行处理,加快指令执行速度。

4. 解码和提交机制

采用3-Way Decode/Rename/Commit机制,可同时对三条指令进行解码、重命名和提交操作,进一步提升指令处理并行度,提高处理器整体性能。

5. 性能表现

在Benchmark SPECint2006测试中,Dubhe-83分数达9.4/GHz,充分展现其在整数计算性能方面的出色表现,能满足多种对整数运算要求较高的应用场景。

Dubhe-83在RVV上具有显著的技术亮点和优势:

1. 向量计算单元设计

Dubhe-83的Vector的VLEN=DLEN=256,配备2条128-bit的计算单元。此设计大幅提升向量计算能力,可同时处理2x128-bit的数据元素,在向量运算中充分发挥并行计算优势,加速数据处理。

2. 存储加载单元(LSU)设计

LSU采用2条Pipeline实现方式,Vector Load/Store和 Scalar Load/Store深度融合。Vector Load/Store带宽为2x128-bit,这种融合设计在满足高带宽需求的同时尽可能节省资源(面积)的开销,在数据加载和存储过程中,无论是向量数据还是标量数据,均可高效传输和处理,减少数据访问延迟,提高数据处理效率。

3. 向量工作方式与指令实现

Vector支持LMUL工作方式,每条Vector宏指令采用拆分uop实现方式。只要uop的所有Element在连续两个Cache Line范围内,则该 uop可一次性完成读/写操作。该设计优化了向量指令执行过程,减少指令执行周期,提升向量带宽。

4. 向量Load/Store uop实现优势

Vector Load/Store采用拆分uop实现方式,相较于一些厂商拆分Element的实现方式,在绝大多数应用场景中具有绝对性能优势。这种实现方式能更高效利用存储带宽,减少数据传输次数,提高数据加载和存储效率,进而提升整个系统性能。

5. 乱序执行机制

不仅Scalar采用深度乱序实现方式,Vector也采用深度乱序实现机制。与Vector按序实现方式相比,乱序方式能天然解决许多数据依赖场景。在实际应用中,数据间存在复杂依赖关系,按序执行可能因数据未准备好导致流水线停顿,而乱序执行可灵活调整指令执行顺序,优先执行不依赖未就绪数据的uop,显著提升性能。

6. RVV性能表现

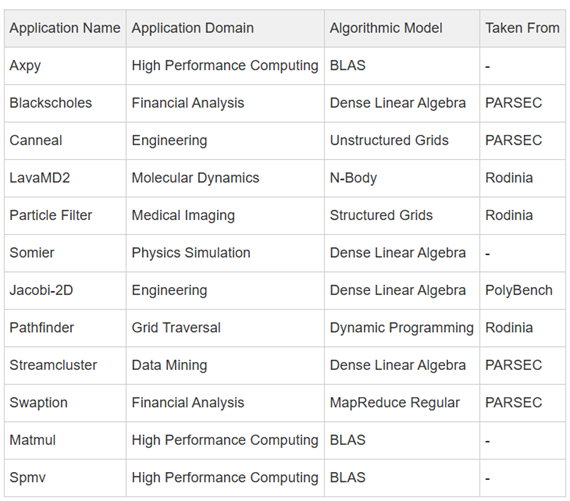

与市场上一些通过In-Order实现的RVV产品相比,Dubhe-83在RiVEC基准测试套件(RiVEC Benchmark Suite,是一个由来自不同领域的数据并行应用程序组成的集合,该套件专注于对向量微架构进行基准测试,各个case的描述详见下表格)上有着显著的性能提升,提升从最少22%(Pathfinder)到最高817%(Matmul),其中,应用于高性能计算领域的几个BLAS算子模型的平均性能提升为357.55%,应用于金融分析/物理仿真/数据挖掘等领域的几个Dense Linear Algebra算子模型的平均性能提升为315.70%。这些实际应用场景中的性能优势,充分证明 Dubhe-83在RVV架构和微架构上的先进性和卓越性能表现,能更好满足用户对高性能计算的需求。

RiVEC Benchmark Suite

-

处理器

+关注

关注

68文章

20325浏览量

254693 -

人工智能

+关注

关注

1819文章

50290浏览量

266826 -

RISC-V

+关注

关注

49文章

2941浏览量

53519

发布评论请先 登录

新思科技ImperasDV解决方案让RISC-V处理器验证效率翻倍

Banana Pi BPI-CM6 计算模块将 8 核 RISC-V 处理器带入 CM4 外形尺寸

直播预约 |开源芯片系列讲座第30期:“一生一芯”计划——从零开始设计自己的RISC-V处理器芯片

为什么RISC-V是嵌入式应用的最佳选择

基于E203 RISC-V的音频信号处理系统 -协处理器的乘累加过程

提高RISC-V在Drystone测试中得分的方法

PIC64GX1000 RISC-V MPU:一款面向嵌入式计算的高性能64位多核处理器

明晚开播 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

直播预约 |开源芯片系列讲座第28期:高性能RISC-V微处理器芯片

RISC-V和ARM有何区别?

RISC-V向量处理器:现代计算的革命性引擎

RISC-V向量处理器:现代计算的革命性引擎

评论