与通过源漏嵌入 SiC 应变材料来提高NMOS 的速度类似,通过源漏嵌入SiGe 应变材料可以提高PMOS的速度。源漏嵌入 SiGe 应变技术被广泛用于提高90nm 及以下工艺制程PMOS的速度。它是通过外延生长技术在源漏嵌入SiGe 应变材料,利用锗和硅晶格常数不同,从而对衬底硅产生应力,改变硅价带的能带结构,降低空穴的电导有效质量。

硅的晶格常数是5.431A,锗的晶格常数是5.653A,硅与锗的不匹配率是4.09%,从而使得 SiGe 的晶格常数大于纯硅。图2-10 所示为在硅衬底上外延生长 SiGe 应变材料外延。SiGe 应变材料会对横向的沟道产生压应力,从而使沟道的晶格发生形变,晶格变小。

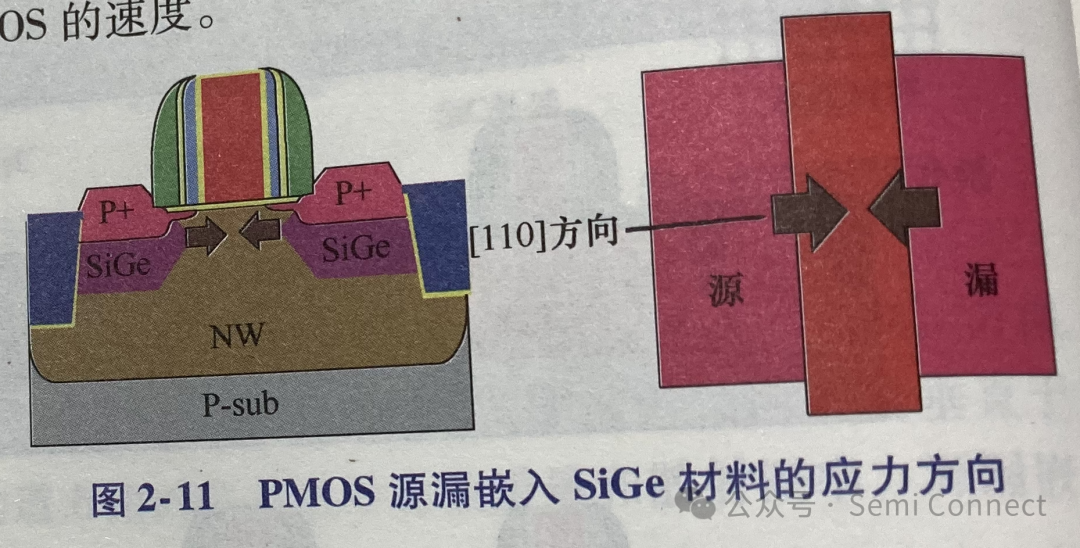

在 PMOS的源漏嵌入SiGe 应变材料,如图2-11所示,PMOS 的沟道制造在[110]方向上,SiGe 应变材料会在该方向产生单轴的压应力,该压应力可以使价带能带发生分裂,重空穴带离开价带顶,轻空六带占据价带顶,从而减小沟道方向的空穴的电导有效质量,最终源漏嵌入 SiGe 应变材料可以有效地提高 PMOS 的速度。

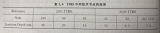

源漏嵌入 SiGe 应变材料也是利用选择性外延技术生长的。源漏嵌入 SiGe 应变材料的工艺的硅源有SiCl4,SiHCl3,SiH2Cl3和SiH4,锗源有GeH4,硅源中的氯原子(或者HCI)可以提高原子的活性,氯原子的数目越多,选择性越好,这是因为氯可以抑制Si在气相中和掩膜层表面成核。锗含量是 SiGe 应变材料外延工艺的一个重要参数,锗的含量越高,应力越大。但是,锗含量过高容易造成位错,反而降低了应力的效果。

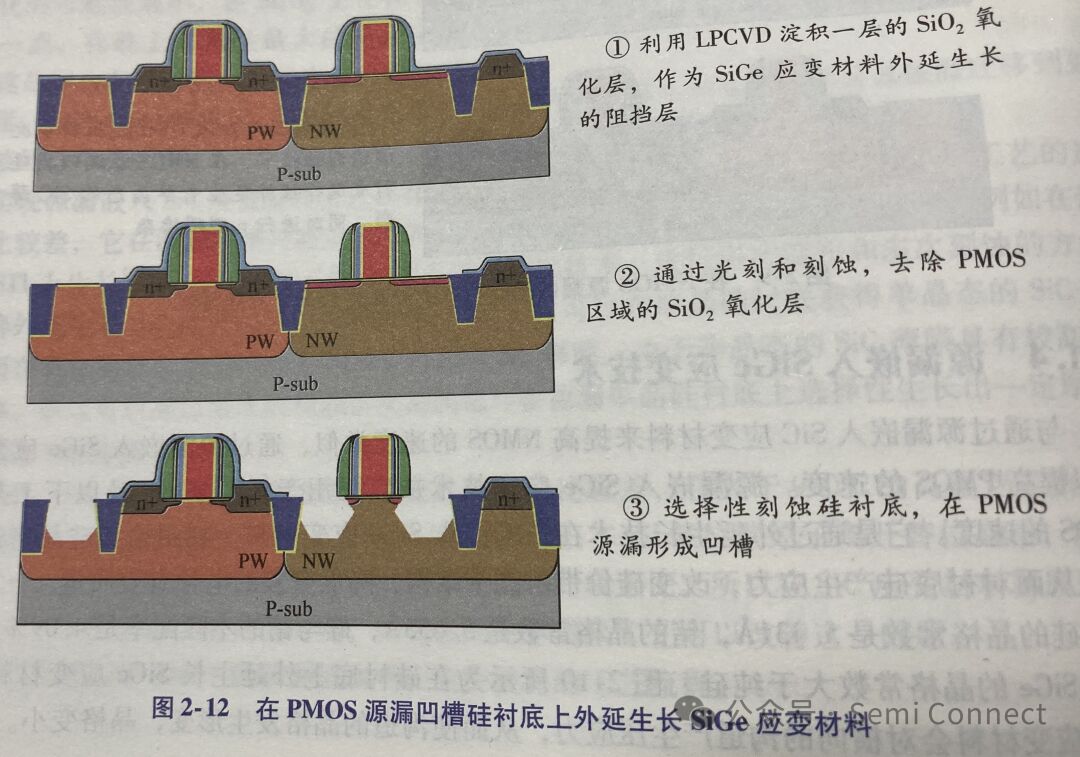

图2-12所示为PMOS 的源漏嵌入 SiGe应变材料的工艺流程。

-

SiGe

+关注

关注

0文章

99浏览量

24666 -

PMOS

+关注

关注

4文章

274浏览量

31724 -

晶格

+关注

关注

0文章

97浏览量

9653

原文标题:源漏嵌入 SiGe 应变技术

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

金属电阻应变片工作原理简介

基于分布式光纤应变传感器技术的山体滑坡在线监测预警方案

漏源电压VDS相关资料下载

漏源电压振荡严重

SiGe技术提高无线前端性能

PNP与NPN哪个是“源”与”漏“的浑水

嵌入式源漏选择性外延(Embedded Source and Drain Selective Epitaxy)

mos芯片源极漏极栅极在哪 mos管怎么判断漏栅源极

SiGe外延工艺及其在外延生长、应变硅应用及GAA结构中的作用

源漏扩展结构概述

源漏嵌入SiGe应变技术简介

源漏嵌入SiGe应变技术简介

评论