引言

器件和系统时钟通常以固定频率运行,这可能会导致在时钟频率处产生电磁干扰,进而引发串扰并耦合至邻近信号路径。扩频时钟(SSC)技术通过对信号进行频率调制,使设备能够降低辐射。调制会将载波能量分散至更宽的频率范围,从而降低峰值功率。因此,监管当前高速串行数据标准(如 PCI Express 和 Serial ATA)的相关组织要求设备必须支持 SSC 功能,以确保符合规范。由于 SSC 涉及随时间变化的频率偏移,其调制特性的验证和调试历来较为复杂。通过使用SSCTrack函数,示波器能够解调串行数据信号的扩频调制,并以频率随时间变化的同步时域图形显示从载波中分离出的SSC调制波形。

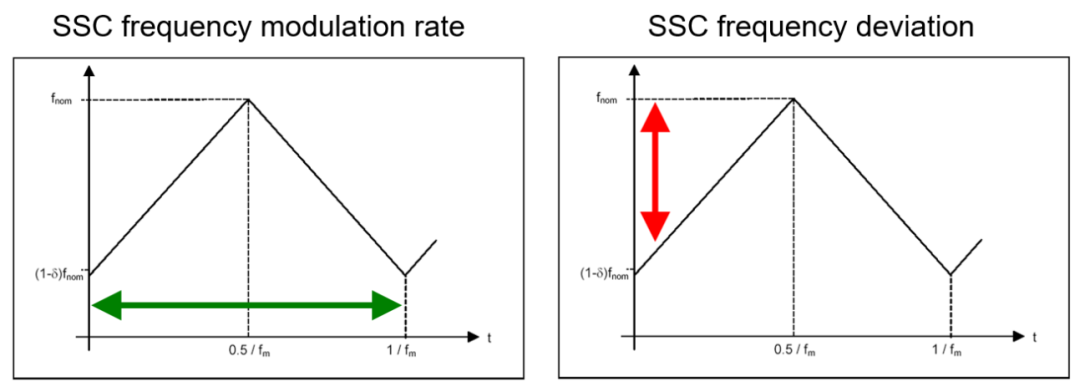

SSC频率调制率与SSC频率偏移的定义

SSC频率调制率(或SSC频率)通常设定在30至33 kHz的固定频率范围内,并施加于高速串行数据的时钟信号上。例如,16 Gbps的串行数据信号可能具有31 kHz的SSC调制频率。该低频SSC调制用于避免音频带解调,并最大限度地减少系统时序偏差。

SSC频率偏移是指相对于标称高速串行数据速率的向下展频,表示SSC频率变化的幅度,即高速串行数据标称速率的降低量。

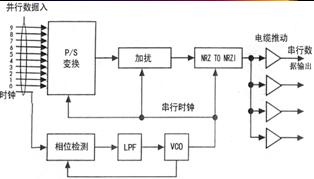

图1:SSC频率调制率与SSC频率偏移

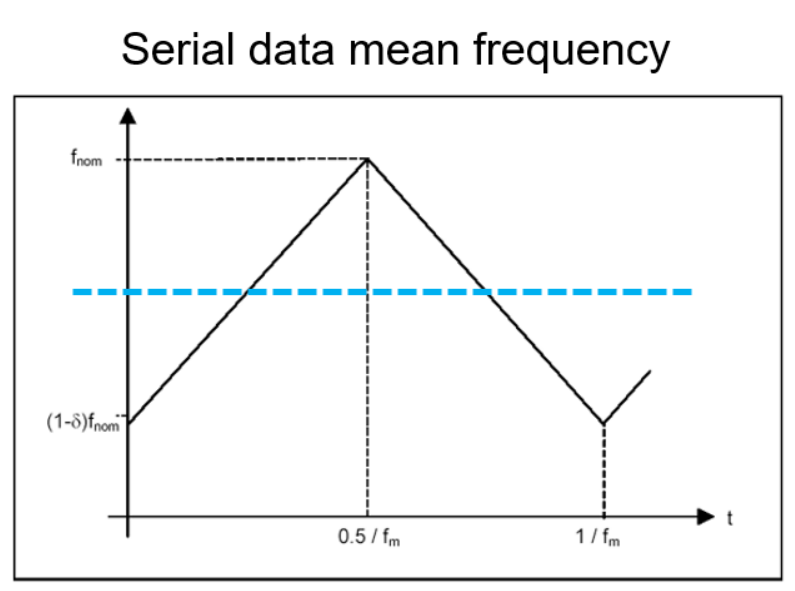

步骤1:计算串行数据平均频率

串行数据平均频率等于串行数据标称频率减去SSC频率偏移的一半。

例如,对于PCI Express 4.0串行数据信号,其比特率为16 Gbps,采用三角波SSC,调制频率为31 kHz,频率偏移范围为0 ppm至-4.8 kppm。

比特率为16E+9(串行数据标称频率),下展频频率偏移为4800E-6,计算得(16E+9)×(4800E-6) = 76.8E6,即76.8 MHz的频率偏移。

因此,平均频率为标称频率减去频率偏移的一半,即16 GHz – (0.5 × 76.8 MHz) = 15.9616 GHz。

图2:串行数据平均频率等于串行数据标称频率减去SSC频率偏移的一半

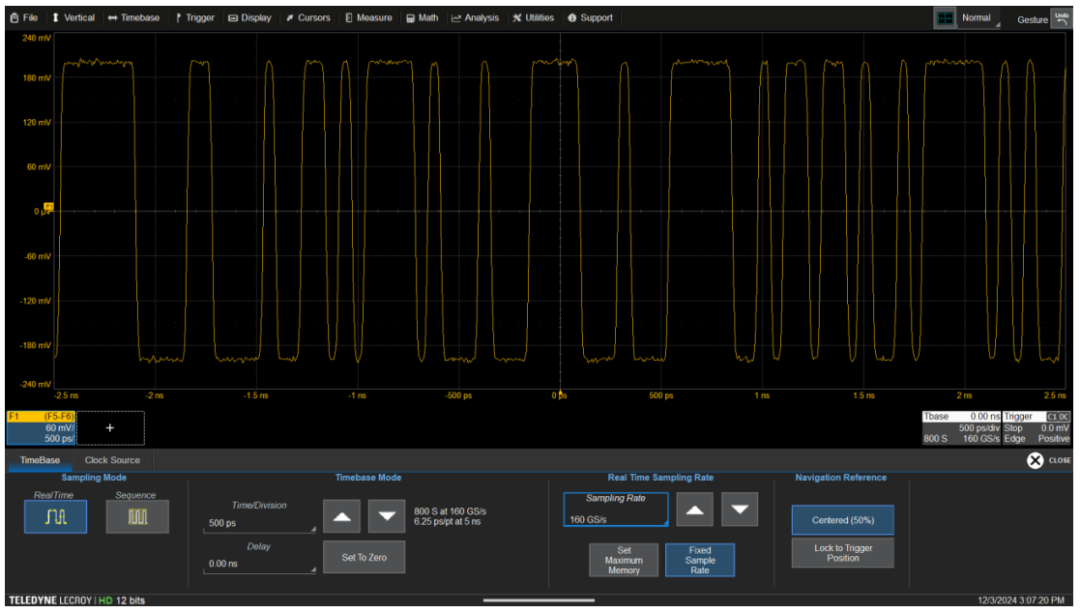

步骤 2:采集串行数据信号波形

采集信号时,确保采用最佳采样率和垂直刻度(V/div)设置。例如,对于16 Gbps的串行数据信号,应使用160 GS/s的采样率。将输入通道的垂直刻度调整至波形垂直方向占满大部分网格,以最大化动态范围。对于使用线缆采集的差分信号,应分别调整每个单端输入的垂直刻度,使其垂直方向占满大部分网格,同时调整差分波形的垂直刻度,使其同样占满大部分网格。

如图3所示,输入信号为400 mV幅度、16 Gbps的PRBS 23波形,带有31 kHz的SSC调制,向下扩频至-4.8kppm。示波器采样率为160 GS/s,垂直刻度设为55 mV/div,波形在垂直方向上占满大部分网格。

图3:采集的信号为带有31 kHz SSC调制、向下扩频-4.8kppm的16 Gbps差分波形

步骤3:应用绝对值函数

使用运算函数,将绝对值函数应用于差分串行数据信号波形,将绝对值函数的向下脉冲缩放,使其在垂直方向上填满大部分网格,如图4所示。

图4:差分波形的绝对值应显示为向下脉冲

步骤4:配置SSCTrack运算函数

使用运算函数,将SSCTrack应用于绝对值函数。

将平均频率设置为步骤1中计算的值。

LPF通带宽度、LPF转换宽度及带宽均设置为2 MHz。建议采用750倍抽取和20 MHz/格的时间刻度。

将示波器时间基准设置为至少20微秒/格,并重新采集波形。SSC调制轮廓应如图5所示。

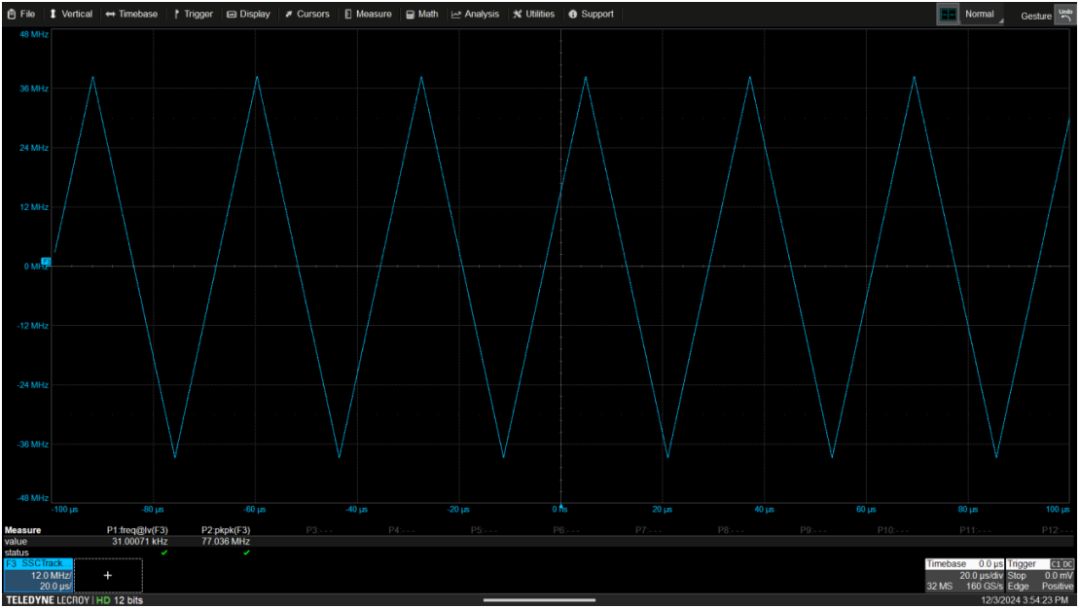

图5:SSCTrack运算符显示扩频调制轮廓

SSC 验证示例:

如图6所示,可直接对 SSCTrack 波形进行测量。通过对 SSCTrack 应用频率和峰峰值测量参数,可确认 SSC 频率及频率偏移的数值。

图6:通过对 SSCTrack 的测量验证 SSC 频率和频率偏移

SSC 调试示例:

图7所示的是实际 Serial ATA 2i 信号存在显著抖动问题,以下调试步骤用于定位问题根源。该信号比特率为3.0 Gbps,采用三角波 SSC ,调制频率为31.8 kHz,频率偏移范围为0 ppm至-4.8 kppm。 比特率为3E+9,向下扩频的频率偏移为4800E-6,计算得 (3E+9)×(4800E-6) = 14.4E6,即14.4 MHz的频率偏移。因此,平均频率等于标称频率减去频率偏移的一半,即 3 GHz – (0.5 × 14.4 MHz) = 2.9928 GHz。

图7中的SSCTrack波形显示出异常的阶梯状SSC调制轮廓。对波形进行解调并绘制频率-时间曲线后发现,SSC调制轮廓并非平滑的三角形,而是出现了意外的锯齿状且不规则的SSC调制形态。本例中,抖动问题是由被测设备内数字编码器固件错误引起,我们通过SSCTrack迅速定位了根本原因。

图7:SSCTrack发现数字编码器故障

结论:

通过将SSCTrack运算函数应用于差分串行数据信号波形的绝对值,可实现SSC性能验证,生成以时间为横轴、频率为纵轴的曲线。该频率-时间调制曲线不仅可用于验证SSC调制的形状、频率及偏移,还能用于SSC调制错误的调试与根源分析。

关于我们

特励达力科(Teledyne Lecroy)是高端示波器、协议分析仪和其他测试仪器的专业制造商,可快速全面地验证电子系统的性能和合规性,并进行复杂的调试分析。

1964 年成立以来,公司一直专注于将强大的工具整合到创新产品中,以提高“洞察时间”。更快的洞察时间使用户能够快速查找和修复复杂电子系统中的缺陷,从而显著缩短产品的上市时间。

-

频率

+关注

关注

4文章

1581浏览量

61749 -

电磁干扰

+关注

关注

36文章

2465浏览量

107658 -

函数

+关注

关注

3文章

4408浏览量

66905 -

时钟信号

+关注

关注

4文章

495浏览量

29720

原文标题:使用 SSCTrack 函数解调串行数据扩频时钟信号

文章出处:【微信号:美国力科TeledyneLeCroy,微信公众号:美国力科TeledyneLeCroy】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

多片AFE5818的输入ADC时钟为同步时钟,不同的芯片上LVDS串行数据时钟和帧时钟是否是同步的?

DAC8801信号输出波形会随着串行数据线上的信号变化而变化,为什么?

【proteus练一练】串行数据转换为并行数据

扩频系统如何设计调频解调模块

基于74HC595的串行数码管显示实验

SPC57S-Eval套件板上的哪个引脚用于串行时钟和串行数据吗

串行数字视频信号传输系统-SDI接口

测量串行数据信号:选择合适的示波器带宽

使用SSCTrack函数解调串行数据扩频时钟信号

使用SSCTrack函数解调串行数据扩频时钟信号

评论