一、直接模拟频率合成技术

一般是以高稳定度参考源比如晶振所产生的频率信号作为基准,经过必要的的加减乘除运算(对不同信号混频可以看作对相应频率的加减运算,倍频和分频看作乘除运算)得到需要的新的频率,由于这样产生的频率是一系列离散的值,可以通过滤波器和开关的选择性提取出我们需要的指定输出频率,最后通过放大滤波电路输出。直接模拟频率合成技术属于发展的早期阶段,它的特点是较高分辨率和稳定度,跳变频时间短,但是也有因对电路设计的高要求而产生的成本尺寸问题。

二、直接数字频率合成技术

基本思路

它首先是将波形的关键信息按已知逻辑置于芯片的集成寄存器中,通过控制信号可以有逻辑地读取相应的波形信息,再经过数模变换和滤波放大等内部集成的电路结构就可以合成我们想要的信号。

对于 DDS 的整个原理过程进行分析可知,将幅值相位等波形信息进行存储时,从模拟到数字的过程避免不了数字量化误差,这是导致相位失真和幅度失真的主要原因,其次,DDS 方案还存在杂散较大且不能消除、相位累加器截断误差、正弦查找表有限字长和时钟信号泄漏等问题。它从波形信息单独存储提取的角度出发,可以产生任意需要的波形和需要的初始相位,这种设计的灵活性也让它可以在更广阔的场景中发挥作用。

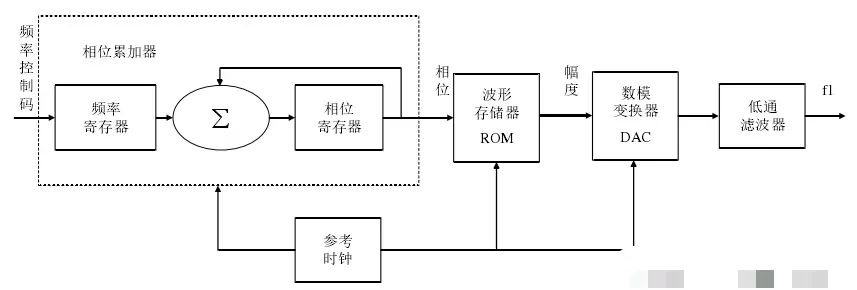

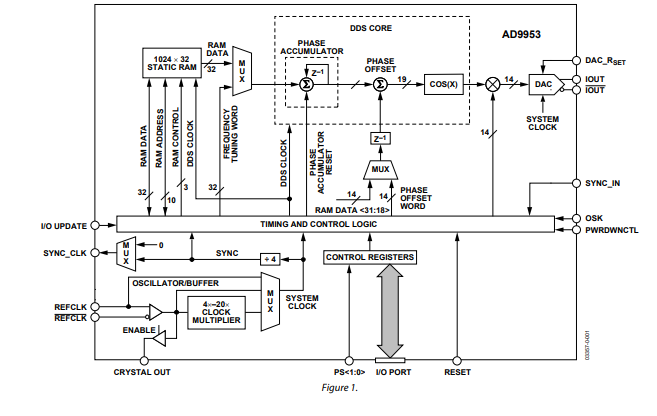

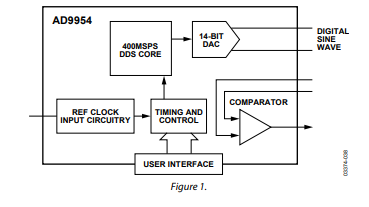

DDS 的基本原理框图如上图所示,从中看出,基本工作原理是逻辑控制产生的频率码控制累加器的一系列相位步进并且对应到相位信息,然后利用已知的存储逻辑在 ROM 中找到对应的幅度,接下来经过 DAC 模块使信号的幅度成为阶梯状信号,最终再低通滤波得到连续的正弦信号。

三、间接模拟式频率源

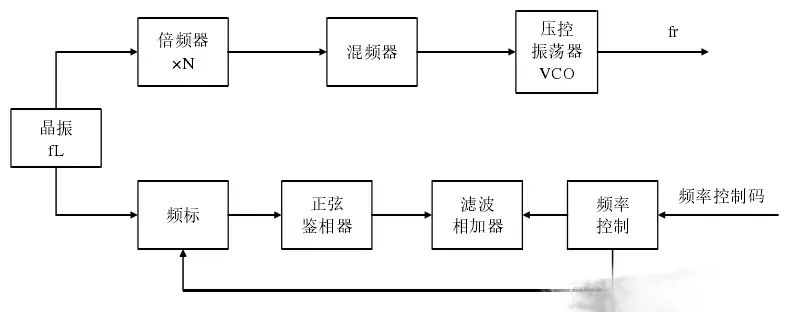

间接模拟式频率源的核心是模拟锁相环,它的频率响应时间比直接式的短得多,因为锁相环等器件都有时延,另一方面,也是锁相环类似于窄带滤波的特性会让此方案的杂散较好,而架构中的正弦鉴相器也会有效提升相噪指数。它的原理框图如下图,但也会有电路结构复杂等限制它应用的缺陷。

该类频率源方案的架构中,晶振产生一个Lf 的基准频率,一路经过倍频后与压控振荡器的输出信号进行上变频操作,实现压控振荡器输出信号向高频段的频谱搬移,另一路则是以初始晶振得到的信号作为参考,在逻辑控制下与目标信号进行同频鉴相,最终让压控振荡器与晶振输出信号的相位保持一致,达到锁定状态。架构中的倍频和混频操作只是为实现高频 VCO 的目标,不是必要模块。

四、间接数字式频率源

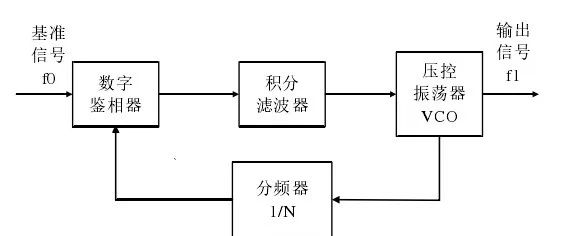

它的核心是数字锁相环,电路结构方面加入了数字分频器。特点是是频率分辨

率高,易于集成等,因此通信系统中发挥着重要的作用,主要缺陷是相位噪声差。

间接数字式频率综合器的结构如上图所示,从中可以看到,先对压控振荡器的输出频率被进行N分频,再经过反馈回路与用于参考的基准频率比较相位和频率等信息,二者之间的差异直接影响误差电压信号使 VCO 频率重新锁定到目标频率的信号输出。

五、锁相环频率合成技术

锁相环合成技术核心是相位控制机制的锁相环,之前已经有了一定介绍。具体而言分为整数分频和小数分频频率合成技术,其中常用的小数分频频率合成技术又分为脉冲移除技术和双模分频技术。

整数分频频率合成技术是在锁相环的反馈回路中增加了一个分频器,工作机制区别不大,由于分频器的作用使输出信号 fo与输入信号 fi 频率不再相等,而是变为固定比值 N,即: fo=N⋅fi。

利用锁相环路可以快速调节重新锁定的特点,目前应用广泛的是程序控制 N 来实现锁相环输出信号 fo 在压控振荡器的输出范围内扫频输出。

整数分频技术设计的系统能够输出的最精细频率步进就是鉴相频率 fi ,因此对同一输出频率,提高其频率分辨率只有增大分频比 N,但这样也会使锁相环系统的相位噪声恶化,相比较而言小数分频技术可以在保持内部鉴相频率不变的前提下有效提升输出信号的频率分辨率性能,在高分辨率频率源的设计中更为适用。小数分频中脉冲移除技术是在整数分频的电路结构基础上又在锁相环反馈环路加入一个脉冲移除器,它可以按照特定的周期移除信号中的脉冲,脉冲移除技术进一步发展形成了双模分频技术。

六、混合频率合成技术

上述几种单一类型的频率合成技术方案都有自己比较明显的优缺点,所以目前频率合成方案都会将直接和间接,数字和模拟,锁相环频率合成等多种频率合成技术结合起来,尽可能保留各自的优势,避免较为明显的缺陷,综合形成混合频率合成技术方案。

这样可以实现单种频率合成技术达不到的综合性能指标。现今混合频率合成方案已经发展地较为完善,这里主要讨论一下多环锁相,DDS 激励锁相环,PLL 和DDS 环内和环外混频这四种。

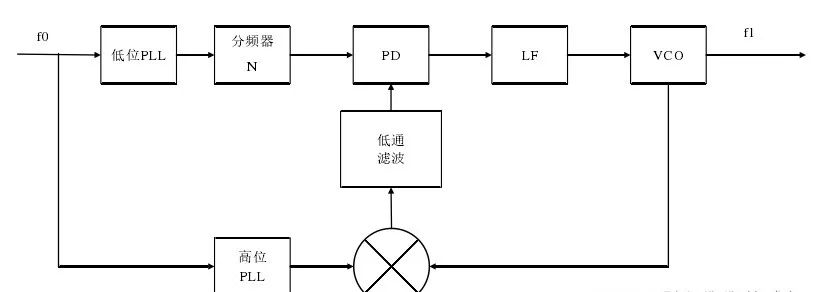

多环锁相结构相比于单环在频率分辨率方面有明显的提升,如下图所示:

输入信号频率为 f0 ,分两路,一路经过低位锁相环再经过分频器 N ,输出频率变为 N1f0/N ,相应频率分辨率为 fo/N ,另一路经过高位锁相环,输出频率变为 N2f0,相应频率分辨率为 f0 ,这两路的输出信号再由锁相环路实现相加输出信号 f1,总体的频率分辨率为 f0/N ,即: f1=(N2+N1/N)⋅f0。

综合来看,为了实现高频率分辨率的目标,此种方案也会存在由于电路复杂导致的相位噪声和谐波恶化的问题。

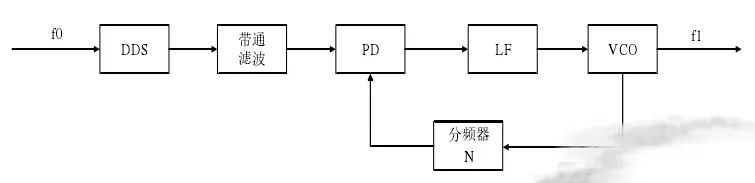

DDS 激励锁相环的系统框架如下图:

系统的总体输出信号频率表示为式: f1=N⋅fDDS=N⋅MK⋅f0

其中直接数字频率合成中的频率控制字表示为 K ,相位累加器字长表示为 M ,此方案有效结合了两种技术的优势,在宽带高分辨率应用方面有重要的作用。

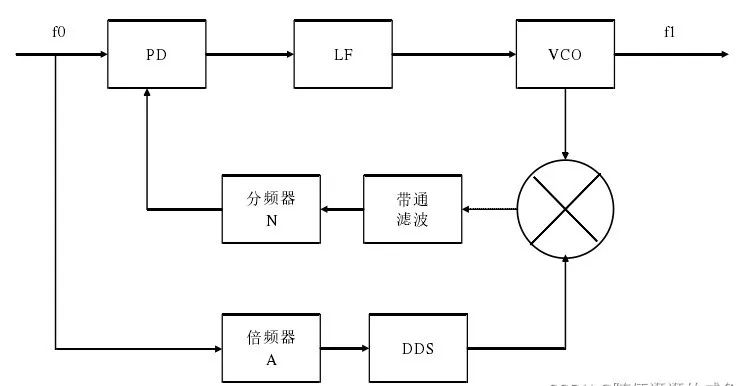

PLL 与 DDS 环内混频的原理框图如下图所示:

结构方面,是将 DDS 引入基本的锁相环路内,输出频率描述为: f1=A⋅fDDS+N⋅f0=(A⋅MK+N)⋅f0

此方案可以优化输出信号的相位噪声参数并且改善杂散带来的干扰(PLL 窄带滤波特性),但是带宽较窄并且滤波难度较大。

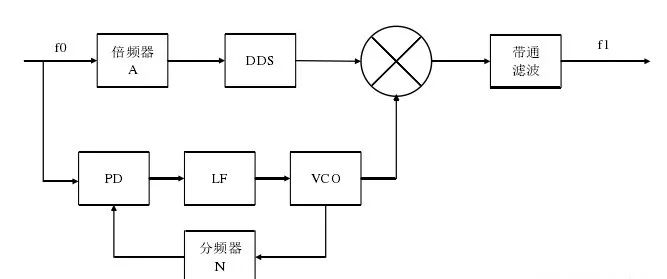

PLL 与 DDS 环外混频的原理框图如下图:

结构方面,核心是 DDS 输出频率和 PLL 输出频率在外部混频,频率分辨率为:(A/M)f0 ,输出频率表示为式:f1=A⋅fDDS±N⋅f0=(A⋅MK±N)⋅f0

此系统方案可以有效提升频率分辨率,调频速度和频率输出范围的性能,但是和环内混频一样会有杂散和滤波难度方面的问题。

原文链接:https://2048.csdn.net/6825b01ca5baf817cf4c613b.html

-

锁相环

+关注

关注

36文章

637浏览量

91302 -

滤波器

+关注

关注

162文章

8471浏览量

186288 -

晶振

+关注

关注

35文章

3638浏览量

73821 -

频率合成

+关注

关注

1文章

33浏览量

22333

原文标题:常见的频率合成方案汇总

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

微波宽带频率合成器ADF5612的技术解析与应用探讨

ADF4351宽带合成器:特性、应用与电路设计详解

ADF4350宽带合成器:高性能频率合成的理想之选

ADF4169:13.5 GHz 分数 N 频率合成器的技术剖析与应用

ADF4159:一款13 GHz分数N频率合成器的详细解析

高性能6GHz小数N频率合成器ADF4157的技术剖析与应用

155.52 MHz频率合成器AD809:技术特性与应用指南

深度解析DS1085 EconOscillator频率合成器

LMX2531:高性能频率合成器的深度解析与应用指南

AD9953 400 MSPS、14位DAC、1.8 V CMOS直接数字频率合成器技术手册

AD9951 400 MSPS、14位DAC、1.8 V CMOS直接数字频率合成器技术手册

AD9954 400MSPS、14位、1.8V CMOS、直接数字频率合成器技术手册

一文详解频率合成技术

一文详解频率合成技术

评论