概述

MAX9174/MAX9175是670MHz低抖动、低扭曲的1:2分配器,尤其适合于保护切换、环回、时钟和数据分配。这些器件具有1.0ps~(RMS)~ (最大)的超低随机抖动,保证在那些定时误差极为敏感的高速链路中可靠工作。

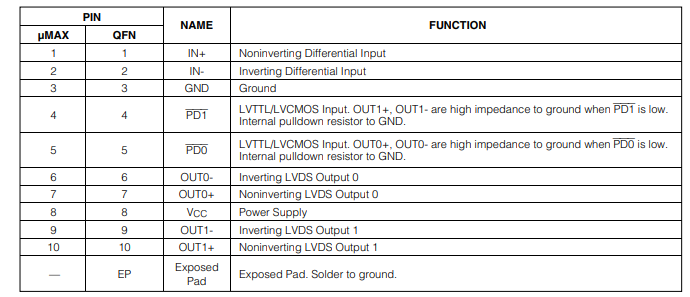

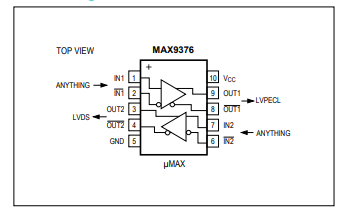

MAX9714具有安全失效的LVDS输入和LVDS输出。MAX9175接收任何差分输入(CML/LVDS/LVPECL),提供LVDS输出。控制掉电输入,可以将输出置为高阻。当输入处于开路、无驱动短路或无驱动终端匹配时,MAX9174的安全失效电路驱动输出为高电平。MAX9175具有偏置电路,在输入开路时驱动高电平输出。掉电输入兼容于标准的LVTTL/LVCMOS逻辑,并且掉电输入可以承受-1V的下冲和VCC + 1V的过冲。MAX9174/MAX9175提供10引脚µMAX和10引脚、底盘裸露的薄型QFN封装,工作于+3.3V单电源,工作温度范围-40°C至+85°C。

数据表:*附件:MAX9174 MAX9175 670MHz、LVDS至LVDS和任意逻辑至LVDS 1比2分配器.pdf

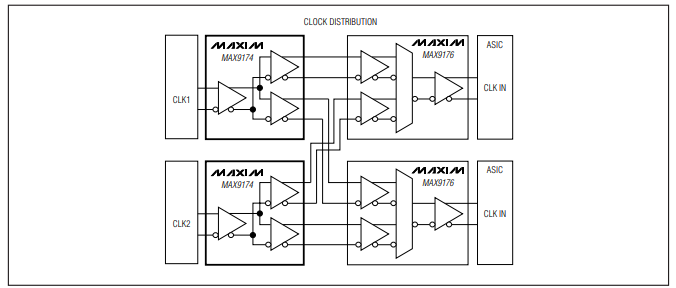

应用

- 时钟分配

- 环回

- 保护开关

特性

- 670MHz时,最大1.0ps

(RMS)抖动 - 800Mbps数据速率时,最大80ps

(P-P)抖动 - +3.3V工作电源

- LVDS安全失效输入(MAX9174)

- 任意输入电平(MAX9175)包括差分CML/LVDS/LVPECL

- 断电时,输入能够承受-1.0V至V

CC+ 1.0V的电压 - 低功耗CMOS设计

- 10引脚µMAX和薄型QFN封装

- -40°C至+85°C的工作温度范围

- 符合ANSI TIA/EIA-644 LVDS标准

- IEC 61000-4-2第4级ESD保护

应用电路

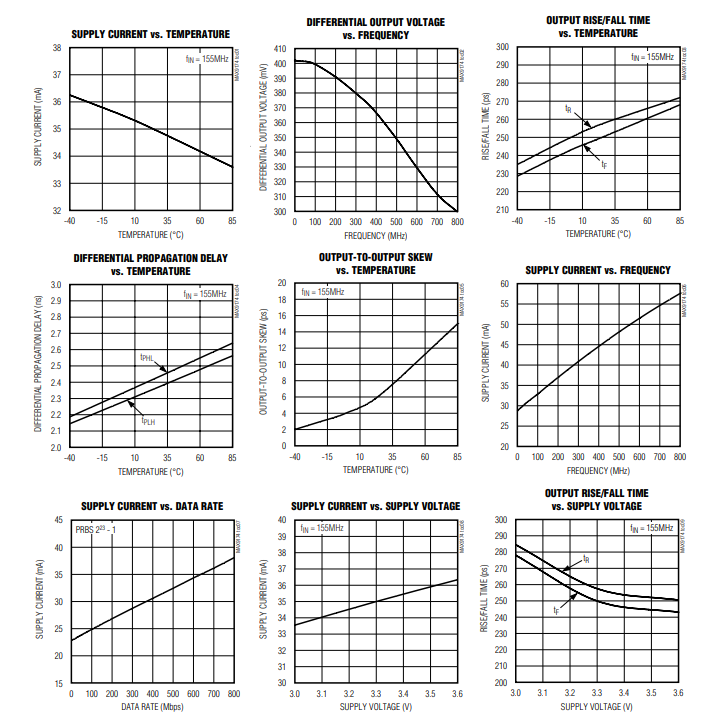

典型操作特性

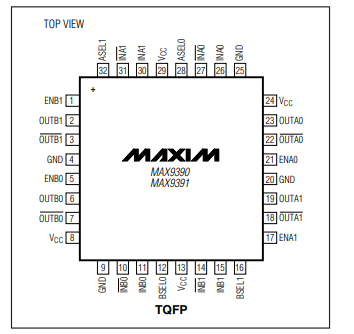

引脚配置描述

应用信息

电源去耦

绕过 Vcc 引脚,通过在尽可能靠近器件的位置并联安装 0.1μF 和 0.001μF 的高频表面贴装陶瓷电容器,将较小值的电容器连接到 Vcc。

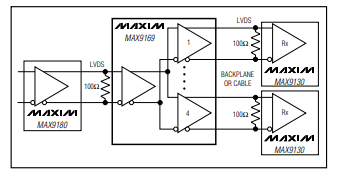

差分走线

输入和输出走线会影响 MAX9174/MAX9175 的性能。使用受控阻抗差分走线(100Ω 类型)。为减少辐射噪声并确保信号耦合对称,将差分输入和输出信号布置在同一层中。通过匹配两条信号线的电气长度来减少偏移,过度的偏移会导致磁场抵消的降低。在差分走线之间保持恒定距离,以避免差分阻抗的不连续性。尽量减少过孔的数量,以进一步防止阻抗不连续性。

电缆和连接器

LVDS(低压差分信号)互连通常具有 100Ω 的受控差分阻抗。使用具有匹配差分阻抗的电缆和连接器,以最大限度地减少阻抗不连续性。避免使用非平衡电缆,如带状电缆或简单的同轴电缆。平衡电缆,如双绞线,信号质量更好,并且往往产生较少的电磁干扰,因为它们的磁场相互抵消。平衡电缆拾取噪声作为共模信号,会被 LVDS 接收器拒绝。

端接

MAX9174/MAX9175 需要外部输入和输出端接电阻,用于 LVDS,在每个差分对中连接一个

-

时钟

+关注

关注

11文章

1999浏览量

135228 -

lvds

+关注

关注

2文章

1241浏览量

70215 -

分配器

+关注

关注

0文章

216浏览量

27429

发布评论请先 登录

MAX9234,MAX9236,MAX9238热插拔、21位、直流平衡、LVDS解串器

MAX9376,pdf datasheet (LVDS/An

DS90LV110AT 1至10 LVDS数据/时钟分配器数据表

DS90LV110T 1至10 LVDS数据/时钟分配器数据表

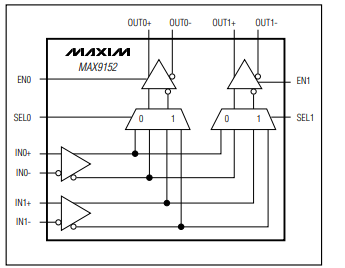

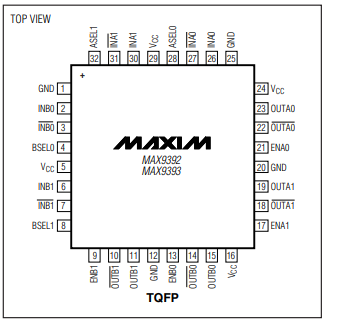

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉点开关技术手册

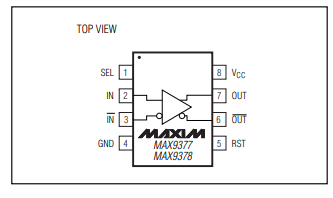

MAX9377/MAX9378任意逻辑至LVPECL/LVDS转换器,引脚可设置四分频电路技术手册

MAX9374/MAX9374A差分LVPECL至LVDS变换器技术手册

MAX9174/MAX9175 670MHz、LVDS至LVDS和任意逻辑至LVDS 1:2分配器中文手册

MAX9174/MAX9175 670MHz、LVDS至LVDS和任意逻辑至LVDS 1:2分配器中文手册

评论