在本文中,我们不涉及关于EMC的设计建议。然而,在组件水平上,所使用的技术所固有的“锁存”现象是唯一考虑的因素。

CMOS结构封装括一个PNPN可控硅类型单元,由VDD和VSS之间的寄生晶体管产生。当寄生可控硅被扰动激活,导致了µC的电源短路,并导致内部结构的破坏时,就会出现一种延迟现象。以下的条件可能会导致“锁存”:

ü输入/输出电压的电压高于VDD或低于VSS的电压。

ü电源电压VDD比VDDMax高

ü电源VDD急剧变化。

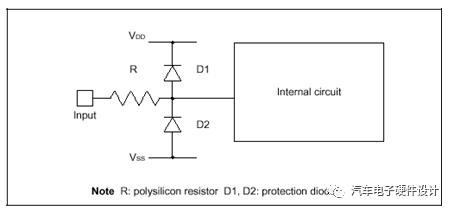

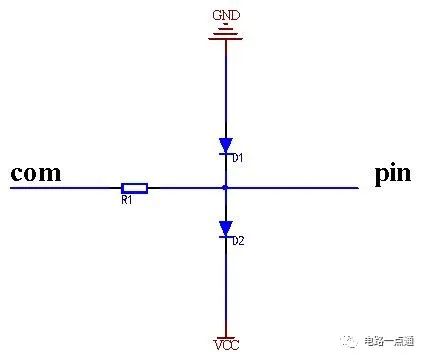

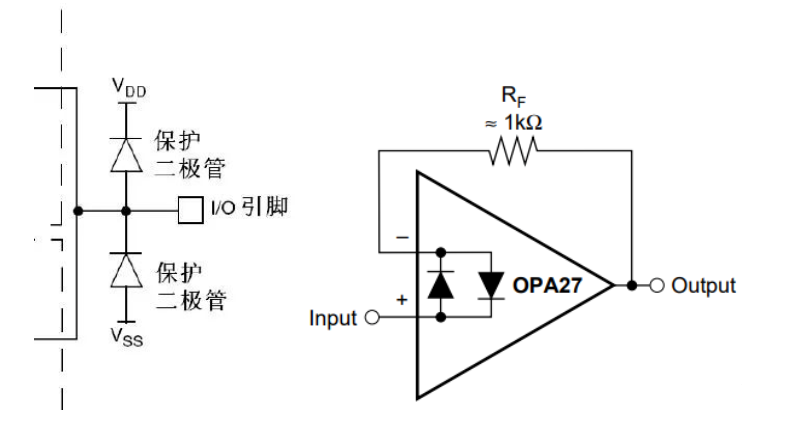

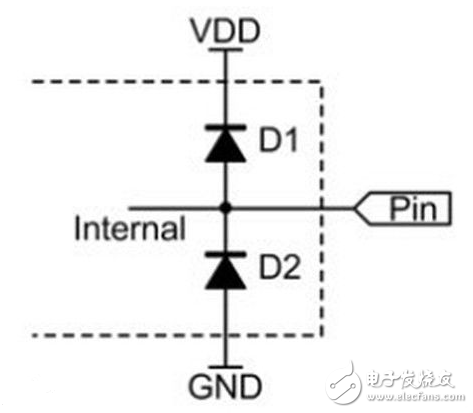

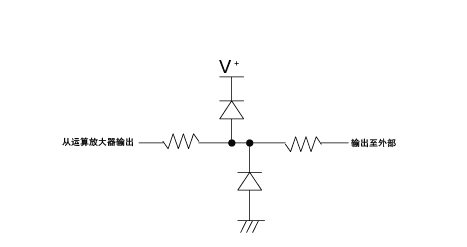

µC有对静电保护,输入是在内部配置保护网络,通过对VDD和VSS并联钳位二极管和串联电阻进行保护。

然而,这种内部保护电路必须在设计层面上的预防措施来完成。建议:

ü保持µC在其额定范围内的电源电压。

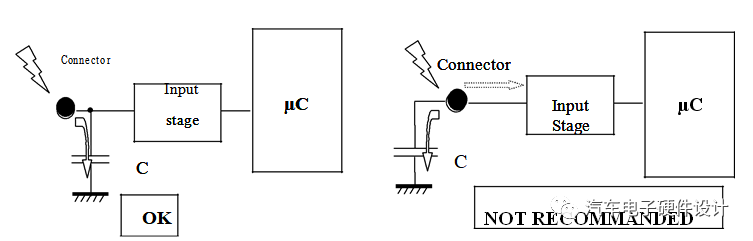

ü在连接器的引脚上直接放置一个静电电容,以得到保护。

-

CMOS

+关注

关注

58文章

6191浏览量

241616 -

二极管

+关注

关注

149文章

10316浏览量

176599 -

emc

+关注

关注

174文章

4325浏览量

190411

原文标题:MCU健壮性设计之EMC / ESD的要求

文章出处:【微信号:QCDZYJ,微信公众号:汽车电子工程知识体系】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

二极管钳位保护电路讲解

钳位二极管保护电路图 TVS钳位二极管保护原理详解

VDD和VSS并联钳位二极管和串联电阻进行保护

VDD和VSS并联钳位二极管和串联电阻进行保护

评论