刘晓昱 陈燕 李建强 乔彦彬 马强 单书珊张海峰 唐晓柯

(北京智芯微电子科技有限公司国家电网公司电力芯片设计分析重点实验室 北京市电力高可靠性集成电路设计工程技术研究中心)

摘要:

高密度封装技术在近些年迅猛发展,同时也给失效分析过程带来新的挑战。常规的失效分析手段难以满足结构复杂、线宽微小的高密度封装分析需求,需要针对具体分析对象对分析手法进行调整和改进。介绍了X射线、计算机辅助层析成像(CT)技术、微探针和多方法联用等失效分析技术,分析了其原理和适用于高密度封装的优势。并结合两个高密度封装失效分析案例,具体介绍了其在案例中的使用阶段和应用方法,成功找到失效原因。最后总结了各方法在高密度封装失效分析中应用的优势、不足和适用范围。

0引言

20世纪80年代以来高密度微电子组装技术迅速发展,大大提高了器件级IC封装和板级电路组装的密度[1-3]。近年来,以球栅阵列(ball grid array,BGA)封装、小外形外壳封装(small outline package,SOP)、芯片级封装(chip scale package,CSP)、3D等封装技术为代表的高密度封装快速发展[4-5]。相对于扁平式封装(quad flat package,QFP)等传统封装技术,高密度封装有着巨大优势,例如:1.27mm间距的BGA在25mm边长的面积上可容纳350个输入/输出(I/O)端口,远高于传统封装;CSP封装的焊球节距小于1mm,有利于缩小整个芯片体积[6-8]。然而,随着封装特征尺寸逐渐减小,对其可靠性有着更高要求,高密度布线的金属迁移短路、微铜柱凸点失效及BGA锡球焊接等新问题也随之出现[9]。

失效分析在集成电路产业中发挥着重要作用,一般根据失效模式和现象,通过无损、有损实验分析验证,挖掘失效机理[10-11]。传统失效分析方法包括:外部目检、X射线检查、超声扫描检查、电学测试、开封检查等。由于高密度封装具有线宽尺寸小、封装密度高、结构复杂等特点,传统的失效分析方法很容易产生无法探测失效点、破坏失效点等问题[12-13]。本文介绍了4种应用于高密度封装的失效分析检测技术和方法,并结合案例详述其分析过程。

1高密度封装失效分析关键技术和方法

1.1X射线检测技术

X射线检测是一种重要的无损检测技术。X射线在穿透物体不同部位时,由于材料、厚度不同,会在不同路径上产生不同衰减,进而通过探测衰减程度而呈现物体内部特征图像[14-15]。

目前主流的X射线成像技术采用实时成像检验系统,主要特点是同时具有高分辨率和大动态范围。另外,随着微焦点检测等技术的应用,X射线检测精度日益提高,例如,YXLON公司生产的Y.CougarSMT型X射线检测仪精度可达1μm,使其在高密度封装产品检测中发挥重要作用。

1.2CT检测技术

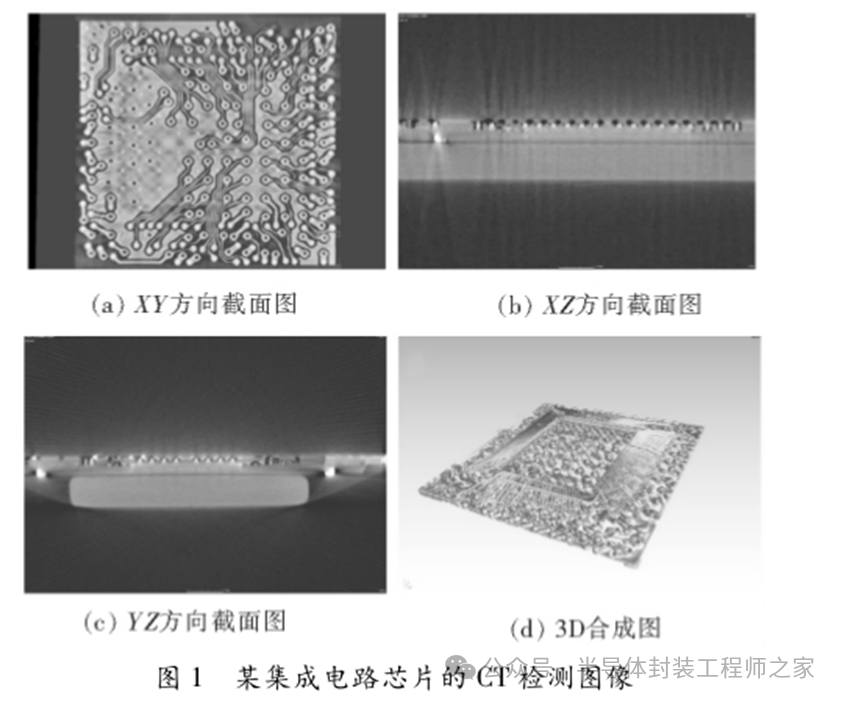

计算机辅助层析成像技术(computedtomography,CT)是X射线成像技术的延伸,通过采集待测物件不同角度的X射线投影信息,利用高性能计算机计算生成断层图像和三维(3D)图像[16]。其中断层扫描成像可以对待测样品在XY,YZ,XZ三个方向上选取任意截面进行成像,而不显示其余无关部分,避免成像干扰。3D成像是利用计算机对选择性过滤后的结构或材料进行3D重构,有利于分析高密度封装中的复杂结构。图1为某集成电路芯片的CT检测图,其中图1(a)~(c)分别为二维(2D)某层截面图,图1(d)为3D合成图。

1.3X射线二维成像与CT技术联用

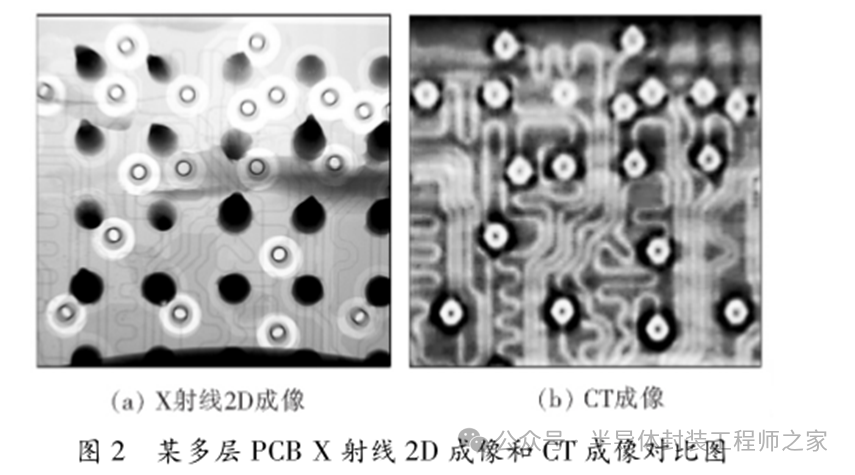

X射线在样品内部沿直线传播,具有成像准确、分辨率高的优点,然而对于结构复杂的器件,多层结构的投影会发生叠加;壳体较厚的陶瓷或金属封装电子元器件还会使细节特征衬度降低,影响分析结果[17]。CT技术成像是由计算机计算重建得来,其分辨率略低于X射线直接投影成像,尤其是在大倍数观察时,成像质量低于X射线2D成像,如图2所示,图2(a)为某器件的多层印刷电路板(PCB)X射线2D放大成像图,可见图中金属线轮廓清晰,分辨率较高,但BGA焊球(图中黑色圆形阵列)等无关元素也同时被拍摄,图2(b)为相同部位的CT断层成像图,过滤掉BGA焊球等无关成分,但分辨率较低。另外,3D成像还受到滤窗的人工调整、计算误差、采集干扰等因素影响。联合使用X射线2D成像、CT断层成像和CT3D成像技术,利用三者的优势,对器件的不同部位采用不同分析手段,相同部位利用多种分析方法从不同角度进行检查,可以极大地提高分析准确性。

1.4研磨制样技术、X射线、FIB和探针台联用

研磨制样技术是将样品镶嵌到树脂中,经过一系列研磨过程,得到样品真实截面形貌的技术,属于有损分析,在元器件失效分析中具有重要作用。聚焦离子束(FIB)设备可以使用高能离子对样品表面原子进行剥离,以进行微纳加工。探针台是晶圆测试领域的重要设备,探针可分为软针和硬针,软针针尖直径为0.2~1μm,硬针针尖直径多为5μm到几百微米;探针座在X,Y,Z三个方向上的线性移动精度可以小于1μm,探针台具有灵活性高、精度高、信号稳定等优点[18]。

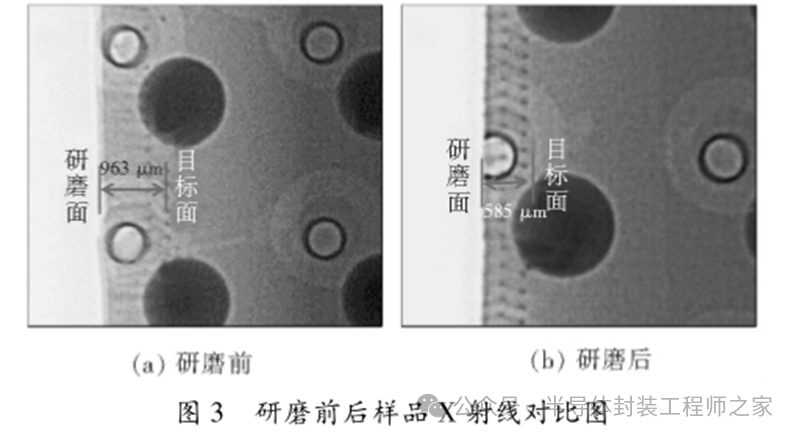

在高密度封装中,金属线宽减小,部分缺陷的尺寸也随之降低,甚至只有几十微米,这就要求在研磨制样时做到高精度,并严格控制研磨速度,稍小的失误都有可能造成研磨过量。这时可以在研磨的过程中使用X射线观测,测量研磨一定时间前后两次观察时的研磨长度,以计算该研磨条件下的研磨速度;同时利用X射线测量研磨面至缺陷的剩余距离,结合研磨速度实现精准研磨控制。使用特定的研磨条件对某高密度封装失效样品进行30s研磨,研磨前后进行X射线照射得到对比图,如图3所示,经测量研磨面距目标位置的距离分别为963和585μm,则研磨距离为378μm,该条件下研磨速度为12.6μm/s,则在该条件下再研磨46s左右可至目标位置。

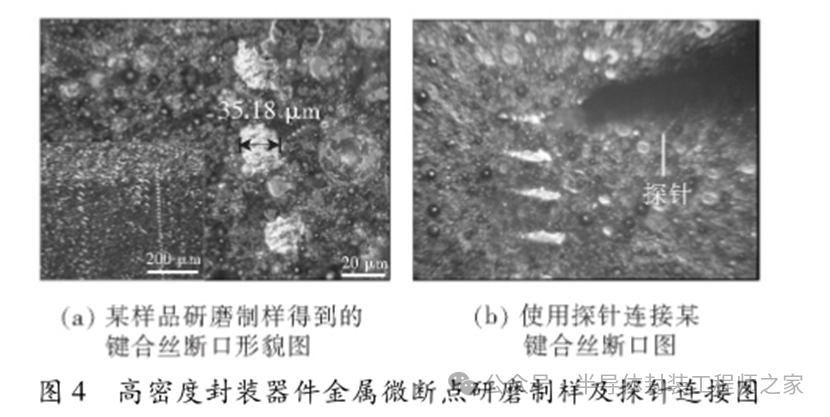

在研磨至观测面时,若缺陷尺寸远小于金属线宽,则研磨造成的金属延展的影响不可忽视,这时可以使用FIB设备去除表面延展金属,露出底层金属的真实形貌。若研磨得到某电路中间的微断点,需进行部分电路的电学测试,则可使用探针台建立精准稳定的电学连接。例如:研磨制样得到的某键合丝断口(图4(a))直径约为35μm,常规的电学连接针无法精准连接,而探针台的探针硬针针尖直径可达5μm,并且通过精准定位实现稳定连接,如图4(b)所示。

2失效分析在高密度封装失效案例中的应用

2.1CPU失效分析

某批次进口CPU产品发生功能失效,失效率为10-3。该芯片为BGA封装,共1000多个芯片管脚,868个封装管脚,Cu键合丝,基板采用4层FR4印刷电路板。进口商不提供芯片管脚和封装管脚的对应关系。

将封装输入/输出管脚依次对地管脚进行正反向I-V测试。发现其中7个输入/输出管脚的I-V曲线异常,表现为同一管脚在多次测试中会随机出现开路和正常两种情况,测试时对芯片的按压力度影响两种曲线出现的概率,按压力度大时多表现为正常,按压力度小时多表现为开路,初步判断器件内部存在虚接。

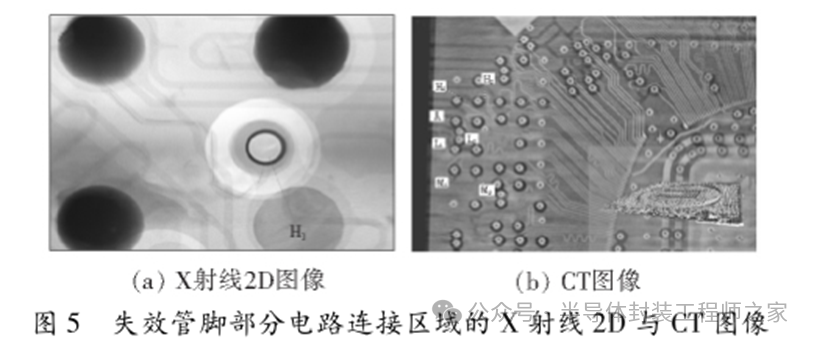

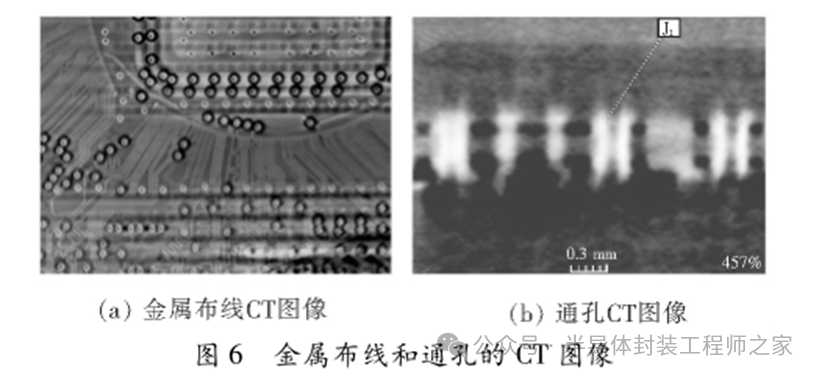

利用X射线2D成像、CT断层成像和CT3D成像技术共同对失效件进行检查分析。首先,利用CT获取平行于芯片表面的断层图像,逐层分析,部分金属线宽过小区域结合X射线2D图像,确定封装管脚、金属引线框架、键合丝、芯片管脚的连接对应关系,以便进行后续有损电学检测分析,如图5所示,图中H1,H2,J1,L1,L2,M1,M2为失效管脚名称,图5(b)中插图为3D图像。

其次,利用CT在平行于芯片方向和垂直于芯片方向的断面图上分别检查金属布线和通孔有无异常,如图6所示。经初步检查,失效管脚对应的封装金属布线均无开路、短路的明显异常。推断失效点可能位于键合丝第一键合点或第二键合点。

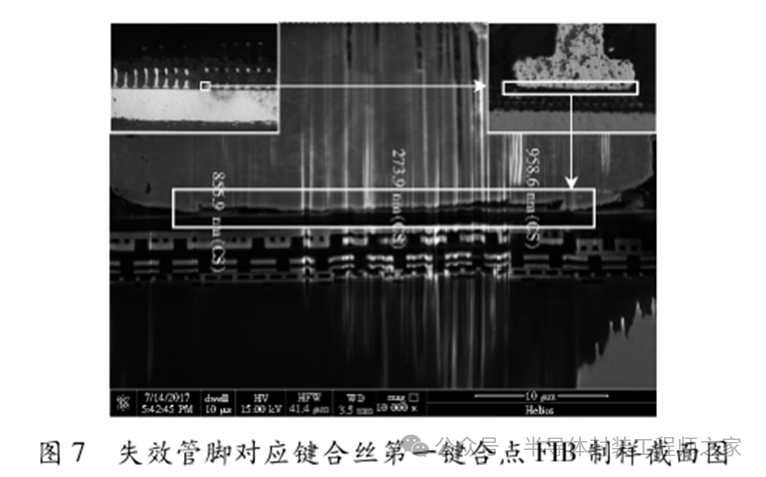

对失效点进行由外侧向内侧的纵向研磨制样,第二键合点未见异常,第一键合点存在异常。得到第一键合点失效的截面后,为消除研磨过程中的金属延展影响,对截面采用FIB切去表面层,露出深层截面的原始形貌,如图7所示,插图均为截面金相显微图。结果发现,失效管脚的Cu键合丝和Al管脚之间存在缝隙,缝隙的最大宽度为959nm,最小宽度为274nm。该缝隙是造成开路虚接失效的原因。

2.2BGA封装ARM芯片失效分析

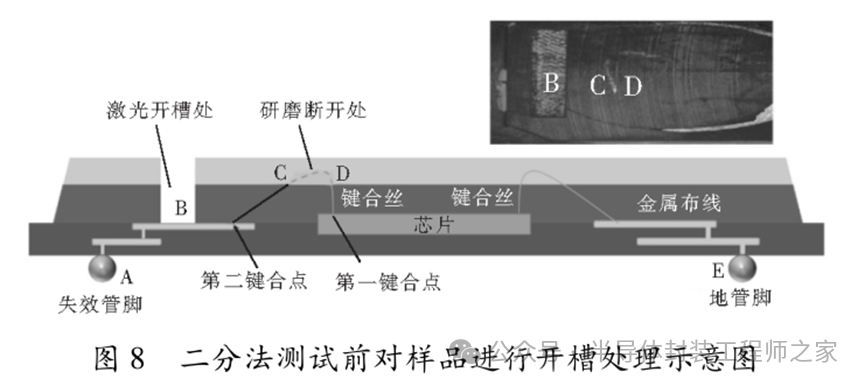

某进口BGA封装ARM芯片在使用时出现功能异常,失效率约为6×10-4,芯片为Cu键合。解焊芯片后,首先将失效芯片和参考芯片的功能管脚对地管脚进行I-V测试。发现异常管脚I-V曲线与参考件不同,曲线正、负向电流均减小,怀疑由某处电阻增大造成。芯片进行X射线和CT检查均未见异常,但由于失效现象并非开路失效,X射线检测精度有可能无法满足要求,故采用二分法进行电学定位,同样利用X射线和CT技术联用确定封装内部连接关系。

由于其他封装管脚对相同地端管脚测试表现为正常曲线,故异常点出现在失效管脚-金属布线-键合丝-芯片的区域。如图8所示(插图为样品研磨后B,C,D区域图像),图中A点为失效管脚,B点为激光开槽露出的金属引线框架,C点为键合丝研磨的第一断口,D点为键合丝研磨的第二断口,E点为地管脚。首先,对键合丝和失效管脚之间的金属引线框架区域进行激光开槽,露出金属引线框架。利用探针台测试B点和失效管脚之间的电阻,显示无异常,而B点至地管脚的I-V曲线为异常。之后,从样品上表面沿平行于样品表面的方向向下研磨,磨断键合丝中部,不破坏其余部分,漏出C和D两点。利用探针台连接断点,进行电学测试发现:A和C之间电阻无异常,D和地管脚之间测试为I-V异常。表明异常点处于失效管脚对应键合丝的第一键合点处,排除第二键合点异常。

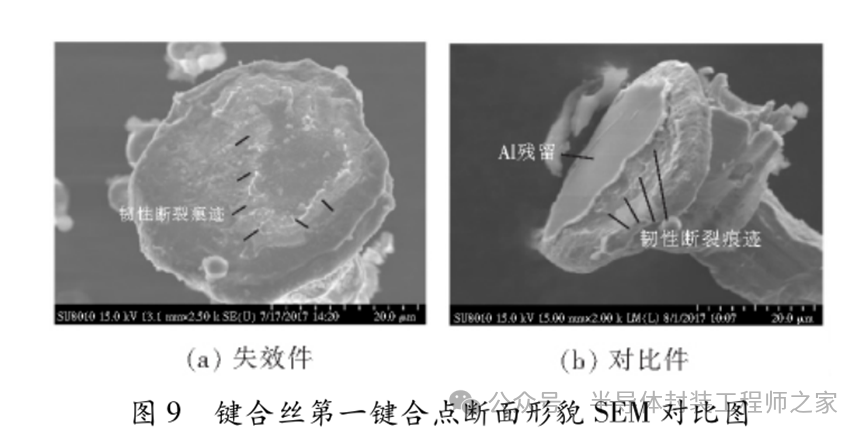

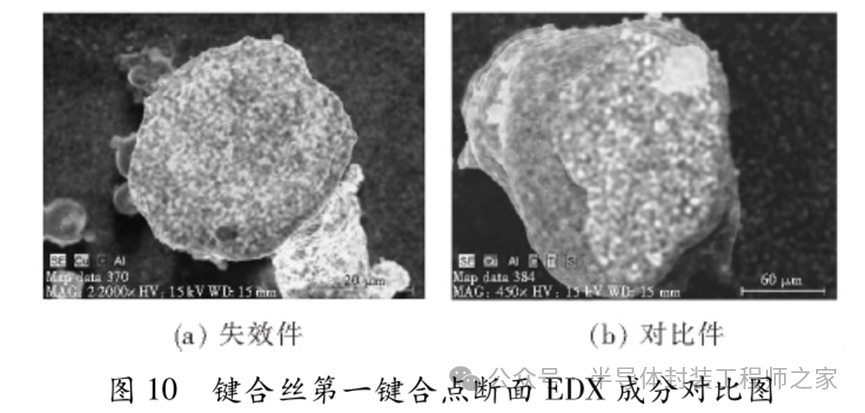

对芯片进行正面开封,首先使用激光进行初步开封,然后使用弱冷酸进行开封,最大限度地保留Cu键合完整。将键合丝拔下,键合丝在其和Al管脚结合处断开,得到断口,使用相同办法得到对比器件的键合丝第一键合点断口。使用扫描电子显微镜(SEM)对两个器件的第一键合点典型断口进行形貌观察和对比分析,结果如图9所示,使用SEM设备的能量色散X射线光谱仪(EDX)进行断口成分分析,结果如图10所示。

结合图9和图10可以发现,失效样品键合丝典型断口区域形貌和元素特征为:断口大面积区域为Cu,少部分区域显示为两种结合金属脱离的韧性断裂形貌,并且有Al残留。对比件典型断口处有大面积Al管脚脱离残留以及阻挡层钛,未有脱离Al管脚残留的其余部分均显示为两种结合金属脱离的韧性断裂形貌,并且有Al成分残留。对比检测实验表明,失效件第一键合点Cu键合丝和Al管脚之间没有形成良好的金属间化合物,导致接触电阻增大,进而导致失效。

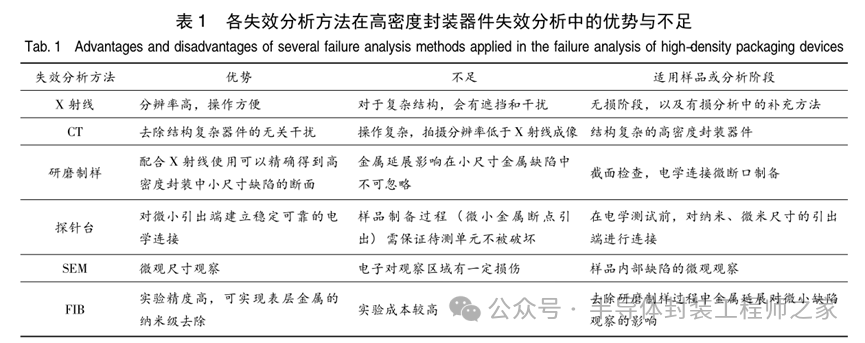

各种失效分析方法在高密度封装器件失效分析中均有自身的优势与不足,详见表1,并且在一定情况下应不单纯遵循传统的方法,可以根据样品特点进行创新,或将多种方法联合使用。

3结论

按常规方法使用传统的失效分析手段对高密度封装器件进行分析,会遇到结构复杂、线宽尺寸过小等困难,这时应对传统的失效分析手段进行创新,或者将多种分析方法进行联合使用,例如本文提到的键合丝断口电学连接测试、X射线测量辅助的高精度研磨方法等,通过实例展示了创新方法在高密度封装器件失效分析中的应用效果,给出了传统失效分析方法在高密度封装器件失效分析中的优势与不足。

微电子封装技术是微电子制造技术的延伸,随着集成电路器件的小型化发展,分立封装向系统级封装演变,高密度封装技术必将持续推进。常规失效分析技术仍需要不断改进或创新,以解决更高密度封装的失效问题。

-

芯片

+关注

关注

462文章

53530浏览量

458834 -

集成电路

+关注

关注

5446文章

12464浏览量

372606 -

封装

+关注

关注

128文章

9139浏览量

147861 -

失效分析

+关注

关注

18文章

244浏览量

67548

原文标题:适用于高密度封装的失效分析技术及其应用

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

探讨高密度小间距LED屏工艺

高速高密度PCB设计的关键技术问题是什么?

DC/DC转换器的高密度印刷电路板(PCB)布局

指导分享高密度光纤配线架安装方法

高密度Interposer封装设计的SI分析

高密度封装失效分析关键技术和方法

高密度封装失效分析关键技术和方法

评论