随机变化需要新方法、新工具,以及不同公司之间的合作。

极紫外(EUV)光刻技术正在接近生产,但是随机性变化——又称为随机效应正在重新浮出水面,并为这项期待已久的技术带来了更多的挑战。

GlobalFoundries、英特尔、三星和台积电希望将EUV光刻技术加入到7nm和5nm生产中。但就像以前一样,EUV由几部分组件组成,在芯片制造商能够引入之前,它们必须整合在一起。包括光刻机、光源、光刻胶和掩膜。最近,行业已经开始发布关于量子随机效应的警报,这种现象会引起光刻图案随机变化。

有些组件已经准备就绪,而有些则发展缓慢。事实上,EUV团队首次将光刻胶及其相关问题列为EUV的最大挑战,超过了电源。经过多年的推迟,EUV光源功率终于满足了大批量生产(HVM)的要求。

光刻胶是用来制作图案的光敏聚合物,它是造成随机性效应的罪魁祸首之一。根据定义,随机效应描述了具有光量子随机变化的事件。它们是不可预测的,没有稳定的模式。

在EUV的情况下,光子击中光刻胶并引起光化学反应。但是对于EUV光刻胶而言,由于量子非定域效应,每个或多个反应期间可能出现新的不同的反应。因此EUV容易发生涉及随机效应。一般来说,该行业将随机性主要归咎于光刻胶,但EUV的光掩膜和其他部分(EUV光子平均自由程较大)也可能会出现随机变量。

随机效应并不新鲜。事实上,这一现象多年来一直困扰着EUV团队。众所周知,随机效应会导致光刻图案的变化。行业一直在努力解决这个问题,但人们要么低估了问题,要么没能及时解决问题,要么两者兼而有之。

新情况是,行业终于迎来了另一个问题。一颗先进的逻辑芯片集成了十亿个甚至更多的微小通孔。 如果EUV光刻过程中出现问题,芯片可能会遭受由于随机效应引发的失效或缺陷(通孔缺失contact missing)。换言之,一颗芯片可能会因为一个触点通孔的缺陷而失效。

这可能是一厢情愿的想法,但芯片制造商相信他们可以躲避7nm工艺节点潜在的由随机性引发的缺陷。事实上,EUV可能出现在7nm工艺节点。但在5nm甚至是7nm工艺节点的情况下,芯片制造商可能无法避免这些和其他问题,除非行业出现一些新的突破。GlobalFoundries高级研究员兼高级技术研究总监Harry Levinson表示:“公平地讲,我们的行业非常乐观地看待我们向EUV光刻前进的方向。我们正准备将第一代引入到大批量生产中,展望第二代EUV光刻技术,抵抗随机效应绝对是最重要的问题之一。”

无论节点如何,EUV随机效应都为芯片制造商、晶圆厂工具供应商和IC设计团体带来了麻烦。西门子公司DFM项目总监David Abercrombie表示:“从设计的角度来看,随机效应确实是随机的,因为你无法预测变化的位置和数量。因此,没有系统的方法可以说一个特定的布局特征应该在这个区域还是在另一个区域中进行修改。换言之,除了避免的所有敏感特性的出现,将其转化成传统设计规则约束以外,完全没有办法在设计过程中补偿随机效应影响。”

作为回应,该行业正在采取措施解决一些问题。其中包括:

• 供应商正在改进EUV光刻胶。

• Applied Materials和ASML正在开发一种新的电子束测量工具,承诺可以检测出随机性缺陷。此外,创业公司Fractilia已经设计了一种方法来辅助测量。

• 然后,通过这些新的测量数据,芯片制造商请求有竞争力的晶圆厂工具供应商进行合作,并一起对信息进行整合。

-

光刻胶

+关注

关注

10文章

357浏览量

31870

发布评论请先 登录

Futurrex高端光刻胶

光刻胶残留要怎么解决?

Microchem SU-8光刻胶 2000系列

光刻胶在集成电路制造中的应用

光刻胶有什么分类?生产流程是什么?

光刻机工艺的原理及设备

光刻胶的原理和正负光刻胶的主要组分是什么

浅谈EUV光刻中的光刻胶和掩模等材料挑战

EUV光刻胶开发面临哪些挑战?

光刻胶黏度如何测量?光刻胶需要稀释吗?

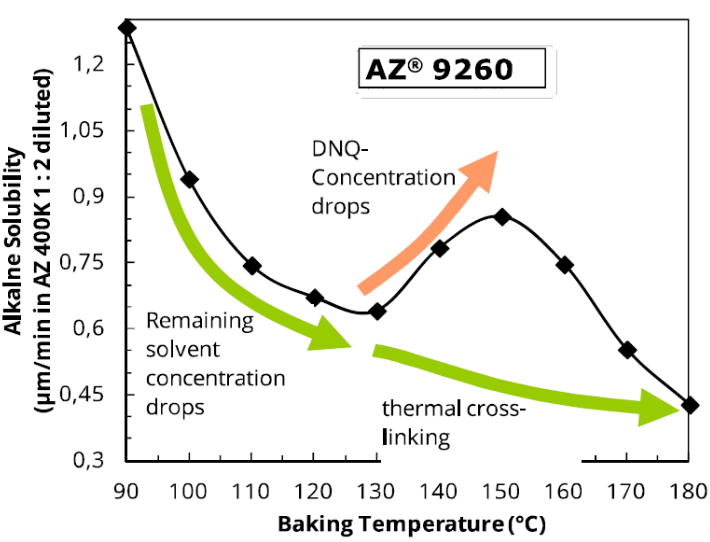

光刻胶的硬烘烤技术

极紫外(EUV)光刻新挑战,除了光刻胶还有啥?

极紫外(EUV)光刻新挑战,除了光刻胶还有啥?

评论