概述

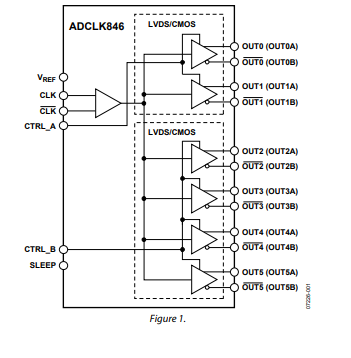

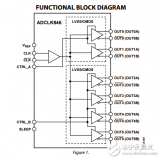

ADCLK846是一款针对低抖动和低功耗优化的1.2 GHz/250 MHz、LVDS/CMOS、扇出缓冲器。可配置范围为6 LVDS至12 CMOS输出,包括LVDS和CMOS输出的组合。两条控制线路用于确定固定模块输出是LVDS输出还是CMOS输出。

时钟输入接受各种单端和差分逻辑电平,包括LVPECL、LVDS、HSTL、CML和CMOS。

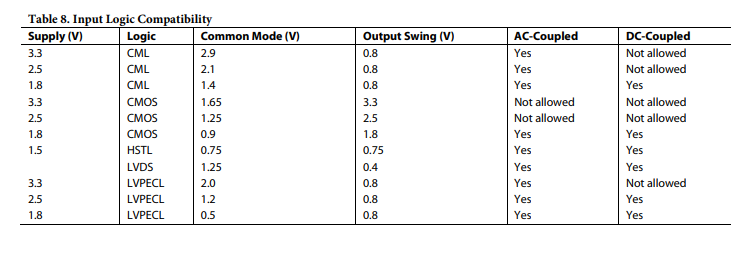

表8提供用于各类连接的接口选项。SLEEP引脚使能睡眼模式以关断器件的电源。

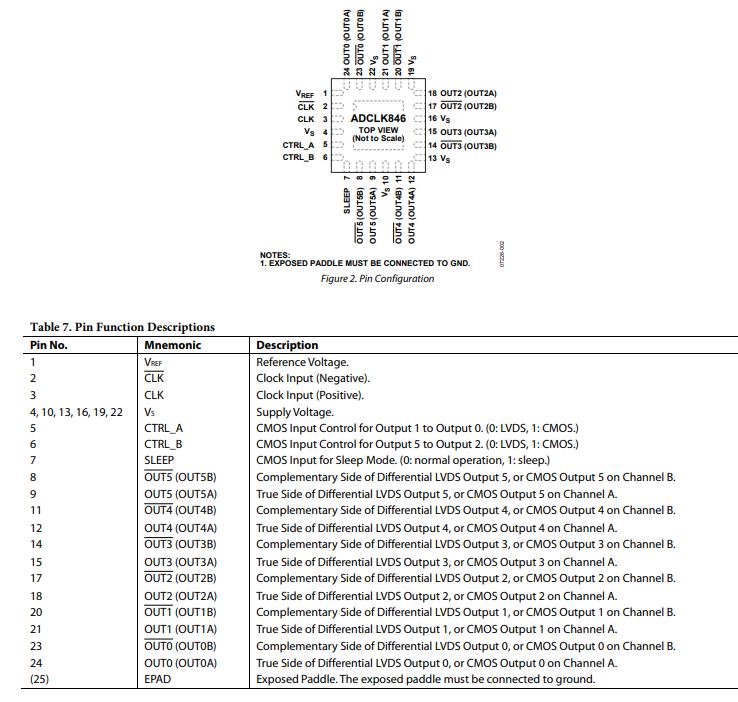

这款器件采用24引脚LFCSP封装,工作温度范围为−40℃至+85℃的标准工业温度范围。

数据表:*附件:ADCLK846 1.8 V、6 LVDS 12 CMOS输出低功耗时钟扇出缓冲器技术手册.pdf

特性

- 可选LVDS/CMOS输出

- 多达6 LVDS(1.2 GHz)或者12 CMOS(250 MHz)输出

- 每通道功耗:<16 mW(工作频率为100 MHz)

- 综合抖动:54 fs(12 kHz至20 MHz)

- 附加宽带抖动:100 fs

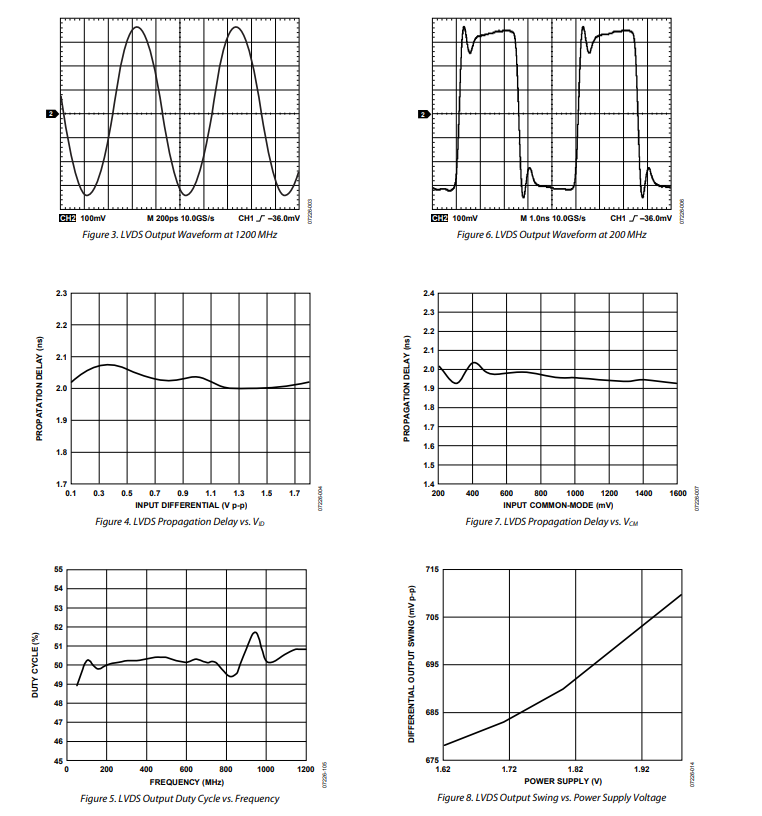

- 传播延迟:2.0 ns(LVDS)

- 输出上升/下降时间:135 ps(LVDS)

- 输出至输出偏斜:65 ps(LVDS)

- 睡眠模式

- 引脚可编程控制

- 1.8 V电源

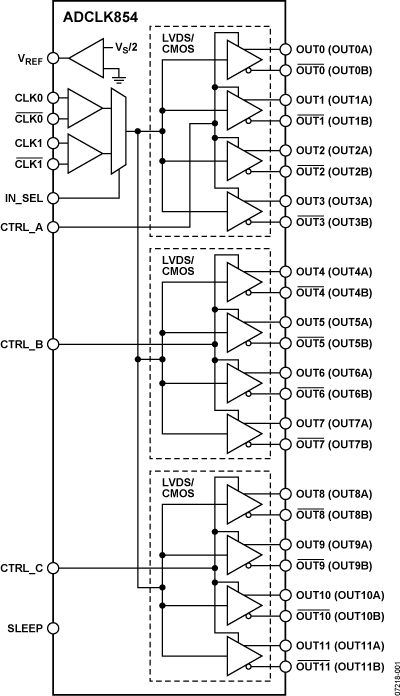

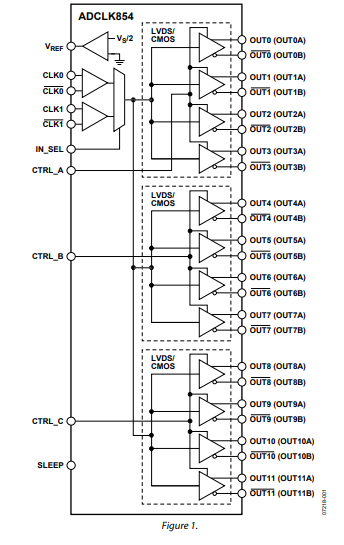

框图

引脚配置描述

典型性能特征

功能描述

ADCLK846的时钟输入会分配到所有输出通道。每个通道组可通过引脚编程设置为LVDS或CMOS电平。这允许从LVDS和CMOS逻辑的组合中选择6到12种输出配置,以及使用这两种逻辑的其他组合。

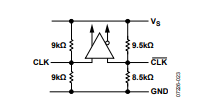

时钟输入

ADCLK846的差分输入在内部进行自偏置。时钟输入有一个电阻分压器,可设置共模电平为输入的互补信号。应将信号偏置到比真值低30 mV,以避免在输入信号停止时出现振荡。等效输入电路见图20。

输入可以是交流耦合或直流耦合。表8提供了输入逻辑兼容性的参考。如果需要单端输入,可以通过交流或直流耦合到差分输入的一侧来实现。将另一个输入通过电容旁路到地。

请注意,抖动性能会随着低输入斜率而下降,如图11所示。有关不同端接方案,请参见图28至图32。图20. ADCLK846输入级

交流耦合应用

当需要交流耦合时,ADCLK846提供两种选择。第一种选择不需要外部组件(不包括隔直电容);它允许用户将参考信号耦合到时钟输入引脚(见图31)。

第二种选择允许使用**V_{REF}**引脚为ADCLK846设置直流偏置电平。V_{REF}引脚可以通过电阻连接到CLK和overline{CLK}。这种方法允许在ADCLK846处对信号进行较低阻抗的端接(见图32)。

内部偏置电阻仍与外部偏置电阻并联。相对较高的内部电阻使得外部到**V_{REF}**的端接起主导作用。当不希望稍微偏移输入时,这也很有用。如前所述,提到的仅指内部偏置。

时钟输出

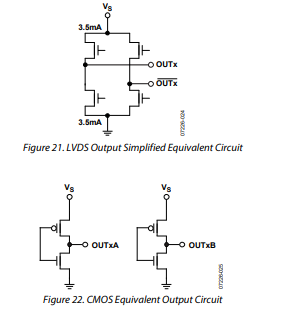

每个驱动器由一个差分LVDS输出或两个单端CMOS输出组成(始终同相)。当LVDS驱动器启用时,相应的CMOS驱动器处于三态。当CMOS驱动器启用时,相应的LVDS驱动器断电并处于三态。图21和图22展示了等效输出级。

控制和功能引脚

CTRL_A逻辑选择

CTRL_A为输出1和输出0选择CMOS(高电平)或LVDS(低电平)逻辑。此引脚有一个内部200 kΩ下拉电阻。

CTRL_B逻辑选择

CTRL_B为输出5、输出4、输出3和输出2选择CMOS(高电平)或LVDS(低电平)逻辑。此引脚有一个内部200 kΩ下拉电阻。

睡眠模式

SLEEP使芯片除带隙基准外的部分断电。该输入为高电平时,会使输出进入高阻态。此引脚有一个200 kΩ下拉电阻。控制引脚在睡眠模式下仍可操作。

电源

ADCLK846的**V_{S}**需要1.8 V ± 5%的电源。最佳实践建议在印刷电路板(PCB)上用足够的电容(>10 μF)对电源进行旁路,并在尽可能靠近器件的位置用足够的电容(0.1 μF)对所有电源引脚进行旁路。ADCLK846评估板(ADCLK846/PCBZ)的布局提供了一个良好的布局示例。

外露金属焊盘

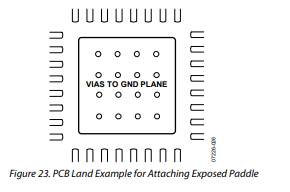

ADCLK846封装上的外露金属焊盘用于电气连接,同时也增强散热。为使器件正常工作,该焊盘必须正确连接到地(GND)。ADCLK846通过其外露焊盘散热。PCB充当ADCLK846的散热器。PCB连接必须为热量从顶层向下传导到接地层等更大散热区域提供良好的热路径。这需要一个由过孔组成的栅格。图23给出了一个示例。

-

CMOS

+关注

关注

58文章

6241浏览量

243474 -

缓冲器

+关注

关注

6文章

2236浏览量

49062 -

时钟

+关注

关注

11文章

2000浏览量

135311 -

lvds

+关注

关注

2文章

1244浏览量

70270

发布评论请先 登录

请问ADCLK846未用的LVDS一般如何处理?

ADCLK846/PCBZ,ADCLK954高性能时钟扇出缓冲器评估板

ADCLK846,pdf datasheet (Low Po

1.8伏6LVDS/12 CMOS输出低功耗时钟扇出缓冲器adclk846数据表

1.8V,12-lvds/24-cmos输出低功耗时钟扇出缓冲器adclk854数据表

ADCLK846 1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器

ADCLK854 1.8 V、12 LVDS/24 CMOS输出的低功耗时钟扇出缓冲器

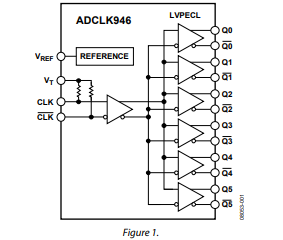

ADCLK946采用SiGe工艺的6 LVPECL输出时钟扇出缓冲器技术手册

ADCLK846 1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器技术手册

ADCLK846 1.8 V、6 LVDS/12 CMOS输出低功耗时钟扇出缓冲器技术手册

评论