概述

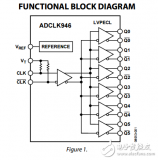

ADCLK946是一款采用ADI公司专有的XFCB3硅锗(SiGe)双极性工艺制造的超快型时钟扇出缓冲器。这款器件设计用于要求低抖动性能的高速应用。

这款器件具有一个带中心抽头、差分、100 Ω片上端接电阻的差分输入。支持直流耦合LVPECL、CML和3.3 V CMOS(单端)和交流耦合1.8 V CMOS、LVDS和LVPECL输入。VREF引脚可用来为交流耦合输入提供偏置。

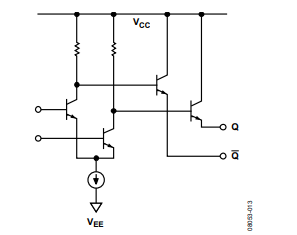

ADCLK946具有六个全摆幅的发射极耦合逻辑(ECL)输出驱动器。对于LVPECL(正ECL)输出,将VCC偏置到正电源, VEE偏置到地。对于ECL输出,将VCC偏置到地,VEE偏置到负电源。

ECL输出级设计成将每端800 mV直接驱动至端接于VCC至2 V的50 Ω电阻,从而获得1.6 V的总差分输出摆幅。

ADCLK946采用24引脚LFCSP封装,额定工作温度范围为−40℃至+85℃的标准工业温度范围。

数据表:*附件:ADCLK946采用SiGe工艺的6 LVPECL输出时钟扇出缓冲器技术手册.pdf

应用

特性

- 工作频率:4.8 GHz

- 宽带随机抖动:75 fs

- 片上输入端接

- 3.3 V电源

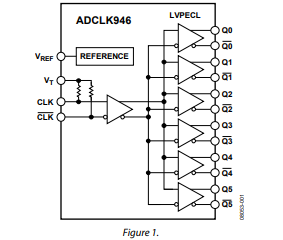

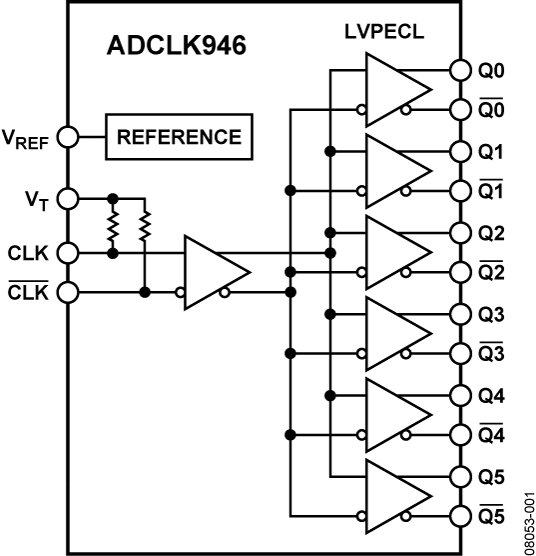

框图

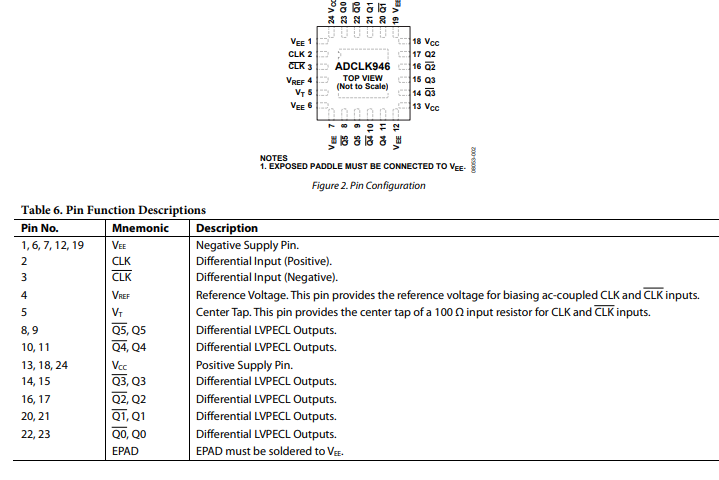

引脚配置描述

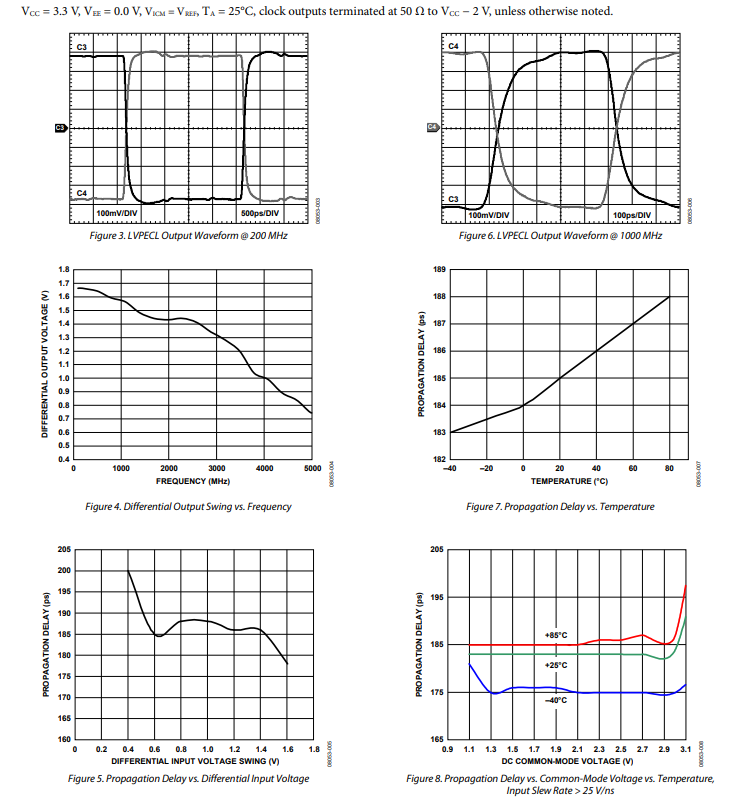

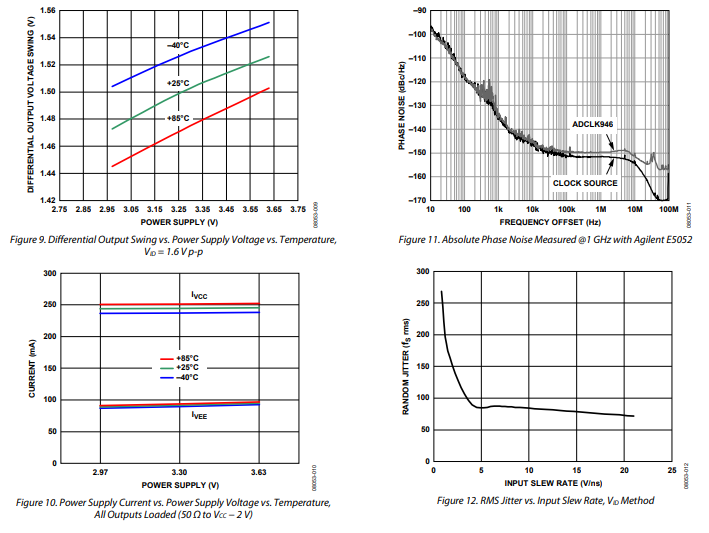

典型性能特征

功能描述

时钟输入

ADCLK946接收一个差分时钟输入,并将其分配到所有LVPECL输出。规定的最大频率是输出电压摆幅为标准LVPECL摆幅50%时的点(见图4)。

该器件具有一个配备中心抽头差分的100 Ω片上端接电阻的自由运行输入。该输入可接受交流耦合的1.8 V CMOS、LVDS和LVPECL输入。有一个Vaux引脚可用于为交流耦合输入提供偏置(见图1)。将差分输入电压摆幅保持在约400 mV峰峰值至不超过3.4 V峰峰值之间。有关各种时钟输入端接方案,请见图14 - 图17。

如图12所示,输入斜率低于1 V/ns时,输出抖动性能会下降。ADCLK946经过专门设计,可在较宽的输入斜率范围内将额外的随机抖动降至最低。只要有可能,应使用快速肖特基二极管衰减器来降低过大输入信号的斜率,因为衰减器应采用低损耗电介质或具有良好高频特性的电缆。

时钟输出

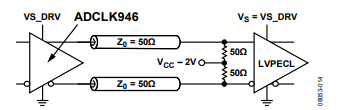

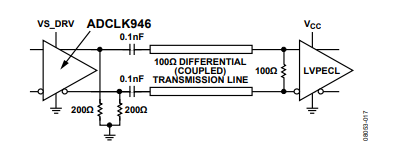

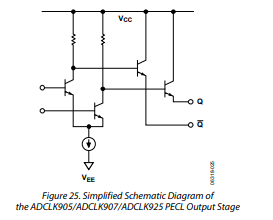

规定的性能要求使用合适的传输线终端。ADCLK946的LVPECL输出旨在直接驱动800 mV至50 Ω电缆,或驱动至以VCC - 2 V为参考端接50 Ω的微带线/带状线传输线,如图14所示。LVPECL输出级如图13所示。这些输出经过优化,可实现最佳的线路匹配。如果高速信号布线长度超过一厘米,无论是微带线还是带状线技术,都需要适当的传输线端接,以确保正确的定时,并防止过度的输出振铃和与脉冲宽度相关的传播延迟色散。

图13. LVPECL输出级的简化示意图

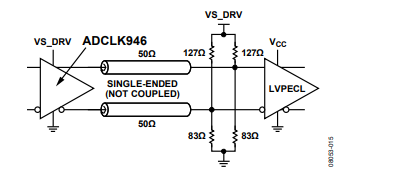

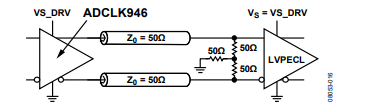

图14 - 图17描绘了各种直流耦合的LVPECL输出端接方案。当直流耦合时,接收缓冲器的Vₛ应与VS_DRV匹配。

戴维南等效端接使用电阻网络为LVPECL驱动器提供50 Ω直流端接,该直流电压低于VS_DRV。在此方案中,VS_DRV上的直流偏置点应等于接收缓冲器的Vₛ。尽管图15所示的电阻组合会产生VS_DRV - 2 V的直流偏置点,但实际的共模电压为VS_DRV - 1.3 V,因为有额外电流从ADCLK946 LVPECL驱动器的下拉电阻流出。

LVPECL Y端接是一种出色的端接方案,它使用最少的组件,同时提供奇模和偶模阻抗匹配。偶模阻抗匹配在高频下紧密耦合传输线时很重要。其主要缺点是,它在改变LVPECL驱动器射极跟随器的驱动强度方面灵活性有限。在驱动长走线时,这通常不是问题。

图14. 直流耦合,3.3 V LVPECL

图15. 直流耦合,3.3 V LVPECL 远端戴维南端接

图16. 直流耦合,3.3 V LVPECL Y端接

图17. 交流耦合,带并行传输线的LVPECL

-

缓冲器

+关注

关注

6文章

2215浏览量

48651 -

SiGe

+关注

关注

0文章

99浏览量

24448 -

时钟

+关注

关注

11文章

1953浏览量

134532

发布评论请先 登录

ADCLK946是否可以直接给AD9739作为时钟驱动LVDS

ADCLK946,pdf datasheet (SiGe C

低电压输出SiGe时钟扇出缓冲器的adclk94数据表

ADCLK946 采用SiGe工艺的6 LVPECL输出时钟扇出缓冲器

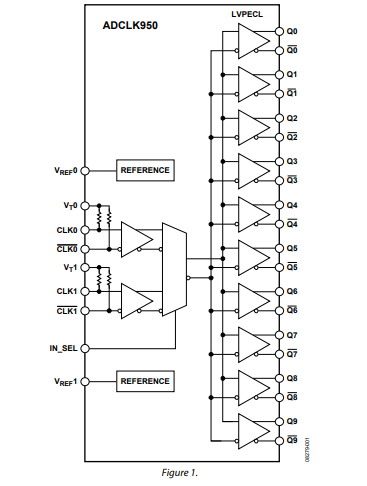

ADCLK950:两个可选输入、10个LVPECL输出、SiGe时钟扇出缓冲器数据表

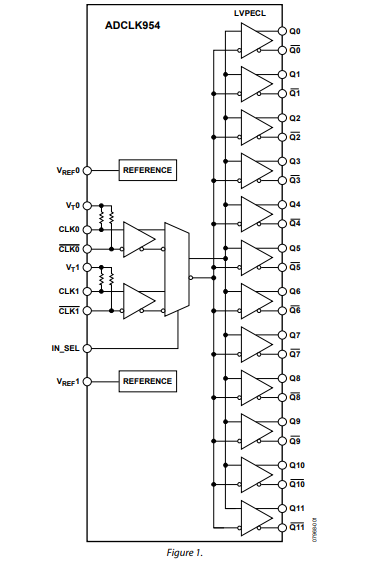

ADCLK954:两个可选输入、12个LVPECL输出、SiGe时钟扇出缓冲器数据表

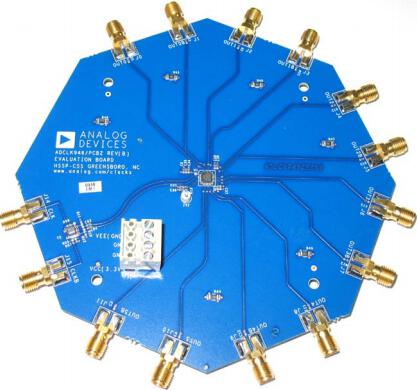

基于ADCLK946/PCBZ时钟缓冲器的参考设计

ADCLK946采用SiGe工艺的6 LVPECL输出时钟扇出缓冲器技术手册

ADCLK946采用SiGe工艺的6 LVPECL输出时钟扇出缓冲器技术手册

评论