我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。

FPGA中计数器设计探索,以计数器为32位为例:

第一种方式,直接定义32位计数器。

reg [31:0]count;

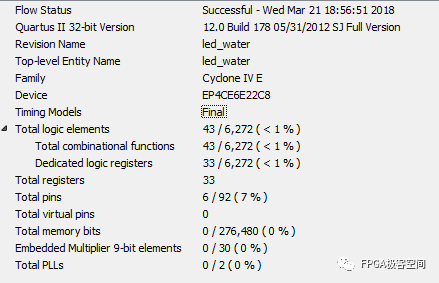

quartus ii 下的编译,资源消耗情况。

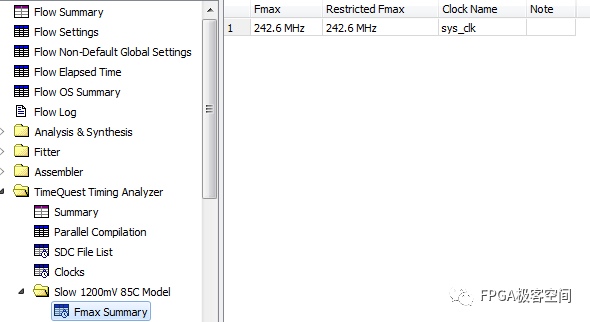

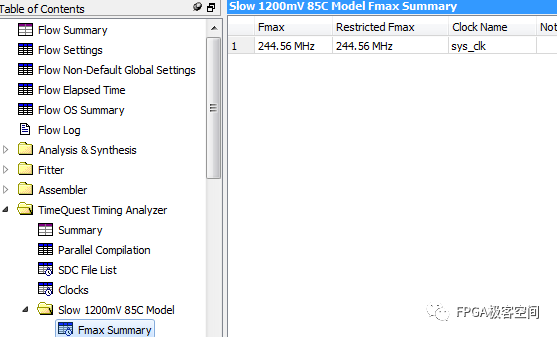

85C模型下的时钟频率。

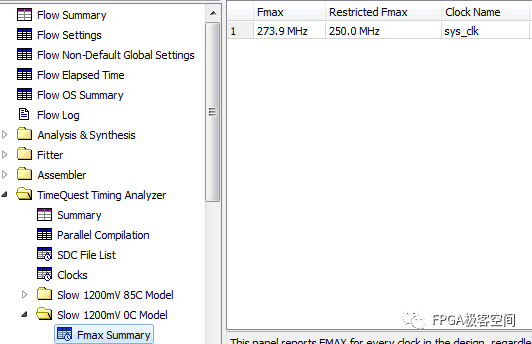

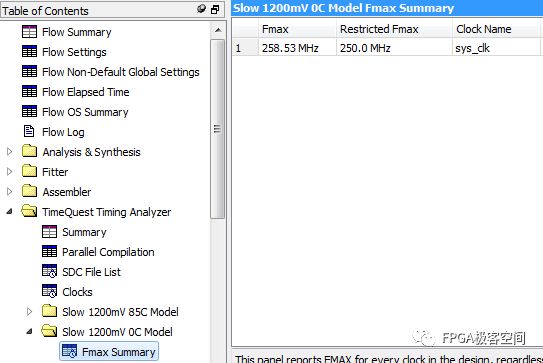

0C模型下的时钟频率。

chip planner下资源分布情况。

第二种方式,定义2个16位计数器。

reg [15:0]count1,count2;

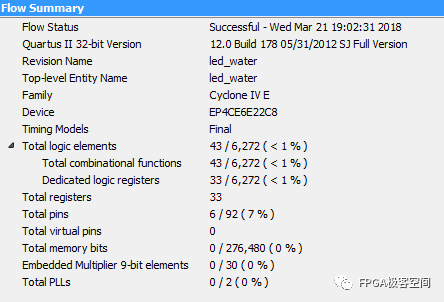

quartus ii 下的编译,资源消耗情况。

85C模型下的时钟频率。

0C模型下的时钟频率。

chip planner下资源分布情况

从上述两种情况来看,结合C4内部LAB的结构,两种方式消耗资源一样多,两种模型下的时钟频率比较接近。

值得注意的是,以上测试是在资源足够频率不高的条件下测试的。根据经验,当资源使用较多,时钟频频较高时,建议使用方式二。

-

FPGA

+关注

关注

1655文章

22283浏览量

630192 -

计数器

+关注

关注

32文章

2306浏览量

97567

原文标题:FPGA中计数器设计探索

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

频率计数器/定时器 时间间隔计数器的应用领域和范围的深度解析 频率计数器模块

雷击计数器的种类和综合选型部署解决方案

雷电(雷击)计数器的原理、作用及行业应用解决方案

MCU定时器/计数器

STM32F103高级定时器中,开启单脉冲模式是不是会立刻清除计数器使能位?

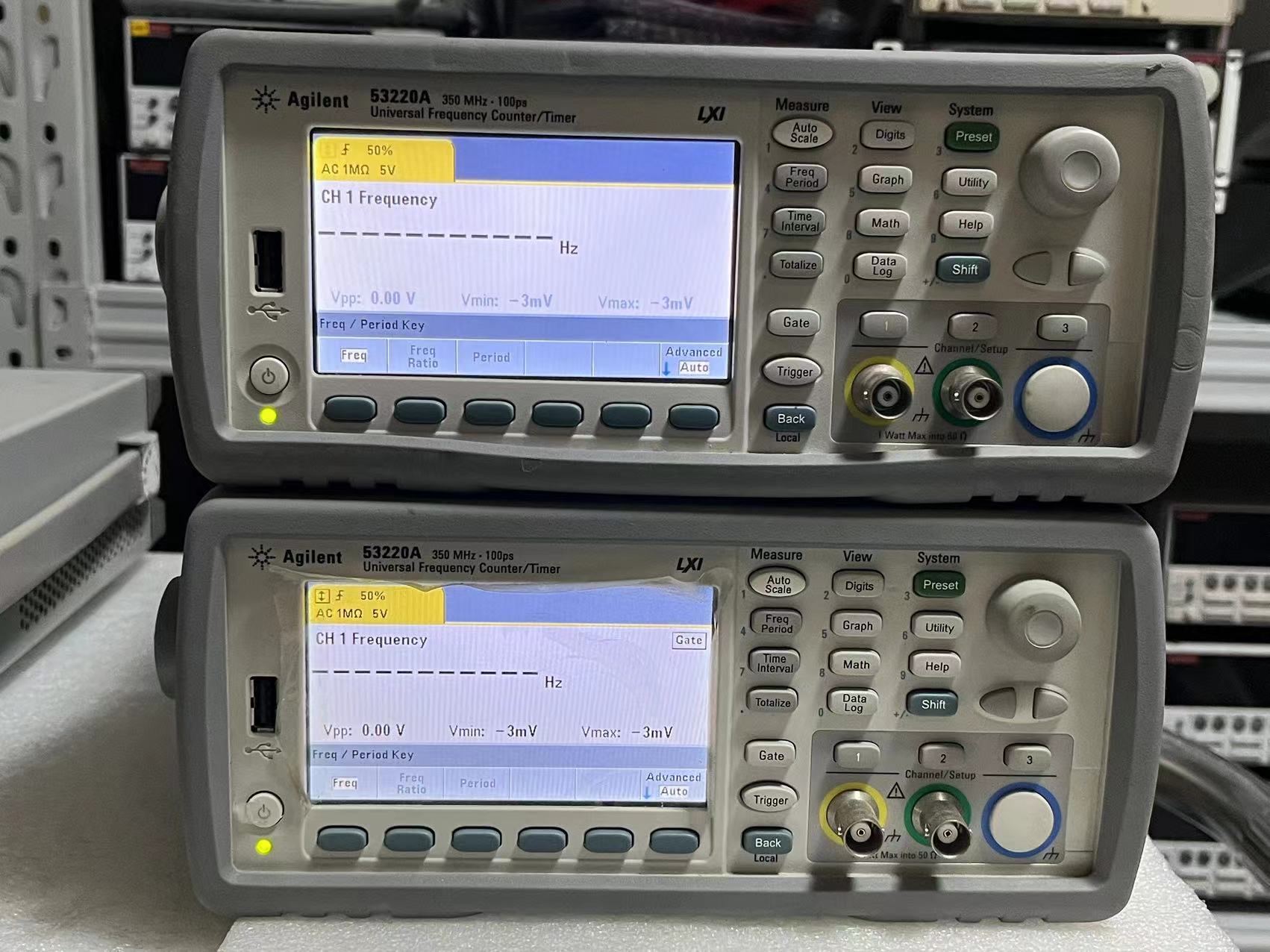

KEYSIGHT是德科技53220A台式频率计计数器原安捷伦

尘埃粒子计数器有什么特点

智能雷击计数器的综合行业解决方案

以计数器为32位为例:FPGA中计数器设计探索

以计数器为32位为例:FPGA中计数器设计探索

评论