一、引言

集成电路是现代电子技术的基石,而外延片作为集成电路制造过程中的关键材料,其性能和质量直接影响着最终芯片的性能和可靠性。本文将深入探讨集成电路外延片的组成、制备工艺及其对芯片性能的影响。

二、集成电路外延片的组成

外延片是在经过精细加工和严格处理的衬底之上,运用特定的外延生长技术,精确生长出一层或多层具备一定物理、化学和电学性能,以及特定晶体结构和厚度的半导体薄膜。外延片主要由衬底和外延层两部分组成。

(一)衬底

衬底是外延片的基础,为外延层提供生长的基础。常用的衬底材料包括单晶硅、碳化硅和蓝宝石等。

单晶硅衬底:具有优异的晶体完整性和电学性能,能为外延层提供理想的晶格匹配和生长基础。单晶硅衬底是集成电路制造中最常用的衬底材料,其纯度、晶格完整性和电学性能对最终芯片的性能有着重要影响。

碳化硅衬底:具有高击穿电场、高热导率等特性,适用于高频、高压、高功率的集成电路应用。碳化硅衬底在射频功率器件、电力电子器件等领域有着广泛的应用前景。

蓝宝石衬底:凭借良好的绝缘性能和化学稳定性,在光电器件等领域的外延片中应用广泛。蓝宝石衬底在LED、激光器等光电器件的制造中发挥着重要作用。

(二)外延层

外延层是在衬底上生长的一层或多层半导体薄膜,其性能直接影响最终芯片的性能。外延层的组成、掺杂浓度、晶体结构和厚度等参数都是精确控制的。

组成:外延层的组成与衬底材料可以相同(同质外延)也可以不同(异质外延)。同质外延生长的外延层和衬底是同一种材料,具有相同的晶格结构和化学性质;异质外延生长的外延层与衬底材料不同,或者生长化学组分、物理结构与衬底完全不同的外延层。

掺杂浓度:外延层的杂质浓度可通过精确的掺杂工艺进行调控。如在制造高性能晶体管时,可在N型外延层中精确控制磷、砷等杂质原子的浓度,以实现特定的电子迁移率和导电性。

晶体结构和厚度:外延层的晶体结构缺陷密度极低,可确保载流子在其中的高效传输,减少散射和损耗。同时,外延层的厚度也是精确控制的,以满足不同器件的设计要求。

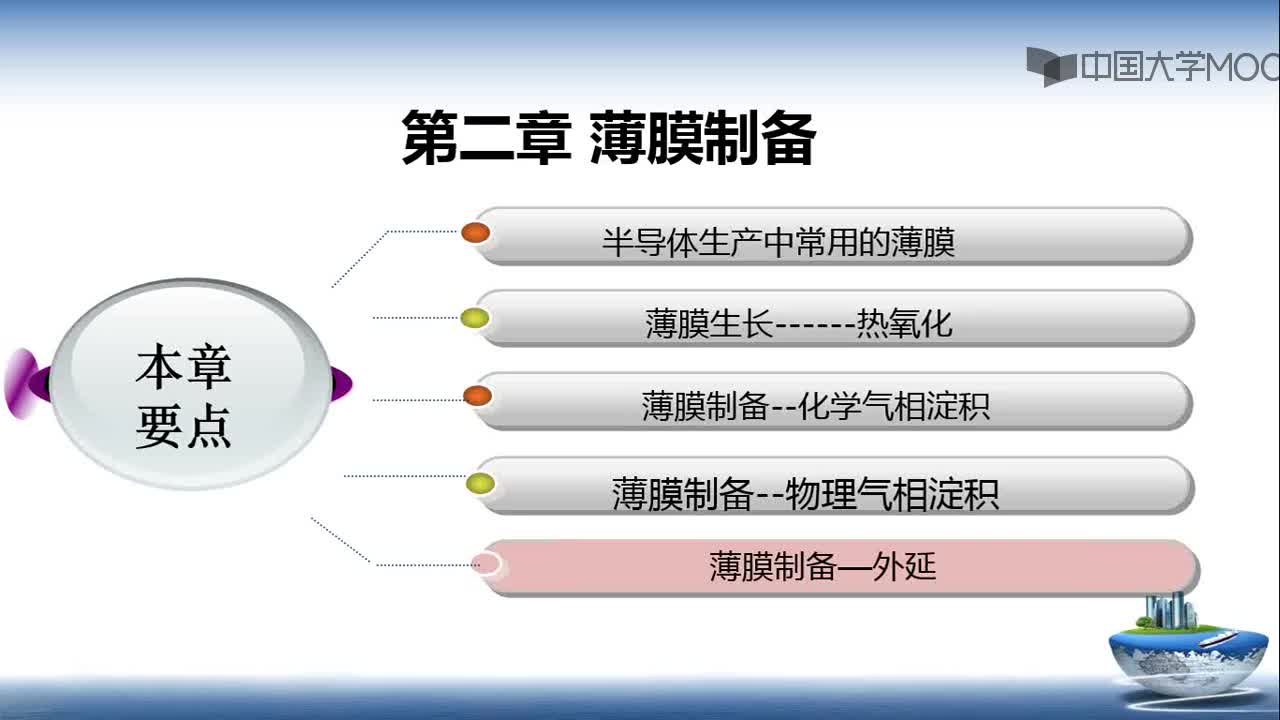

三、集成电路外延片的制备工艺

外延片的制备工艺是集成电路制造过程中的关键步骤之一,其工艺水平直接影响最终芯片的性能和可靠性。常用的外延片制备工艺包括化学气相沉积(CVD)和分子束外延(MBE)等。

(一)化学气相沉积(CVD)

化学气相沉积是外延片制备中最常用的方法之一。以金属有机化学气相沉积(MOCVD)为例,在生长氮化镓(GaN)外延层时,通常以三甲基镓(TMGa)和氨气(NH₃)作为源气体,在高温和催化剂的作用下,TMGa分解出镓原子,NH₃分解出氮原子,它们在衬底表面发生化学反应并沉积,逐渐生长出GaN外延层。通过精确控制反应温度、气体流量、压力等参数,可以精确调控外延层的生长速率、厚度和质量。

(二)分子束外延(MBE)

分子束外延是一种高真空度下的外延生长技术。在MBE系统中,有多个分别装有不同元素的蒸发源,如生长砷化镓(GaAs)外延层时,将装有镓(Ga)和砷(As)的蒸发源加热,使Ga和As原子蒸发成束状射向衬底。利用反射式高能电子衍射等技术实时监测衬底表面的原子生长情况,精确控制蒸发源的温度和蒸发时间,就能实现原子级别的精确生长。MBE技术可以生长出厚度仅为几个原子层的超薄外延层,用于制造量子阱、量子点等先进的半导体器件。

四、集成电路外延片对芯片性能的影响

外延片作为集成电路制造过程中的关键材料,其性能和质量直接影响着最终芯片的性能和可靠性。

(一)提高芯片性能

提高电子迁移率:在高速集成电路中,通过在硅外延层中采用应变工程技术,可使硅原子晶格产生一定的拉伸或压缩应变,能显著提高电子或空穴的迁移率。这有助于提高器件的工作频率和响应速度。

实现复杂功能:在系统级芯片(SoC)中,需要在同一外延片上集成多种不同功能的器件。如在CMOS工艺中,通过在外延片上依次生长不同掺杂类型和浓度的外延层,可分别用于制作PMOS和NMOS晶体管,再结合金属互连等工艺,就能实现逻辑运算、存储等多种复杂功能。

优化电学性能:外延层的掺杂浓度、晶体结构和厚度等参数都是精确控制的,可以优化器件的电学性能。例如,通过精确控制外延层的掺杂浓度,可以调整器件的阈值电压、漏电流等关键参数,提高器件的可靠性和稳定性。

(二)提高芯片可靠性

减少散射和损耗:外延层的晶体结构缺陷密度极低,可确保载流子在其中的高效传输,减少散射和损耗。这有助于提高器件的工作效率和降低功耗。

实现电气隔离:在功率集成电路中,通常会生长一层厚的绝缘外延层,如二氧化硅(SiO₂)外延层,用于实现高压器件与低压器件之间的电气隔离。这种绝缘外延层具有高击穿电压和低漏电特性,能有效防止不同电位区域之间的电流泄漏和信号串扰,确保电路在高电压、大电流环境下的稳定运行。

提高热稳定性:某些特殊的外延层材料,如碳化硅衬底,具有高热导率等特性,有助于提高器件的热稳定性。在高温环境下,碳化硅衬底能够迅速将热量散发出去,避免器件因过热而损坏。

五、结论

集成电路外延片作为集成电路制造过程中的关键材料,其组成、制备工艺及对芯片性能的影响是半导体技术领域的重要研究课题。通过精确控制外延层的组成、掺杂浓度、晶体结构和厚度等参数,可以显著提高芯片的性能和可靠性。随着半导体技术的不断发展,外延片制备工艺也将不断创新和完善,为集成电路产业的发展提供有力支撑。

未来,随着5G通信、人工智能、物联网等新兴技术的快速发展,对集成电路的性能和可靠性提出了更高要求。外延片作为集成电路制造过程中的关键材料,其研究和开发将更加注重高性能、低成本和环保等方面。通过不断优化外延片制备工艺和提高材料性能,将有助于推动集成电路产业的持续发展和创新。

-

集成电路

+关注

关注

5446文章

12465浏览量

372655 -

半导体封装

+关注

关注

4文章

312浏览量

15126 -

外延片

+关注

关注

0文章

40浏览量

9994

发布评论请先 登录

半导体制造之外延工艺详解

CMOS集成电路的基本制造工艺

集成电路外延片详解:构成、工艺与应用的全方位剖析

集成电路外延片详解:构成、工艺与应用的全方位剖析

评论