声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

封装

+关注

关注

128文章

9317浏览量

149026

发布评论请先 登录

相关推荐

热点推荐

85页PPT,看懂芯片半导体的封装工艺!

经过半导体制造(FAB)工序制备的电路图形化晶圆容易受温度变化、电击、化学和物理性外部损伤等各种因素的影响。为了弥补这些弱点,将芯片与晶圆分离后再进行包装, 这种方法被称为“半导体封装

集成电路制造中薄膜生长工艺的发展历程和分类

薄膜生长是集成电路制造的核心技术,涵盖PVD、CVD、ALD及外延等路径。随技术节点演进,工艺持续提升薄膜均匀性、纯度与覆盖能力,支撑铜互连、高k栅介质及应变器件发展。未来将聚焦低温沉积、三维结构适配与新材料集成,实现性能与可靠

一文详解封装基板的制备工艺

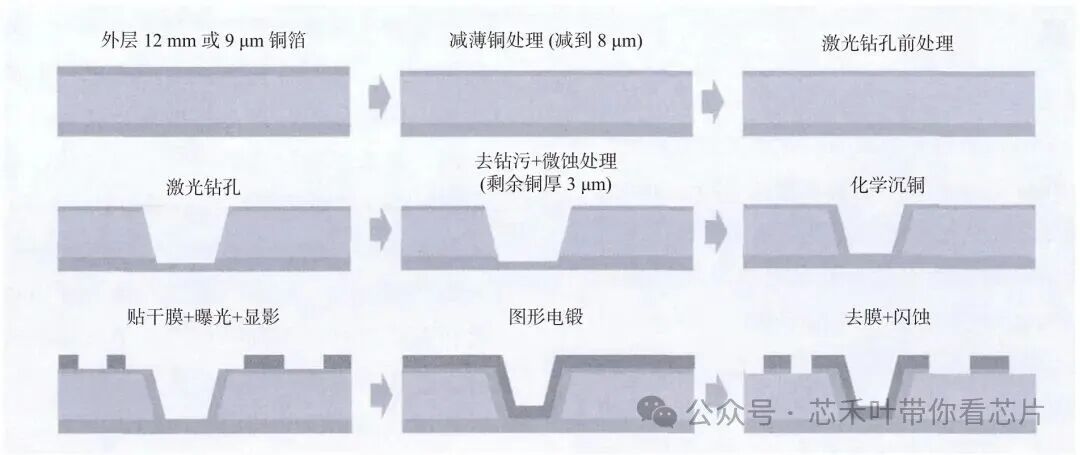

在封装基板发展的早期阶段,广泛采用一种称为减成法的印制电路板制造技术,亦称蚀刻铜箔技术。该技术的基本原理是在覆铜板上印刷出所需的电路图案,通过抗蚀膜保护图案区域,随后利用化学蚀刻去除未

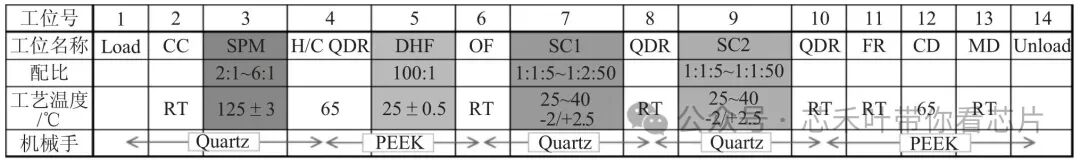

集成电路制造中常用湿法清洗和腐蚀工艺介绍

集成电路湿法工艺是指在集成电路制造过程中,通过化学药液对硅片表面进行处理的一类关键技术,主要包括湿法清洗、化学机械抛光、无应力抛光和电镀四大类。这些工艺贯穿于芯片制造的多个关键环节,直

集成电路制造中薄膜刻蚀的概念和工艺流程

薄膜刻蚀与薄膜淀积是集成电路制造中功能相反的核心工艺:若将薄膜淀积视为 “加法工艺”(通过材料堆积形成薄膜),则薄膜刻蚀可称为 “减法工艺”(通过材料去除实现图形化)。通过这一 “减”

PDK在集成电路领域的定义、组成和作用

PDK(Process Design Kit,工艺设计套件)是集成电路设计流程中的重要工具包,它为设计团队提供了与特定制造工艺节点相关的设计信息。PDK 是集成电路设计和制造之间的桥梁

集成电路传统封装技术的材料与工艺

集成电路传统封装技术主要依据材料与管脚形态划分:材料上采用金属、塑料或陶瓷管壳实现基础封装;管脚结构则分为表面贴装式(SMT)与插孔式(PIH)两类。其核心工艺在于通过引线框架或管座内

玻璃基板在芯片封装中的应用

自集成电路诞生以来,摩尔定律一直是其发展的核心驱动力。根据摩尔定律,集成电路单位面积上的晶体管数量每18到24个月翻一番,性能也随之提升。然而,随着晶体管尺寸的不断缩小,制造工艺的复杂度和成本急剧

电机控制专用集成电路PDF版

本书共13章。第1章绪论,介绍国内外电机控制专用集成电路发展情况,电机控制和运动控制、智能功率集成电路概况,典型闭环控制系统可以集成的部分和要求。第2~7章,分别叙述直流电动机、无刷直流电动机、步进

发表于 04-22 17:02

中国集成电路大全 接口集成电路

资料介绍本文系《中国集成电路大全》的接口集成电路分册,是国内第一次比较系统地介绍国产接口集成电路的系列、品种、特性和应用方而知识的书籍。全书共有总表、正文和附录三部分内容。总表部分列有国产接口

发表于 04-21 16:33

集成电路封装基板工艺详解(68页PPT)

集成电路封装基板工艺详解(68页PPT)

评论