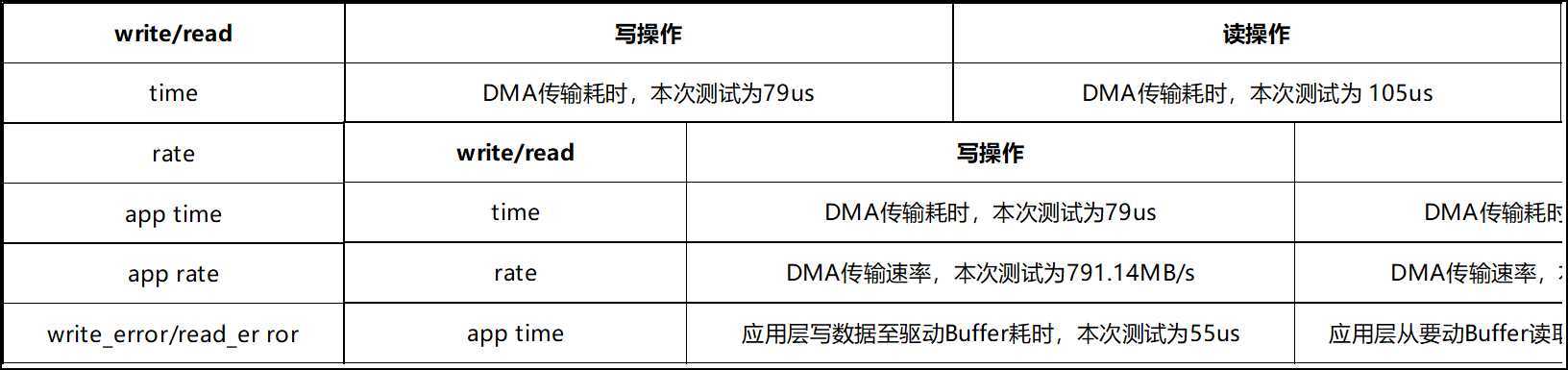

测试数据汇总

表 1

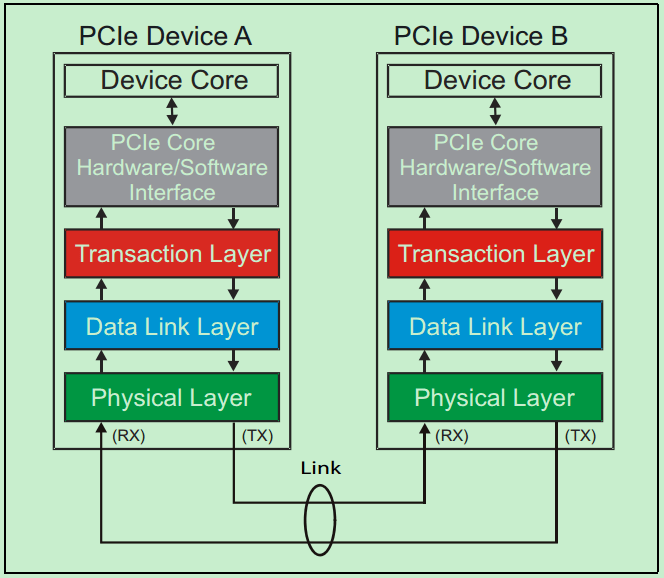

PCIe总线介绍

PCIe,即PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准。主要用于扩充计算机系统总线数据吞吐量以及提高设备通信速度。

图 1

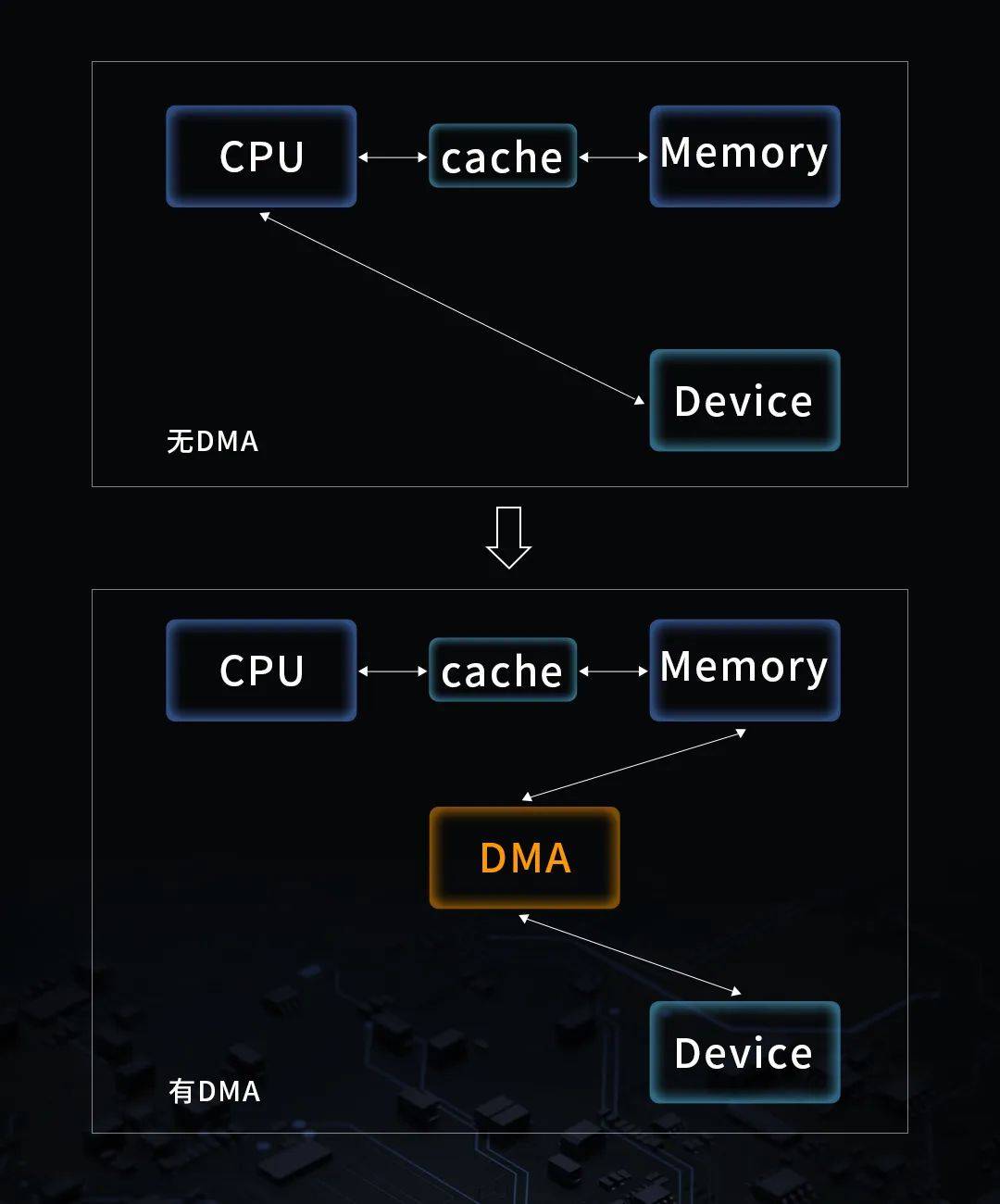

DMA技术介绍

DMA(Direct Memory Access,直接内存访问)是一种让硬件外设直接与存储器进行数据交换的技术,无需CPU参与数据传输过程。

使用非DMA方式进行数据传输时,外设与内存之间的数据搬运需要依靠CPU来完成。这意味着每次数据传输都需要CPU的介入,导致CPU资源占用较高,并且数据传输速度相对较低。

使用DMA方式进行数据传输时,外设可以直接与内存进行数据交换。减少了CPU的介入和中断处理,数据传输过程更加流畅和高效。

图 2

RK3568J + FPGA典型应用场景

图 3

基于RK3568J + FPGA的PCIe通信案例

本文主要介绍基于RK3568J + FPGA的PCIe通信案例,适用开发环境如下:

Windows开发环境:Windows 7 64bit、Windows 10 64bit

Linux开发环境:VMware15.5.5、Ubuntu18.04.4 64bit

U-Boot:U-Boot-2017.09

Kernel:Linux-4.19.232、Linux-RT-4.19.232

LinuxSDK:LinuxSDK-[版本号](基于rk356x_linux_release_v1.3.1_20221120)

硬件平台:创龙科技TL3568F-EVM工业评估板

(基于瑞芯微RK3568J + 紫光同创Logos-2)

为了简化描述,本文仅摘录部分方案功能描述与测试结果,详细产品资料可以通过公众号(Tronlong创龙科技)下载。

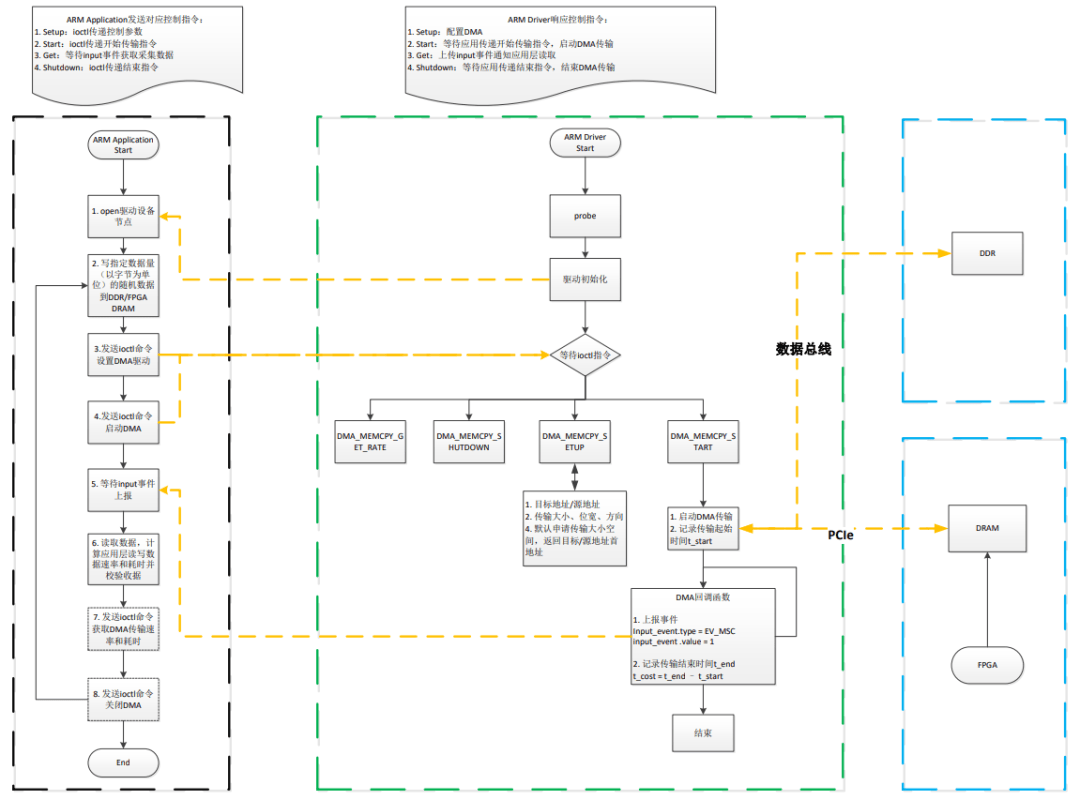

案例说明

ARM端基于PCIe总线对FPGA DRAM进行读写测试。应用程序通过ioctl函数发送命令开启DMA传输数据后,等待驱动上报input事件;当应用层接收到input事件,说明DMA传输数据完成。

程序流程如下图所示。

图 4

(1)ARM端程序原理说明如下:

a)采用DMA方式;

b)将数据写至dma_memcpy驱动申请的连续内存空间(位于DDR);

c)配置DMA,如源地址、目标地址、传输的数据大小等;

d)写操作:通过ioctl函数启动DMA,通过PCIe总线将数据搬运至FPGA DRAM;

e)程序接收驱动上报input事件后,将通过ioctl函数获取DMA搬运数据耗时,并计算DMA传输速率(即写速率);

f)读操作:通过ioctl函数启动DMA,通过PCIe总线将FPGA DRAM中的数据搬运至dma_memcpy驱动申请的连续内存空间(位于DDR);

g)程序接收驱动上报input事件后,将数据从内核空间读取至用户空间,然后校验数据,同时通过ioctl函数获取DMA搬运数据耗时,并计算DMA传输速率(即读速率)。

(2) FPGA端程序原理说明如下:

a)实现PCIe Endpoint功能;

a)处理PCIe RC端发起的PCIe BAR0空间读写事务;

b)将PCIe BAR0读写数据缓存至FPGA DRAM中。

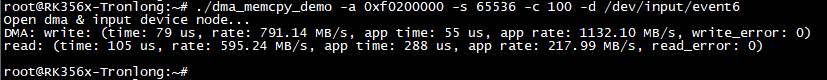

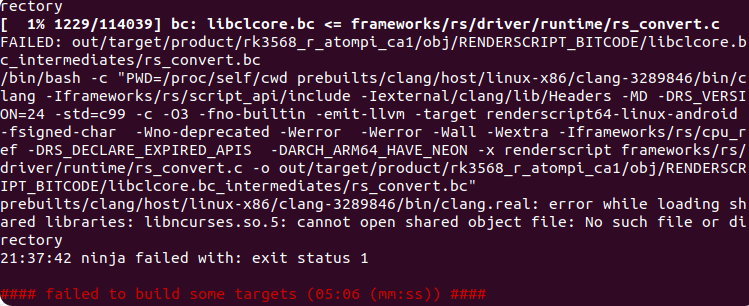

案例演示

评估板上电启动后,进入评估板文件系统执行如下命令,将随机数据先写入FPGA DRAM,再从FPGA DRAM读出。测试完成后,程序将会打印最终测试结果,包含读写平均传输耗时、读写平均传输速率、读写错误统计等信息。

Target#./dma_memcpy_demo -a 0xf0200000 -s 65536 -c 100 -d /dev/input/event6

图 5

表 2 测试结果说明

到这里,我们的演示步骤结束。想要查看更多瑞芯微RK3568J + FPGA相关的案例演示,欢迎各位工程师通过公众号(Tronlong创龙科技)下载,快来试试吧!

审核编辑 黄宇

-

FPGA

+关注

关注

1664文章

22502浏览量

639149 -

PCIe

+关注

关注

16文章

1479浏览量

88917

发布评论请先 登录

RK3568 Android11编译环境搭建及报错解决指南

【迅为工业RK3568稳定可靠】itop-3568开发板Linux驱动开发实战:RK3568内核模块符号导出详解

【赛题教程】基于RK3568+PG2L50H实现八路视频输入参考方案

【HZ-RK3568开发板免费体验】HZ-RK3568开发板操作系统编译

【HZ-RK3568开发板免费体验】合众HZ-RK3568开发板初次使用

【HZ-RK3568开发板免费体验】1、开发板资源、SDK使用和镜像烧写

【HZ-RK3568开发板免费体验】合众HZ-RK3568开发板测评

【HZ-RK3568开发板免费体验】HZ-RK3568开发板初步接触

【HZ-RK3568开发板免费体验】01 开箱+环境搭建+系统烧录升级

紫光同创Logos2+RK3568开发板|国产器件强强联合开启嵌入式开发新篇章

紫光同创Logos2+RK3568开发板:国产器件强强联合开启嵌入式开发新篇章

1分钟学会如何提升PCIe通信速率,基于RK3568J + FPGA国产平台!

1分钟学会如何提升PCIe通信速率,基于RK3568J + FPGA国产平台!

评论