在当今高速电子系统的设计与应用中,信号完整性已成为至关重要的考量因素。随着电子设备的数据传输速率不断攀升,信号在电路中传输时面临着诸多挑战,如反射、串扰、延迟等,这些问题会严重影响系统的性能和可靠性。

当信号沿着传输线传播时,遇到阻抗不连续的点,就会发生反射现象。例如,在电路板上的走线宽度变化、过孔连接或者不同层间的介质差异等,都可能导致阻抗突变。反射回来的信号与原始信号叠加,会造成信号失真,使接收端难以准确识别信号的逻辑状态。

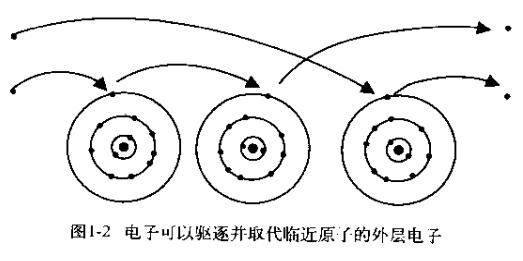

串扰则是指相邻信号线路之间的电磁耦合,一条线路上的信号变化会在相邻线路上感应出噪声信号。在高密度布线的电路板中,这种现象尤为明显。例如,在高速数字电路中,时钟线与数据线相邻时,时钟信号的快速跳变可能会在数据线上产生串扰噪声,导致数据传输错误。

延迟问题也不容忽视。信号在传输线中的传播速度并非无限,而且不同长度和材质的传输线会产生不同的延迟。在同步电路系统中,如果信号延迟差异过大,可能会导致时序违规,使数据无法在正确的时钟沿被采样,从而引发系统故障。

为解决信号完整性问题,首先在电路设计阶段要进行合理的拓扑规划。对于多点连接的网络,如总线结构,采用合适的拓扑(如星形、树形或菊花链形)可以优化信号的分布和传输路径,减少反射和延迟的影响。同时,要精确控制传输线的阻抗匹配,通过调整走线的宽度、间距以及介质的介电常数等参数,使传输线的特征阻抗与源端和负载端的阻抗相匹配,从而有效降低反射。

在 PCB 布局方面,要遵循一定的规则。将高速信号与低速信号分开布局,减少相互之间的串扰。对于敏感信号,如模拟信号和微弱的传感器信号,要进行良好的屏蔽处理,防止受到其他强信号的干扰。此外,合理安排过孔的位置和数量,因为过孔会引入额外的电感和电容,影响信号的完整性,应尽量减少不必要的过孔使用。

在高速电路设计中,还可以采用一些信号完整性分析工具,如 HSPICE、ADS 等软件进行仿真分析。在设计初期对电路进行建模和仿真,能够提前预测信号完整性问题,并根据仿真结果对电路设计进行优化调整,大大提高设计的成功率和效率,降低硬件调试的成本和时间。

随着电子技术的不断发展,信号完整性问题将持续面临新的挑战,但通过不断优化电路设计、PCB 布局以及借助先进的仿真分析工具,我们能够有效地应对这些问题,确保电子系统的高性能和可靠性,推动电子技术在各个领域的广泛应用和进一步发展。

-

信号完整性

+关注

关注

68文章

1497浏览量

98237 -

电子电路

+关注

关注

78文章

1291浏览量

69366 -

PCB

+关注

关注

1文章

2351浏览量

13204

发布评论请先 登录

常见的信号完整性问题及解决方案

PCB设计中的信号完整性问题

探究电子电路中的信号完整性问题

探究电子电路中的信号完整性问题

评论