RISC-V 已迅速成为全球处理器设计和实现领域的领先标准指令集架构(ISA)。与私有架构不同,RISC-V 是一种开放给所有人的处理器设计标准,为行业带来了前所未有的创新。RISC-V 的重要性、其对科技行业的影响在促进科技领域增长和发展的作用,涵盖了从小型轻量级处理器到强大高性能处理器的整个计算领域。从跨国公司的深度投资到与初创公司的风险投资合作,从大学课堂到国家层面,RISC-V 正在不断扩大其市场份额。如今,RISC-V 社区拥有来自全球 70 个国家和地区的数万名工程师的贡献。

截至目前,玄铁已发布多款产品线,覆盖从低功耗到高性能的多个应用场景。其中包括为节能设计、适用于物联网设备等领域的 E 系列;实时处理能力和高度可靠性的 R 系列;极致性能表现的 C 系列高端处理器和刚发布致力于解决多集群间高效互联的 XT-link 系列。以 C 系列为例:该系列包含多个分支,包括专注于实现最佳能效比的 C908 处理器,强化人工智能计算能力的 C907 处理器;早期发布的旗舰级 C910 处理器与后续升级版本 C920 处理器;后续即将发布的更高性能 C930处理器等,每一款产品都有其独特的市场定位和 PPA 需求。

本文将由玄铁团队技术专家寇博华分享关于玄铁设计与交付在 PPA 优化中的实践:波形激励在数字设计功耗优化中的全面解析。

寇博华

阿里巴巴达摩院玄铁团队技术专家

阿里巴巴达摩院玄铁处理器设计团队技术专家;拥有丰富的低功耗设计经验,与前端和后端团队紧密协作,专注于优化 PPA,并加速设计收敛的进程。

在芯片设计中,功耗、性能和面积(PPA)是衡量产品竞争力的三大关键指标。其中,功耗指标直接影响到产品的能效、热管理和电池寿命。为了优化功耗,从架构设计到代码实现,再到后端实现的每一个环节都需要精心打磨。然而,要准确分析和优化功耗,正确的波形激励是不可或缺的。

波形激励本质上是对设计中每一个信号翻转信息的描述,它能够帮助我们理解信号在不同时间点的状态变化。只有使用了正确的波形激励输入,我们才能获得有意义的信号翻转数据,进而得到准确的功耗分析结果。本文将深入波形激励在功耗优化中的各个方面,包括波形记录格式、波形场景定义、波形生成方法以及反标率的确认,旨在为读者提供全面的技术解析和实用指南。

一 波形的记录格式

在数字设计中,信号的翻转信息是功耗分析的关键。通常,信号的翻转可以通过两个参数来描述:toggle rate 和 static probability。

Toggle rate:表示信号在一个时钟周期内的平均翻转次数。如果一个信号的 toggle rate 为 1,表示该信号在每一个时钟周期都有一次翻转(即从 0 到 1 或从 1 到 0)。如果 toggle rate 为 0,则表示该信号在整个时间窗口内没有发生任何翻转。对于时钟信号,由于在一个时钟周期内会有上升沿和下降沿,所以其 toggle rate 最大为 2。

Static probability:表示一个信号在整个时间窗口中为 1 的占比。例如,如果一个信号在 50% 的时间内为 1,则其 static probability 为 0.5。

信号的翻转信息通常记录在特定的波形文件格式中,常见的有 SAIF、VCD 和 FSDB:

SAIF (Switching Activity Interchange Format):由于仅记录每个信号在整个时间窗口内的平均翻转状态,即 toggle rate 和 static probability,所以 SAIF 文件仅能用来分析平均功耗。

VCD (Value Change Dump):以 ASCII 格式记录信号在每个时钟周期的具体翻转变化。VCD 文件可以直接用文本编辑器打开阅读,但由于其详细记录了每个时钟周期的变化,文件体积较大。

FSDB (Fast Signal Database):和 VCD 格式一样, FSDB 文件也记录了每个时钟周期信号的变化,但是由于采用二进制格式记录,虽然不能直接以文本方式打开,但文件体积最小。FSDB 文件可以通过工具脚本转换成其他格式,如 VCD 或 SAIF。

二 波形场景的定义

在功耗分析过程中,我们需要针对架构功能定义不同的功耗场景。这些场景可以帮助我们评估和分析整体与各个功能的功耗和能效。以下是一些常见的场景介绍:

场景分类 | 场景介绍 |

基准测试 | 以CPU为例,以下是一些典型的基准测试: Dhrystone:经典的整型运算基准测试 Whetstone:用于评估浮点计算的功耗 Sgemm:用于评估向量计算的功耗 Memcpy:用于评估数据在缓存之间搬运的功耗 |

功耗建模 | 在功耗建模中,可以灵活运用不同的指令组合搭建各种测试用例,用来激活设计中主要的数据通路。这种方法有助于构建和验证功耗模型。 |

时钟门控分析 | 需要使用丰富的波形激励来不同程度的激活各个功能单元,用来观测和完善在 RTL 插入的时钟门控使能和叶级寄存器使能。 |

综合和后端工具 | 对于综合和后端工具,我们会提供合适的波形激励,以便工具更好地优化动态功耗。 |

特殊功耗场景 | 还有一些有特殊需求的功耗场景,例如 Max Power 和 di/dt 用来帮助后端团队分析和保证芯片系统和电源网络的可靠性。 |

三 波形的形态和生成

以下是常用的几种波形激励形态及其生成方法:1. 基于 RTL 的波形激励

最常见的波形激励是通过 RTL 验证前仿生成的。这些波形激励对应的是 RTL 级别中各个信号的翻转情况。通过 RTL 仿真,我们可以详细记录每个信号在不同时间点的状态变化,从而为后续的功耗分析提供基础数据。

2. 基于网表级别的波形激励

后仿生成:常规的网表级波形激励是通过跑后仿来生成的。如果不带线(wire)和实例(instance)的延迟信息,得到的后仿波形激励通常称为零延迟(zero-delay)波形。另一种需要带延迟信息的波形称为 SDF 延迟(sdf-delay)波形。为了获取延迟信息,后端工具需要抽取寄生参数,并在时序工具(如PrimeTime)中进行反标,计算出实际的延迟,然后将这些延迟/转换时间等信息写入 SDF 文件。跑后仿时可以带着 SDF 文件生成更准确的波形。

replay 生成:由于后仿通常在项目后期才调通,而我们希望尽早获得更准确的功耗数据,因此在项目中期,当综合和后端实现完成后,我们会使用 EDA 工具将 RTL 波形、综合产生的映射文件(mapping file)、SDF 文件以及实际的网表结合,生成一个网表级的波形激励。

通过这些不同阶段的波形激励生成方法,我们可以在整个设计流程中逐步细化和校准功耗数据,确保最终产品的功耗性能达到预期目标。

四 波形的反标率

在将波形的翻转信息反标到设计(RTL 代码或网表)上时,确保反标的准确性至关重要。导致反标率低的常见错误有:

波形和设计不匹配

层级映射错误

MDA 选项未启用

反标的信息一般分为两个维度:

纬度1 | Primary Input:设计的输入输出 |

Sequential:时序逻辑,通常为寄存器 | |

Combinational:组合逻辑 | |

Memory:存储器 | |

纬度2 | From Activity File:波形文件 |

From SCA/SSA:设置的翻转约束 | |

Propagated/implied:工具自动分析得到的翻转信息,主要用于组合逻辑信号 | |

Default/Not-Annotated:两者都表示没有有效的来源,区别在于default会给一个默认翻转率;而Not-Annotated不会给任何翻转率 |

在检查反标率时,有些参考指标是通用的:

Memory:memory macro 上的反标应该100%来自 Activity File。

Primary Input:功能性接口信号应该从 Activity File 来,个别约束可以从 SCA/SSA 来。

而有些则根据波形和设计的阶段有所不同:

RTL波形反标到网表:

在有 mapping file 的情况下,时序逻辑(sequential)大部分需要来自 Activity File。

组合逻辑(combinational)反标率不会太高,所以这部分的功耗与实际值会有明显差距。

网表级波形反标到对应的网表:所有信号都应该100%来自 Activity File。

通过仔细检查这些指标和要求,可以确保波形反标操作的准确性和有效性,从而提高功耗分析的精度和可靠性。

五 波形激励在不同阶段的使用

在玄铁团队,波形激励的生成和使用贯穿于整个设计流程的不同阶段,以确保功耗优化的有效性和准确性:

项目初期:RTL 前仿

在项目的早期阶段,我们主要基于 RTL 前仿真生成波形。这些波形用于初步的功耗分析,特别是在分析时钟动态门控和存储器翻转效率方面。另外,通过使用 RTL 功耗工具读取这些波形,我们也可以得到功耗数据的早期评估,分析潜在的功耗瓶颈。

优化中期:RTL 前仿+ Replay

在优化的中期阶段,我们会选择具有代表性的波形,提供给后端团队用于综合和后端实现,帮助工具更有效地优化动态和静态功耗。此外,我们还会使用 replay 工具生成网表级别的零延迟(zero-delay)和带延迟(sdf-delay)波形激励。这有助于尽早评估和分析各个场景下更真实的功耗水平,并进行相应的优化。

PPA优化后期:后仿真

到了 PPA 优化的后期,验证团队会调通后仿,生成基于后仿真的网表级波形激励。我们将这些后仿波形与之前通过 replay 机制生成的数据进行对比,以获得最真实的功耗数据。这种对比也可以帮助我们验证前期优化的效果。

后续探索:性能建模与仿真平台

为了进一步提高功耗分析的准确性和全面性,我们还可以尝试在更早期基于性能建模产生的信号激励来进行功耗建模。此外,我们也可以利用 FPGA 和 Emulator 仿真平台自带的激励和功耗分析工具,对更复杂和完整的系统级场景进行功耗分析。这种方法能够更好地模拟实际工作环境,从而提供更为精确的功耗数据。

六 结 语

玄铁的每一款产品都有其独特的市场定位,同时需要满足不同市场细分下的性能和PPA要求。玄铁团队不仅需要面对不同产品线的常规迭代升级、大规模的架构升级,还要紧跟上市发布时间节点,时间紧任务重,对于PPA快速迭代需求变高。通过这些不同阶段的波形激励使用方法,玄铁能够在整个设计流程中持续优化和分析功耗,确保最终产品的高效能和竞争力。

-

数字设计

+关注

关注

0文章

50浏览量

22855 -

PPA

+关注

关注

0文章

21浏览量

7822 -

RISC-V

+关注

关注

49文章

2952浏览量

53559

发布评论请先 登录

高频交直流探头在电机驱动与变频控制中的应用:从波形分析到系统优化

步进电机驱动板细分控制策略与电流波形优化

跳线架在数据中心的应用与优化策略

【高端人才招聘】格见半导体 资深数字后端工程师 上海&成都

【高端人才招聘】格见半导体 资深数字后端工程师

Powered by XuanTie,Qwen Inside:阿里通义大模型携手玄铁 RISC-V开启“端侧智能”新纪元

请问如何优化芯片的功耗管理?

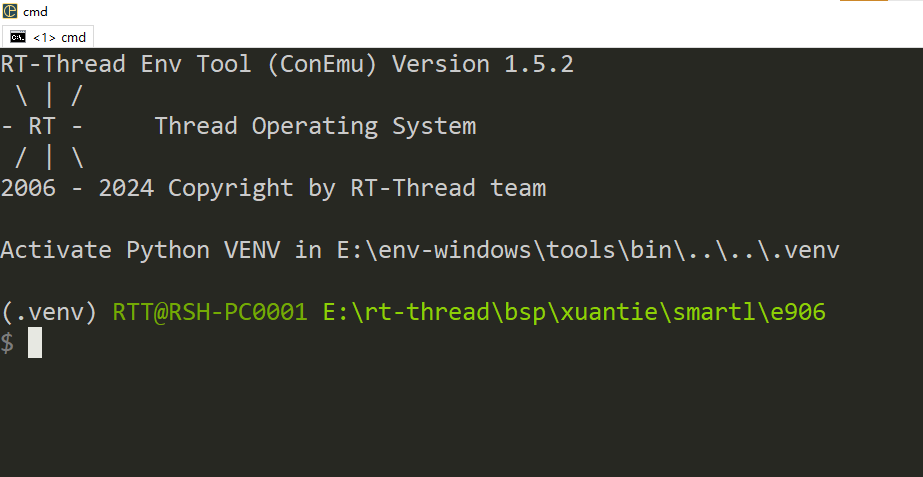

RT-Smart、玄铁C908与嘉楠K230的端侧AI软硬生态 | 问学直播

MDD 逻辑IC的功耗管理与优化策略

学以致用 虚位以待|玄铁RV学院课程正式上线,玄铁与PLCT实验室邀您创“芯”未来

【RT-Thread×玄铁 | 硬核直播】RISC-V新核E901发布!RT-Thread手把手带你玩转玄铁生态! | 博观讲堂

CI/CD实践中的运维优化技巧

RT-Thread BSP全面支持玄铁全系列RISC-V 处理器 | 技术集结

玄铁设计与交付在 PPA 优化中的实践:波形激励在数字设计功耗优化中的全面解析

玄铁设计与交付在 PPA 优化中的实践:波形激励在数字设计功耗优化中的全面解析

评论