随着带宽需求飙升至新高度,多芯粒系统正成为许多应用领域的解决方案。通过在单一封装中异构集成多个芯粒,Chiplet芯粒系统能够为人工智能、高性能计算和超大规模数据中心提供更高的处理能力和性能。一系列技术创新为多芯粒系统的出现铺平了道路,其中关键的一项创新是UCIe标准。UCIe标准于2022年3月推出,是芯粒互联国际标准,UCIe有助于构建一个更广泛的、经过验证的芯粒生态系统。

奇异摩尔是最早一批加入UCIe 联盟的成员,从成立至今持续致力于芯粒生态的建设。经过不断的研发并积极践行UCIe标准,现荣幸宣布基于UCIe 1.1v的32GT/s Kiwi Link Die-to-Die IP正式问世。奇异摩尔将在后天举行的ICCAD 2024展会上全面展示该创新产品并提供1v1的专业技术交流。

01奇异摩尔32GT/s Kiwi Link

Die-to-Die IP 全面上市

奇异摩尔提供完整的UCIe Die-to-Die IP解决方案,包括Controller,PHY和验证完成的IP。该款IP Standard版本以32Gbps的速度运行,实现芯粒之间的超高速互联通信,同时保持完全符合UCIe 1.1版本规范。

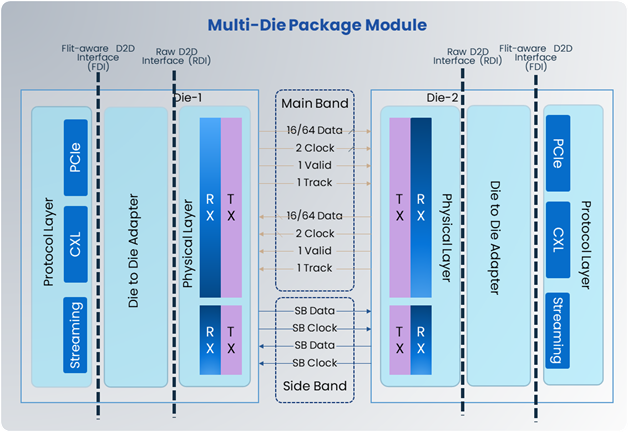

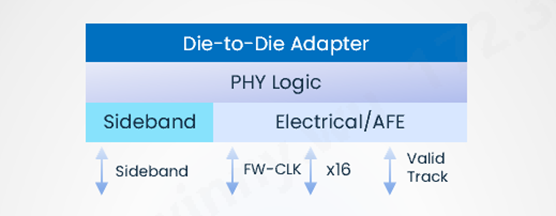

奇异摩尔的UCIe Die-to-Die IP包含基于了UCIe标准的低时延Controller(控制器),它包括Die-to-Die Adapter 和Protocol Layer 负责Sideband信息的收发实现Link bring up和Link magement,负责Mainband数据的发送和接收。UCIe Controller内部Die-to-Die Adapter Adapter 和Protocol Layer之间支持FDI接口, UCIe Controller与PHY之间支持RDI接口。

奇异摩尔UCIe Die-to-Die IP提供了卓越的高带宽、极低延迟和较高的可兼容性。为了确保链路传输的可靠性,该IP支持CRC(循环冗余码)检查和重传机制。其设计适用于单模块和多模块配置,并能够应用于多种封装形式,包括标准封装及先进封装。

产品主要亮点

1符合UCIe v1.1 国际互联标准;

2带宽32Gbps速率、延迟ns;

3提供基于UCIe 的多芯粒低延迟的Controller (控制器);

4支持单模块和多模块 UCIe 配置;

5支持多种协议包括PCIe、CXL 及Streaming协议;

6支持多种封装形态(标准封装/先进封装);

02Kiwi Link Die-to Die IP

差异化特性 (UCIe 标准外)

物理层是封装介质的电气接口。它包括支持高速数据收发的电气PHY,以及可实现链路初始化、训练和校准算法以及测试和修复功能的逻辑 PHY。

UCIe 提供了两大数据通路:Mainband 及 Sideband。Mainband 用来传输业务数据流,Sideband 用来来处理一些 链路训练、链路管理、参数交换及寄存器访问 等非数据传输业务。Sideband 作为 Mainband 的 Back Channel,能够简化UCIE中的链路训练、链路管理和D2D参数交换,简化数据链路的建立过程、提升 Mainband 的带宽利用率、简化 Mainband 设计复杂度。

物理层的Mainband和Sideband 在进行链路初始化和训练需要平衡链路两侧的UCIe Die的速率,达到速率一致性。一般的UCIe Die-to-Die IP 仅支持32>24>16>12>8>4 GT/s 阶梯形态的速率下降。奇异摩尔Kiwi Link Die-to-Die IP 使用精确的速率控制管理仅以0.8Gbps对两侧Die的速率进行微调下降,从而保证Die与Die之间仍旧维持较高的速率通信。

产品验证

我们的IP产品全面经过UCIe 1.1 从物理层合规、Die to Die适配层合规及协议层合规等多个维度进行测试认证包括回环测试/Die-to-Die互连测试/信号质量测试并提供完整真实可靠的测试报告,满足客户所需的IP验证需求。

应用范围

人工智能/智算中心及其他边缘计算用所需大算力扩展的Chiplet芯片互联,不限于GPU、CPU及xPU等。

更多最新产品信息,诚邀您莅临12月11-12日举办的ICCAD 2024,打卡奇异摩尔展位(D63/64),我们的技术专家将为您做1对1的技术讲解。

关于我们

AI网络全栈式互联架构产品及解决方案提供商

奇异摩尔,成立于2021年初,是一家行业领先的AI网络全栈式互联产品及解决方案提供商。公司依托于先进的高性能RDMA 和Chiplet技术,创新性地构建了统一互联架构——Kiwi Fabric,专为超大规模AI计算平台量身打造,以满足其对高性能互联的严苛需求。我们的产品线丰富而全面,涵盖了面向不同层次互联需求的关键产品,如面向北向Scale out网络的AI原生智能网卡、面向南向Scale up网络的GPU片间互联芯粒、以及面向芯片内算力扩展的2.5D/3D IO Die和UCIe Die2Die IP等。这些产品共同构成了全链路互联解决方案,为AI计算提供了坚实的支撑。

奇异摩尔的核心团队汇聚了来自全球半导体行业巨头如NXP、Intel、Broadcom等公司的精英,他们凭借丰富的AI互联产品研发和管理经验,致力于推动技术创新和业务发展。团队拥有超过50个高性能网络及Chiplet量产项目的经验,为公司的产品和服务提供了强有力的技术保障。我们的使命是支持一个更具创造力的芯世界,愿景是让计算变得简单。奇异摩尔以创新为驱动力,技术探索新场景,生态构建新的半导体格局,为高性能AI计算奠定稳固的基石。

-

IP

+关注

关注

5文章

1885浏览量

156789 -

chiplet

+关注

关注

6文章

499浏览量

13655 -

奇异摩尔

+关注

关注

0文章

85浏览量

4075

原文标题:Kiwi Link 32GT/s UCIe 1.1 Die-to-Die IP 全新上市,诚邀莅临ICCAD 展位了解更多

文章出处:【微信号:奇异摩尔,微信公众号:奇异摩尔】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

奇异摩尔与图灵量子达成深度战略合作

高频高侧/低侧驱动器UCC27201A-DIE:性能与应用解析

TPS7A4001-DIE:超高耐压线性稳压器的特性与应用解析

UC1843A - DIE:电流模式PWM控制器的卓越之选

探秘UC1834-DIE:高效线性稳压器的卓越之选

探索 OPA857-DIE 超低噪声跨阻放大器:性能、应用与设计要点

THS4541-DIE:高性能全差分放大器的设计与应用

高频N沟道MOSFET驱动器UCC27201A - DIE的深度解析

Cadence基于台积电N4工艺交付16GT/s UCIe Gen1 IP

晶圆制造中的Die是什么

DAF胶膜(Die Attach Film)详解

奇异摩尔Die-to-Die片内互联方案持续升级

新思科技UCIe IP解决方案实现片上网络互连

奇异摩尔荣获2025中国创新IC强芯-创新突破奖,助力国产化芯片技术突破

奇异摩尔32GT/s Kiwi Link Die-to-Die IP全面上市

奇异摩尔32GT/s Kiwi Link Die-to-Die IP全面上市

评论