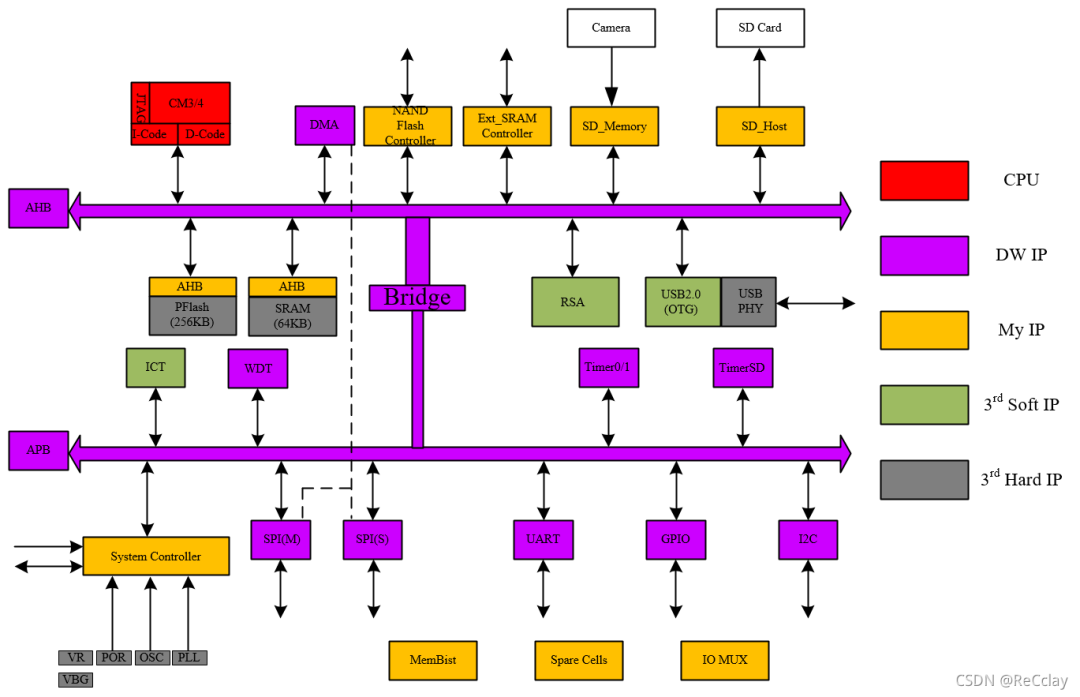

一、SoC 架构图:核心功能和设计目标

SoC 是基于通用处理器这样的思路进行设计的,与 PC 设计思路一样。即通用处理器是由 CORE + MEM 两部分组成,修改软件来实现不同的功能,电脑还是同一个电脑,硬件组成还都是一样的。 SoC 架构图四大组成部分:

1、核 CORE

2、存储 MEM

3、外设 IO

4、总线 BUS

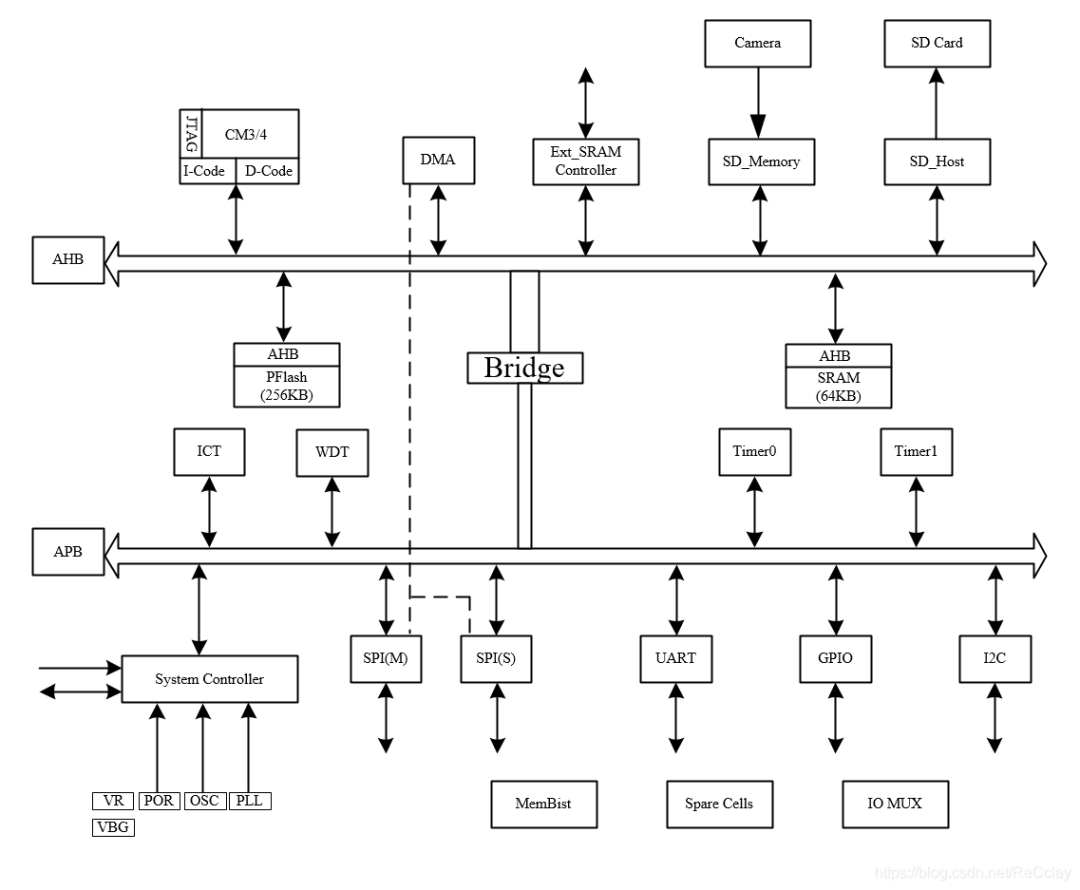

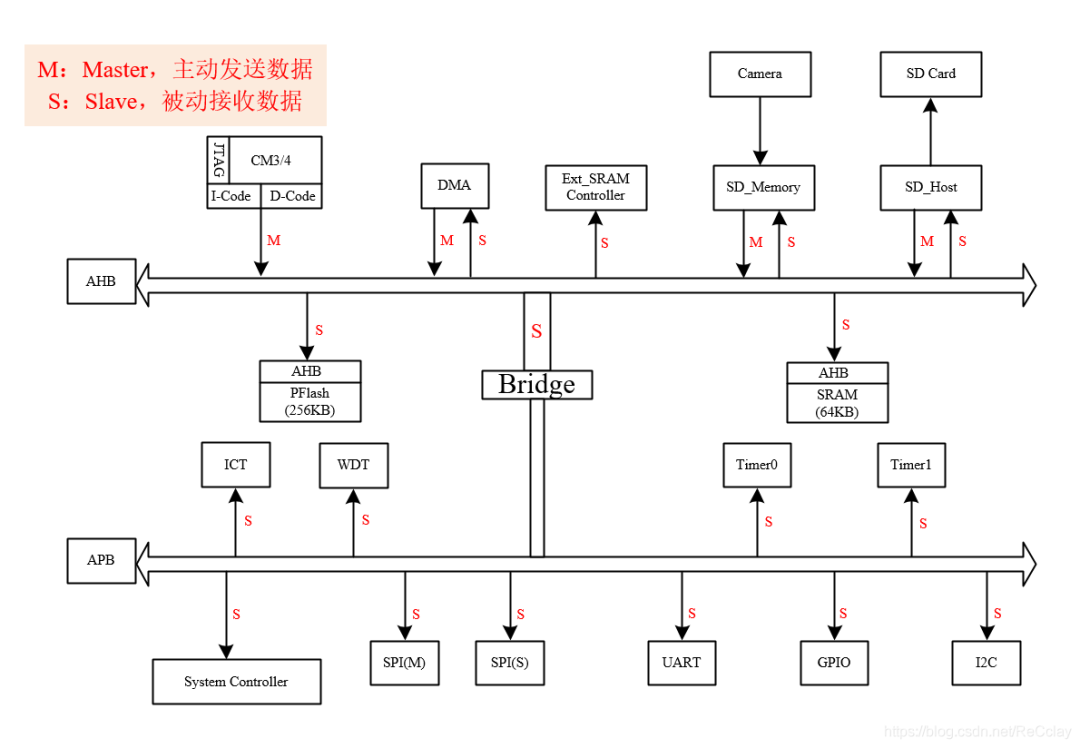

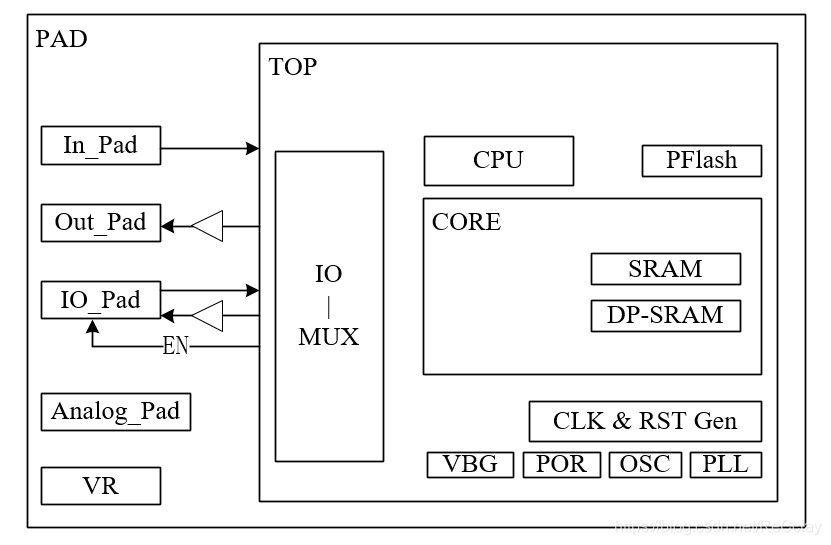

SoC 总的架构图如下:

1.1、SoC - 核 CORE对于核来讲,现在主流的核有三类:

x86 为代表,公司有 AMD 和 INTEL,PC 和 Server 用这类核比较多。

ARM-R 系列:中端,常用在实时场景,如医疗器械,路由交换机

ARM-A 系列:高端,常用在高端应用场景,如手机芯片

ARM 为代表,手机芯片、嵌入式系统等用这类核比较多。

CISC(Complex Instruction Set Computer - 复杂指令集计算机)

RISC(Reduced Instruction Set Computing - 精简指令集计算机)

基于 ARM 和 x86 之间,可以进行灵活的切换和组装

暂没有成熟的商用体系,没有生态支撑

RISC-V(开源)

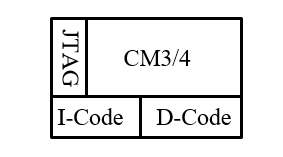

架构图,左上角为 SoC 系统的核,此处使用的是 ARM 公司的 Cortex-M3/M4 内核。

同时,I-Code 表示指令代码,D-Code 表示数据代码。JTAG 用来调试芯片,下载调试程序使用。

注:I-Code、D-Code 即 I-Cache、D-Cache,这个可选的,并不是每个 SoC 都会用到,需要根据实际芯片的规模和需求!

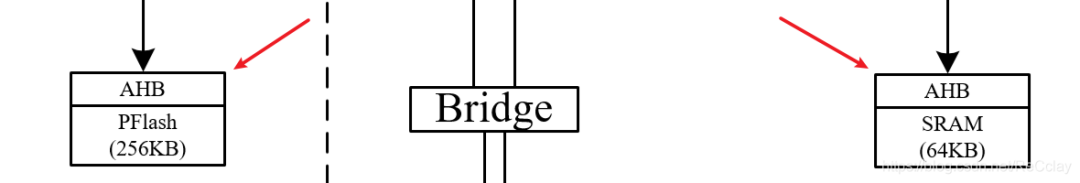

1.2、SoC - 存储 MEM架构图,中间部分为 SoC 系统的存储,此处包含 PFlash 和 SRAM 两种。

如果 PFlash 不够用,可以外扩 Flash,如NFC(Nand Flash Controller)

SRAM 是静态随机存储器(Static Random Acess Memory),与之相对的还有一种是动态随机存储器(Dynamic Random Acess Memory)。DRAM 需要不断的刷新才能保持住数据,SRAM 是不需要刷新的!

DRAM 的密度很高,所以当存储数据容量很大的时候组出来的 Memory 面积就会小一些!SRAM 通常用在小的 SoC 中!

如果 SRAM 不够用,可以外扩 SRAM,比如上图中的Ext_SRAM

PFlash(硬盘)中的数据掉电不丢失

SRAM(内存)中的数据掉电丢

即 BootLoader 放在 PFlash 中,一上电便会将其 load 至 SRAM 中,CPU 来 SRAM 取指来执行我们的程序!

core 上电后,会到 PFlash 中取它的指令,来读取系统要运行的 “软件”(代码),在 PFlash 启动之后,把所需的软件下载至 SRAM 中,最终在 SRAM 里运行 “软件”。

SRAM 存储速率较 PFlash 速率快,故上电跑的程序是放在 SRAM 中,启动程序以及不需要的数据会存在 PFlash 中。

1.3、SoC - 外设 IO外设 IO 分为两部分:

一个是高速外设 IO(AHB 100MHz):DMA、Ext_SRAM Controller、SD_Memory、SD_Host

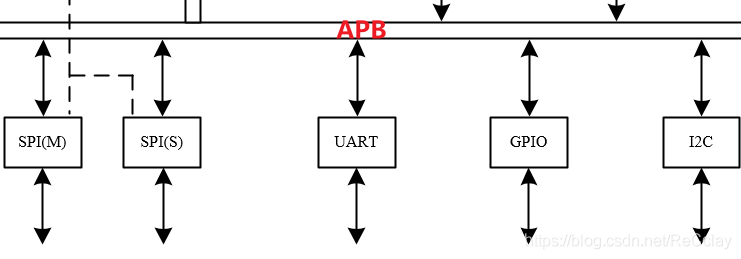

一个是低速外设 IO(APB 50MHz):SPI、UART、GPIO、I2C

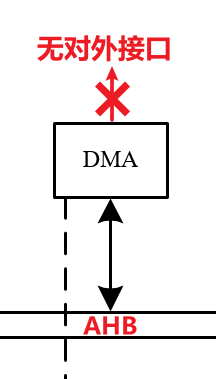

1.3.1、 DMADMA(Direct Memory Access,直接存储器访问),使用场景如下:当 CPU 需要搬移 SRAM 中的大量数据时,此时如果使用 CPU 搬移,则会先将 SRAM 中的数据搬移至 CPU 的寄存器中,然后再取指令写操作等方式搬移至目的地。该方法效率较低,且占用了 CPU 的宝贵处理时间。此时就有了 DMA 的登场,CPU 只需告诉 DMA 引擎,你需要从哪个地址搬移多少个数据到哪个地址,这样 DMA 就自己听话地去工作了,不再需要 CPU 的参与,减轻 CPU 的负荷。 DMA 对外没有接口,这个也可以从架构图中看出。

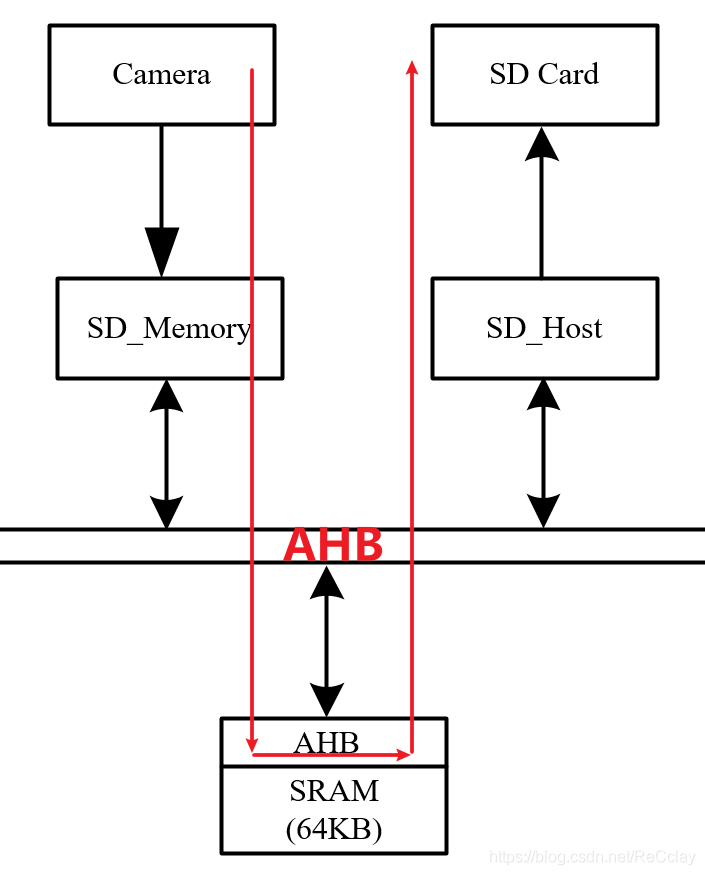

1.3.2、 Ext_SRAM Controller、SD_Memory 与 SD_HostExt_SRAM Controller:通常是 SRAM 大小不够时,用作扩展使用。 通常 SD_Memory 连接一个诸如 Camera 的设备,将拍到的照片数据通过 SD_Memory 接口存储到 SRAM 中,然后 SD_Host 接口将 SRAM 中的数据保存至 SD Card 中,取出 SD 卡插入 PC,就可以看到读取的照片了!

1.3.3、典型低速外设典型的 3 个低速外设接口:I2C、UART、SPI,差异如下:

UART 常用于长距离传输,但是速率较低。

I2C 比 UART 速率快,但是速率不会太长;且 I2C 在短距离传输时,可以接多个 Slave。UART 是点点通信,1 个 UART 接口只能接 1 个 UART Slave。1 个 I2C Master 接口,可以接多个 I2C Slave;

SPI 相较于 UART 和 I2C 速度会更高;1 个 SPI Master 接口,可以接多个 SPI Slave;SPI 占用的 IO 数也较 I2C 多!

外设与 CPU 进行通信,有两种方式:

CPU 来查询我们的状态

直接给 CPU 发送中断,CPU 收到中断后会去处理中断程序

BootLoader 程序和中断程序是事先写好的程序,放到 FLASH 中,一旦启动后便会将其 LOAD 至 SRAM 中!一旦发生某个中断,便会根据中断向量号去查询中断程序去执行它。(了解即可)

注:主动发起数据我们称之为 master;被动接受数据我们称之为 slave。

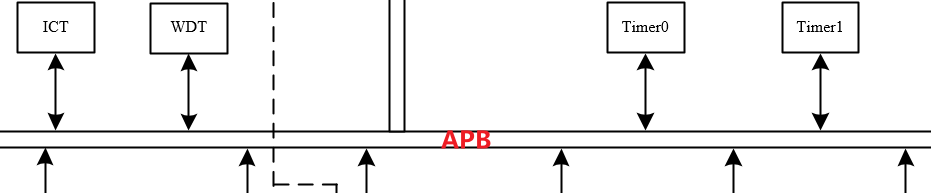

1.3.4、内部组件WDT:看门狗。我们的内核每隔一段时间喂一次狗,如果内核挂掉,看门狗溢出会产生一个中断,告诉外界,芯片已经挂死,需要处理。 Timerx:硬件计数器。CPU计数精读低,通常是 us 级,很难达到 ns 级。而我们的硬件计数器精度可以达到 ns 级别;另外,硬件计数,可以减小 CPU 的开销。 ICT:指令的计数,统计用的!

System Controller:系统控制器

POR:Power On Reset,上电复位(模拟 IP)

OSC:Oscillator,晶振

PLL:Phase Locked Loop,锁相环

VBG:电源管理

VR:Voltage Regulater,电压调节器

上述讲的 IO 小模块,以及本节介绍的模拟组件,我们一般都称之为IP。

1.4、SoC - 总线 BUS将上述介绍的 IP 进行互联的线,我们将其称之为总线。这里使用的是 AMBA 2.0 总线,包括 AHB、APB 两部分。

1.5、其他模块

1.5.1、MemBistMemBist 主要针对 Memory,如 SRAM。在制造过程中,可能会存在缺陷,当芯片回来之后,我们要进行一些制造型测试!MemBist 是进行内建自测试! 这种内建自测试与其他 IP 外设测试不一样,其他 IP 外设测试通常是通过 GPIO 灌激励,然后将经过这些逻辑之后的激励通过另外一些 GPIO 引出,然后去对比 Partner。而内建自测试是我这个测试,对 SRAM 的测试不需要通过外部的管脚,在 SRAM 外部会包一层 Bist 逻辑,然后相当于在内部触发一个使能信号,然后它就可以往 SRAM 中灌各种激励,然后把经过逻辑之后的激励输出,就可以完成这样一个内建自测试。这就是 MemBist 的功能。

1.5.1、Spare CellsSpare Cells 主要是放在顶层,用于芯片后期,在投片时忽然发现有 BUG,这时候要做一个叫 ECO(Engineering Change Order,手动修改集成电路的过程)的东西,这个时候就可能会涉及到一些 cell 的替换,如果之前已经放了 Spare Cells 的话,就可以直接用 Spare Cells,不需要再重新增加 cell。如果增加 cells,可能会导致整个 Die 的面积放不下!所以相当于是提前预留放了一些为我们做 ECO 准备的 Spare Cells,把面积在那占着,这样的话,整个 FloorPlan 就不用了动了!Cell 在那放着,尽可能最小的去影响我们最终的 FloorPlan。

1.5.1、IO MUX管脚复用,类比 STM32。

1.6、SoC IP

二、SoC 架构图:简述 SoC 的功能及应用场景

这种应用在记者、摄影爱好者,数码相机爱好者等有应用需求。当把数码相机中的图片下载到手机上后,可以通过移动网络,上传至社交媒体;现场记者,则可以通过将照片及时发送给电视台、媒体等提供及时的照片素材。

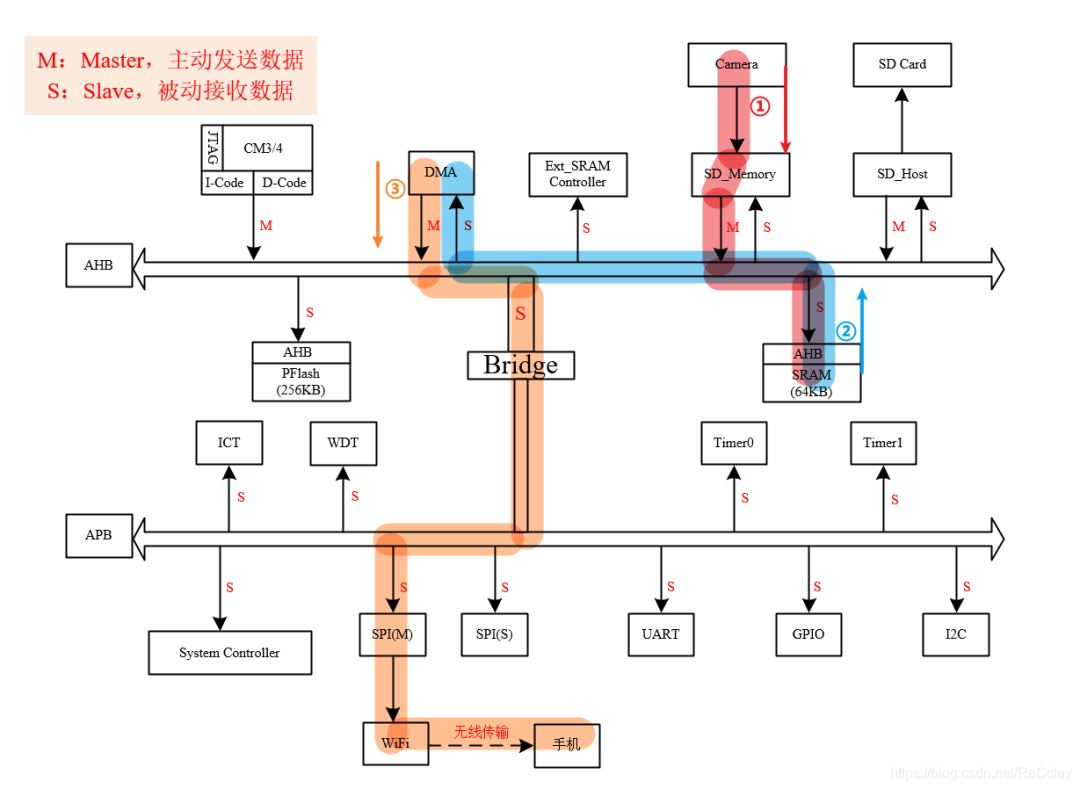

无线通信功能是通过 APB 总线上的 SPI 接口外接一个 WIFI 芯片,实现无线通信和数据传输功能。

数据存储功能主要是 NandFlash 控制器,实现存储功能。但是该芯片采用了替换方案,使用了 SD-Host 接口,外接 SD Card 的方式进行存储数据。

典型的应用场景是:数码相机拍照时,将照片通过 SD-Memory 控制器接口,放入 SRAM 暂存,最后通过 SD Host 接口,将照片存储到外接的 SD memory 卡中,然后手机 / PC 端用户,可以连接到 WiFi 上,通过手机 / PC 下载 SD Card 中存放的视频到手机 / PC。

该芯片是一个 SoC 芯片,主要功能是无线通信和数据存储功能,主要的应用场景是数据相机的存储卡。

随着智能手机的发展,尤其是高清摄像头的发展,这种无线存储芯片方案的应用场景在萎缩。

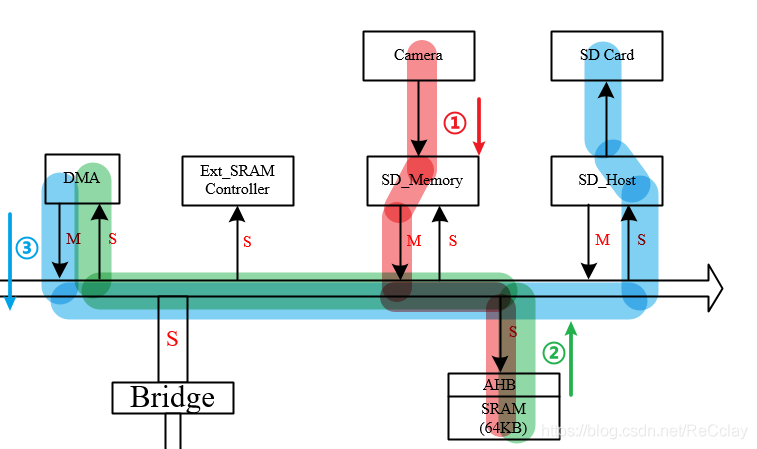

2.1、数据存储 数据流数据存储功能的数据流向示意图(以 DMA 搬移 SRAM 数据为例):数据流按照箭头,依次是:红 -> 绿 -> 蓝。(下图标号所在位置是该颜色起始位置)

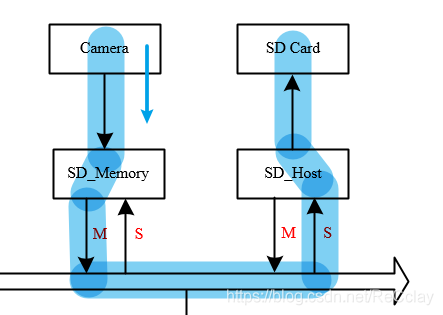

问:为什么不直接从 Camera -> SD Card?如下图:

答:数据通路是可以通的,但是 Camera 发送数据的速率与 SD Card 存储数据的速率,这两个并不一定是完全一样的,这样就可能导致数据错误。将数据存入 SRAM,相当于起一个缓冲的作用!这样我数据存进来之后,是存至 SD Card 还是通过 WiFi 进行无线传输,都可以通过 CPU 进行灵活控制!

2.2、无线传输 数据流无线传输功能的数据流向示意图(以 DMA 搬移 SRAM 数据为例):数据流按照箭头,依次是:红 -> 蓝 -> 棕。(下图标号所在位置是该颜色起始位置)

2.3、关于 Master 和 Slave

CPU 通常是一个 Master,数据的发起者;

存储系统(PFlash、SRAM)是一个 Slave,被动的接收别人发过来的命令,要来读哪个地址的数据了;

两个 AHB 高速外设:SD_Memeory 和 SD_Host。既有 Master 口,又有 Slave 口。SD_Memory 模块工作时,数据是通过 Master 口进行传输,Slave 口更多指的是 CPU 对其进行一些配置(IP 可以工作在多种模式,控制信号可以通过 Slave 口对其进行配置);SD_Host 模块同理。

慢速外设:SPI/UART/GPIO/I2C/Timer/WDT/ICT 等,都是 Slave 口,是 CPU 来告诉他们要传什么数据出去(CPU 对其进行配置)。

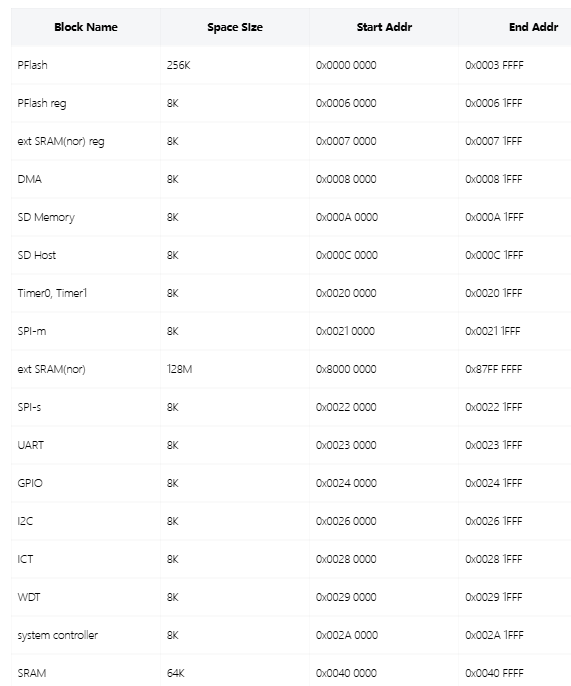

三、SoC 架构图:IP 总线地址映射基地址:Base Address偏移地址:Offset Address

注:基地址 + 偏移地址 可类比 区号 + 号码。低 16 位是偏移地址,高 16 位是基地址。

每一次的访问都是基于地址空间进行访问的,所以会把每一个系统进行划分,划分成为一个地址空间。 各个外设地址如下表:

软件工程师写模块时,通常只关注偏移地址!

一般一个地址空间可以存储 8bit 数据,故上述单位是KB

四、SoC 架构图:Pin-MUX & PAD

①、PAD 本身就挺大的,PAD 过多,很占边长,造成规划的 Die 放不下。【芯片外围边长留足够的余量】

②、PAD 本身是模拟器件,PAD 过多,会增加功耗!【总体功耗也会有收益】

PAD:芯片与外部通信的一个接口

PIN-MUX:主要用来减少 PAD 数目,为什么要减少 PAD?

上图展示的三种数字PAD,从上到下分别是:Input Only、Output Only、Bidirection 三种。工程上通常上都是 Bidirection ,使用的时候直接控制 EN 信号,来使其输入或输出!

模拟 PAD:如 LVDS;

VR(电压调节器) PAD

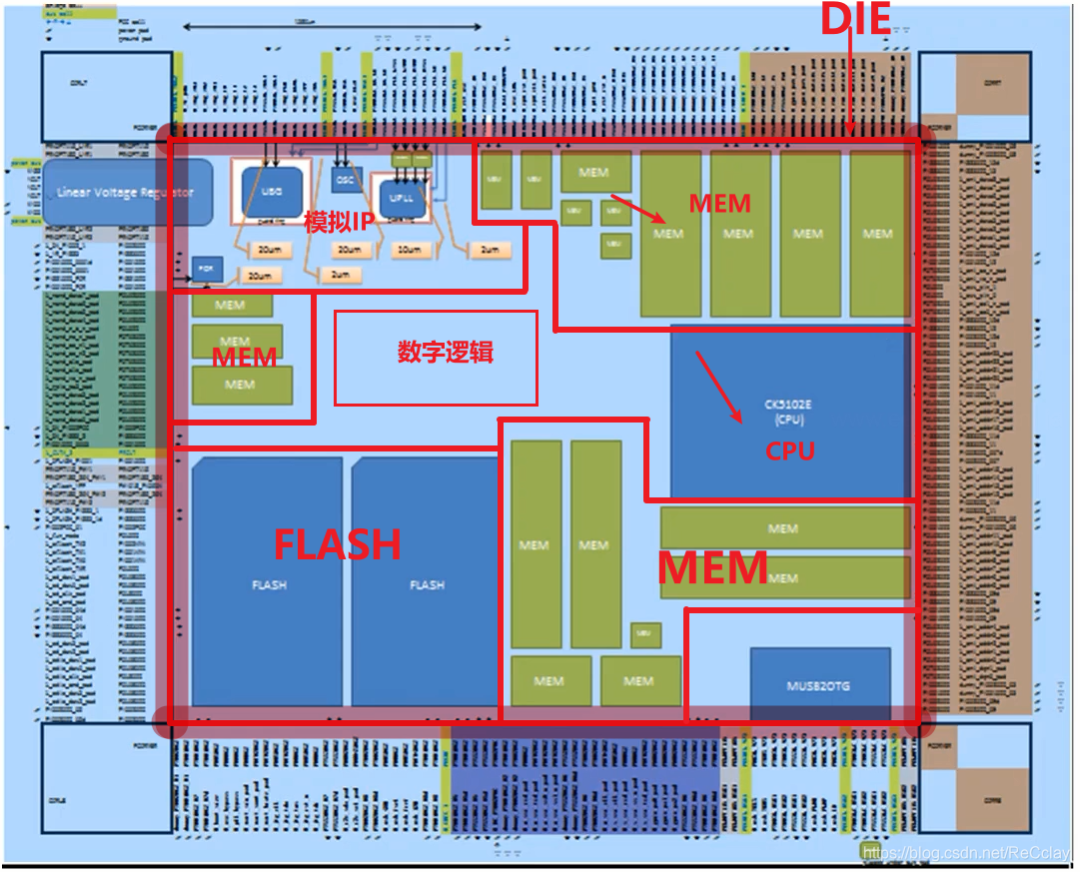

五、SoC 架构图:版图布局 Floorplan

注:版图布局 Floorplan 布局可类比 PCB 的布局!

Floorplan 中可以看到的是各个 Cell(数字电路)和各个 IP(模拟电路)。

模拟IP (MEM/FLASH)放到靠近 DIE 的边角上,提高空间利用率

DIE 的内部会放数字逻辑

这样的放置原则是为了提高整个空间的利用率!MEM 这个模拟 IP,可以认为是一个硬核,如果它放中间,那么周围的绕线就会很麻烦。如果是数字的话,那就是各个离散的 Cell,走线容易,空间利用率高!

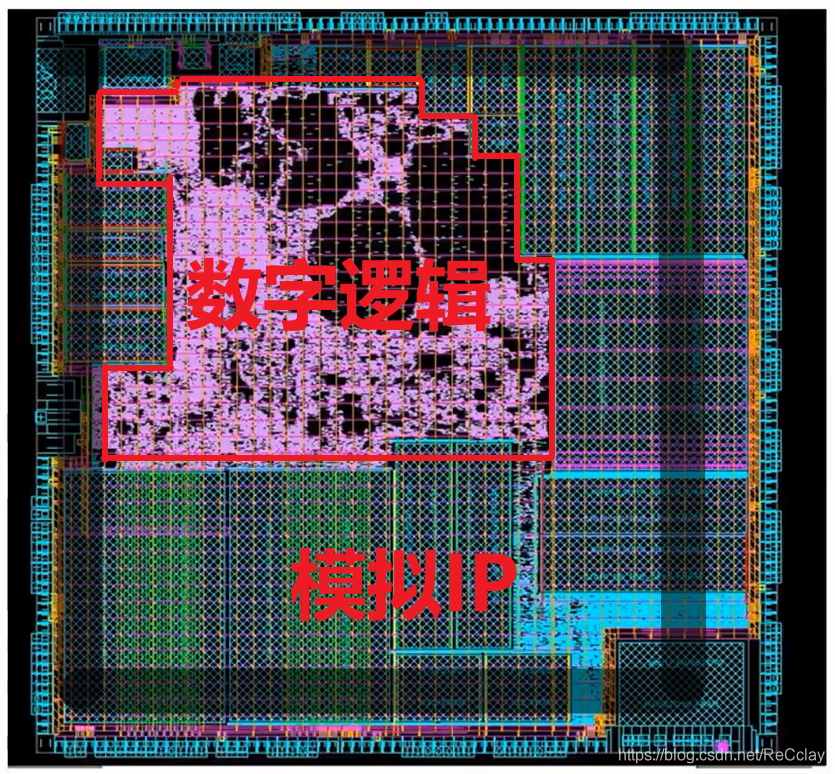

六、SoC 架构图:版图 layout - GDSII

注:版图 layout 可类比 PCB 的布线!

下面的版图 layout 中,中间紫色部分的就是对应 Floorplan 中标注的数字逻辑部分,周围靠近 Die 的就是模拟 IP!

工艺水平:110nm e-flash

DIE 大小:3mm x 4mm = 12 mm^2

晶圆 wafer 大小:8 英寸,可以生成 3600 片 DIE(3mm x 4mm),1 个 wafer 的制造成本在 1000 美金。

良率(yield)【wafer 中有多少个 DIE 是可用的】:>95%(通过 ATE 去筛选不能用的 DIE)

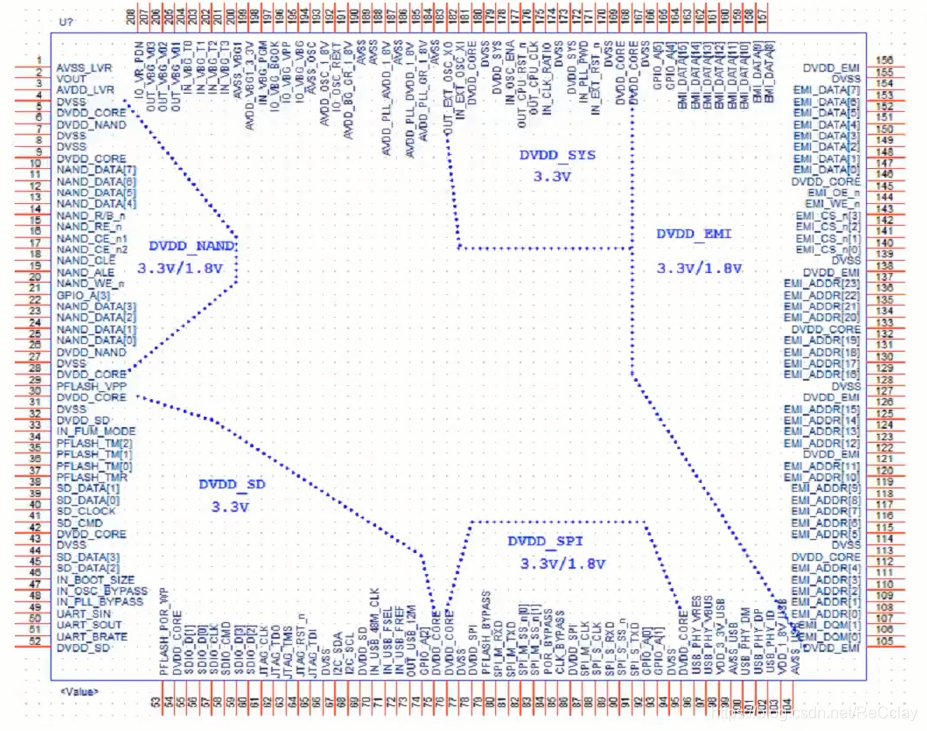

六、SoC 架构图:Pin & 电源电压下图为外围的原理图,从中可以看到管脚分布和电压域划分。

电压域的划分工作通常由架构师完成,前端人员是接触不到这个东西的!

电压域通常可划分为:数字电压域(CORE、IO)、模拟电压域(不同模拟 IP,不同的电压)

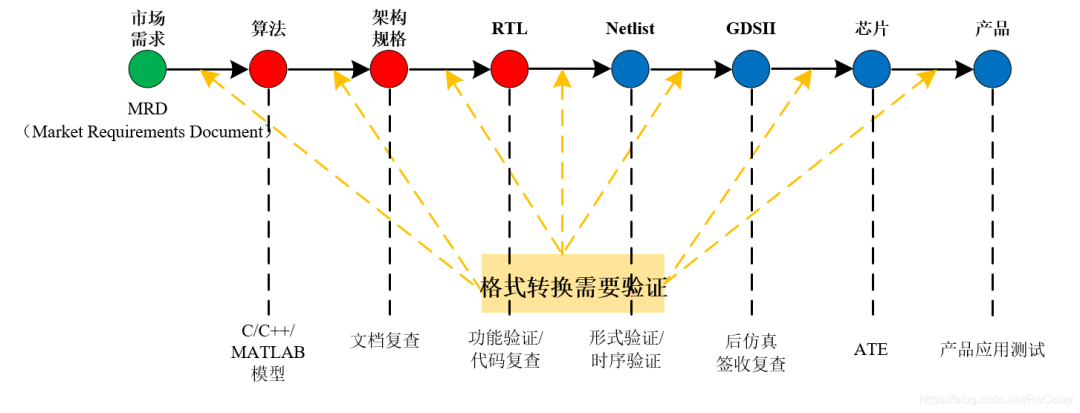

七、数字系统设计节点(SoC Design Node)芯片的诞生,从前期到后期的整个流程:

①、进行市场调研,有没有市场需求,具不具备很好的商业价值,做芯片很烧钱,1 个 wafer1w 美金,还要买一些 IP 等都要花钱!做出来之后能否赚钱,有没有人买单,这个很重要!

②、根据市场需求,算法团队根据要实现的功能,做一个算法模型,算法可以实现(仿真成功),可以达到市场需求,则进行下一步。

③、进行芯片的实现架构设计,包括:软硬件划分(哪些部分用软件实现,哪些部分用硬件实现)、硬件上划分多少个模块等,编写架构文档(AS,Architecture Specification),架构也分为好多层次,比如系统级,电路级等。接下来还有编写一个设计文档(DS,Design Specification)

④、编写 RTL 代码,进行功能验证(EDA 仿真验证、FPGA 原型验证)和代码复查

⑤、通过综合工具,将其转化为 Netlist,即将 RTL 代码映射(MAP)成门级网表(STD CELL),同时进行形式验证(RTL 逻辑功能和 Netlist 的逻辑功能对比,看看综合工具是否把 RTL 某些功能给优化掉),时序验证(实现 Netlist 后,timing setup 能否满足)

⑥、接下来进行物理实现,GDSII 也是一个网表,只不过是包含了器件位置信息的网表。Netlist 仅仅只是逻辑信息。然后进行一些后仿真和签收复查。

⑦、投片,在 wafer 上生成我们的芯片。生产过程有没有问题,通过 ATE 测试,ATE 测试的 partner 是在前面做 RTL 时的 DFx 做的,Membist,Scan 扫描,都是在前期做好的设计,芯片回来之后,会把这些电路启动,进行 ATE 测试!测芯片本身,有没有制造功能的问题!

⑧、最后进行应用测试,即功能测试。投放市场。

从上图看出

①、芯片的实现是需要很多的团队,很多个环节,一步步实现的。

②、每一个环节的交付件(交付标准)是变化的,每一步都是需要有不同的方法验证。做 IC 验证,主要进行 RTL 的功能验证,要明确从事的工作在整个设计流程中的位置!

参考文献

芯片测试术语 ,片内测试 (BIST),ATE 测试

-

sram

+关注

关注

6文章

833浏览量

117718 -

soc

+关注

关注

40文章

4622浏览量

230159 -

通用处理器

+关注

关注

0文章

15浏览量

7290

原文标题:了解 SoC 的架构

文章出处:【微信号:Ithingedu,微信公众号:安芯教育科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文看懂:线束接头气密性试验仪工作原理

新思科技EDA工具和车规IP助力芯粒架构汽车SoC设计

RK3576 能否替代 RK3588?一文看懂 6TOPS 工业 AI SoC 的真实性能差距与选型逻辑

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

高集成度、全数字化架构!SPAD-SoC优势和技术路线

人脸识别和AES加密协同的SOC设计架构

主流厂商揭秘下一代无线SoC:AI加速、内存加量、新电源架构等

一文看懂芯片的设计流程

高通SoC阵列服务器

SoC集群服务器 与 ARM架构阵列服务器 关系

一文看懂SoC的架构

一文看懂SoC的架构

评论