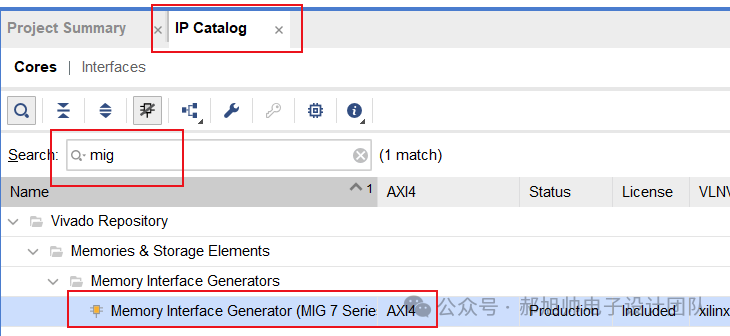

本篇主要讨论Vivado中DDRX控制器(mig)ip核配置中关于命令序号选择和地址映射说明(一)

利用Xilinx 7系列FPGA开发时,经常需要驱动外部存储器--DDRX。Xilinx提供了mig(存储器接口生成器)这个ip用以驱动外部存储器。

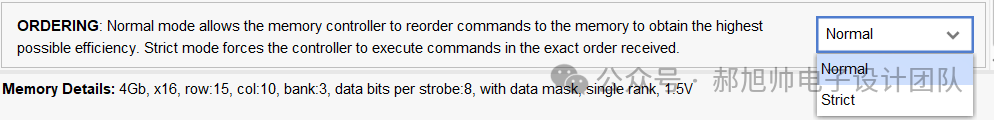

在配置中有一项命令序号模式的选择:

mig这个ip可以接收多个命令(在第一个命令还没有执行时,就可以接收后续的几个命令。并不是接收一个命令,执行完后才可以接收下一个命令)。

上述选择两个模式的区别为:

正常模式允许存储器控制器重新编序收到的命令的顺序,以或者更高的性能(例:收到的命令顺序为A1,A2,A3,但是发现按照A1,A3,A2的顺序执行,不妨碍功能,并且拥有更高的性能)。

严格模式强制要求控制器按照收到的命令顺序去执行。

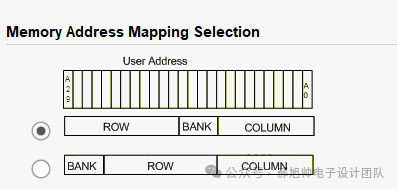

在配置时,还有一项地址映射模式选择:

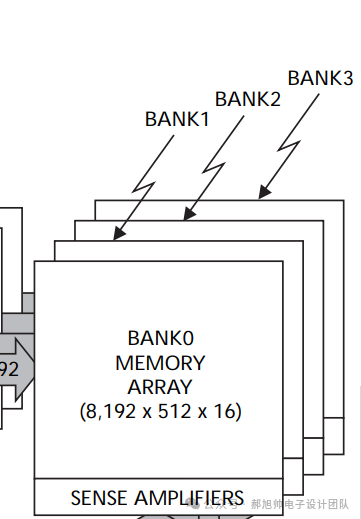

DDRXSDRAM是一种按照M行,N列凑成一个片(BANK),然后多个片构成的一个存储器。在使用时需要提供BANK地址,行地址,列地址,才能够指定对应的访问位置(特别注意:每个位置存储一个字(需要看存储器的宽度),并不是一个字节(8个bit))。

注:此图为SDR SDRAM的内部结构图,只为方便理解。

在使用mig时,我们需要提供一个地址,那么这个地址的各个位对应的DDRX SDRAM的bank地址,行地址,列地址的模式是按照上述选择的。

例:(不考虑RANK地址),假设行地址13位,列地址10位,BANK地址3位,无论我们选择哪一种模式,我们的地址都是给一个26位的地址。如果选择ROW,BANK,COL的模式,那么地址的25:13位会给到行地址,12:10会给到BANK地址,9:0会给到列地址。如果选择BANK,ROW,COL的模式,那么地址的25:23位会给到BANK地址,22:10会给到行地址,9:0会给到列地址。

那么这两个地方我们应该选择哪个呢?

这个和内部结构以及工作原理有关系,并且也和我们平时使用的方式 有一定的关系。

内部结构在上述已经简单的叙述过了,下面简述一下工作原理:

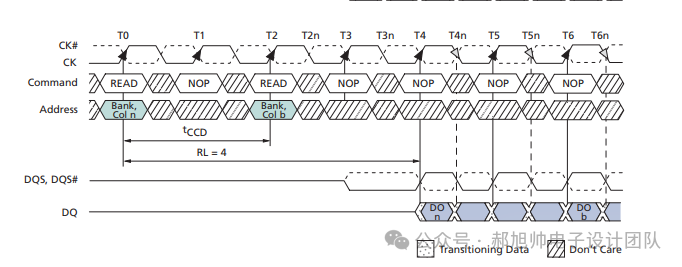

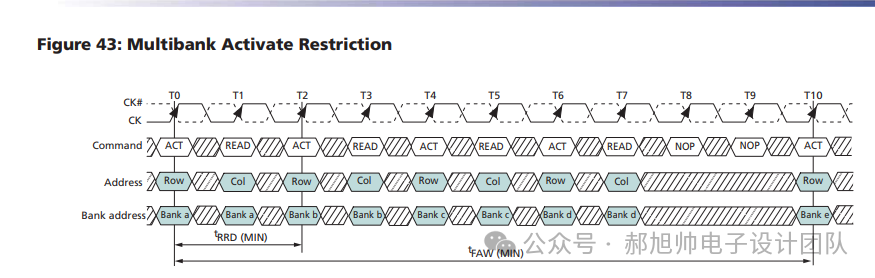

在访问时,我们首先需要激活访问地址对应的BANK里面的对应的那一行,然后才可以进行读写。

下面给出SDRAM中的几个特性:

· 在SDRAM中某一行激活了,是需要关闭的(有时间的限制)。

·在SDRAM中如果第二个操作和第一个操作是同一个bank,同一行,那么第一个操作完成后,可以不关闭此行,第二个操作也不用激活,此时提高了访问效率。

. 在SDRAM中同一个BANK只能激活一行。例:如果第二个操作和第一个操作是同一个bank,但是不同行,那么就只能将第一个操作的行关闭,然后再将第二个行激活。

. 在SDRAM中,不同的BANK是可以同时激活使用者想要访问的行。例:如果第二个操作和第一个操作不在同一个bank,那么就可以在关闭第一个操作对应的bank的同时,激活第二个操作对应的BANK,那么此时相当于节省了一段时间,提高了访问的效率。

知道了这几个特性,我们来考虑上述的两个选择项的问题:

首先考虑命令是否允许重新编号;假设第一个操作为BANK A,ROW A,第二个操作为BANK A, ROW B, 第三个操作为BANK A, ROW A。如果按照严格顺序执行,那么只能够进行激活、操作一,关闭,激活、操作二、关闭、激活、操作三、关闭。共需要九步完成所有的命令。如果把操作二和操作三对调,那么将执行激活、操作一、操作三、关闭、激活、操作二、关闭。共需要七步即可完成,提高了一定的效率,所以此选项建议选择正常模式。

下面考虑地址映射的选项:

这个需要考虑一个使用者的方式:一般我们使用时,是一段连续的地址;例:0到10000。

如果选择BANK,ROW,COL的模式,就是利用第一个bank的第一行,然后第二行,第三行,········, 直到第一个bank利用完毕,才可以利用下一个bank。

如果选择ROW,BANK,COL的模式,就是利用第一个bank的第一行,完事后,利用第二个bank的第一行,然后是第三个bank的第一行····直到所有的bank的第一行全部利用完事后,才会利用第二行。

那么在当一行利用完毕时,BANK,ROW,COL的模式下一个用的是第二行就必须等第一行关闭后,才可以激活第二行。如果选择ROW,BANK,COL的模式下一个用的是其他的bank的行,所以不需要等待关闭就可以激活,相当于节省了一段时间,提高了访问效率。

-

FPGA

+关注

关注

1664文章

22502浏览量

639207 -

控制器

+关注

关注

114文章

17877浏览量

195117 -

地址映射

+关注

关注

0文章

6浏览量

2250

原文标题:Vivado中DDRX控制器(mig)ip核配置中关于命令序号选择和地址映射说明(一)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

组态屏变量地址映射 / 数据类型不匹配解决方法

DDRX SDRAM中的预取技术说明

利用蜂鸟E203搭建SoC【4】——DDR200T内存扩展

E203分享之DDR扩展方案实施流程(中)

Vivado浮点数IP核的一些设置注意点

基于FPGA的DDR控制器设计

FPGA搭建DDR控制模块

用FPGA实现DDR控制模块介绍

Zynq-7000 SoC与7系列设备内存接口解决方案数据手册

EtherNet IP转Profinet网关连接FANUC机器人配置指南(PROFIENT组态篇)

Vivado中DDRX控制器(mig)ip核配置中关于命令序号选择和地址映射说明

Vivado中DDRX控制器(mig)ip核配置中关于命令序号选择和地址映射说明

评论