PCIe(Peripheral Component Interconnect Express)信号完整性问题可能导致数据传输错误、系统不稳定甚至完全失效。以下是一些针对PCIe信号完整性问题的解决方案:

一、检查和优化硬件连接

- 确保连接器和插槽正确接触 :

- 检查PCIe设备(如显卡、固态硬盘等)与主板上的PCIe插槽之间的连接是否牢固,确保所有连接器都正确插入且没有物理损伤。

- 使用高质量的材料和工艺 :

- 选择高质量的PCIe插槽和连接器,确保它们具有良好的导电性和耐久性。

- 使用高质量的电路板材料,以减少信号路径上的阻抗不匹配和信号损失。

- 优化线路布局和设计 :

- 分析线路布局和设计,确保信号路径适合高速操作。

- 如果可能,缩短信号路径,以减少信号衰减和干扰。

- 避免高速信号走线并行,以减少串扰。

二、电源管理和噪声抑制

- 检查电源供应是否稳定 :

- 使用电源分析仪测量供电线路的噪声,确保电源供应稳定且没有过多的噪声干扰。

- 使用电源滤波器 :

- 在电源输入端添加电源滤波器,以抑制电源噪声和干扰。

- 确保设备在推荐的温度范围内操作 :

- 高温可能导致设备性能下降和信号质量恶化,因此应确保设备在推荐的工作温度范围内操作。

三、信号再生和补偿

- 使用Retimer芯片 :

- Retimer芯片通过对信号的重定时和均衡,可以恢复衰减信号的幅度和质量,从而减小信号失真。

- Retimer还能够补偿链路插损,延长传输距离,确保数据传输的稳定性、完整性和低延迟表现。

- 优化端接和电路设计 :

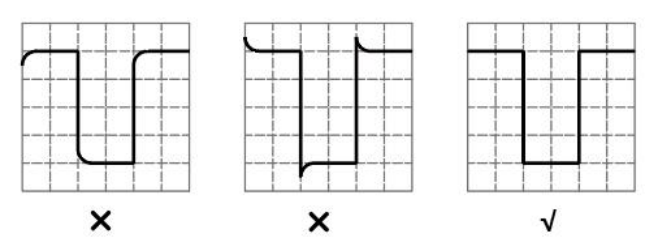

- 采用适当的端接方式(如片内端接On Die Termination,简称ODT),以消除信号反射。

- 优化电路设计,以减少电源噪声和串扰对信号质量的影响。

四、软件配置和更新

- 检查BIOS或固件设置 :

- 确保BIOS或固件设置正确,PCIe插槽已启用。

- 检查是否有与PCIe设备相关的配置错误或冲突,并进行必要的调整。

- 更新驱动程序和固件 :

- 确保PCIe设备的驱动程序和固件是最新版本,以兼容最新的操作系统和硬件。

- 驱动程序和固件的更新可以解决一些与硬件兼容性和性能相关的问题。

五、故障排除和诊断

- 使用TDR(时域反射仪)检查阻抗匹配情况 :

- TDR可以帮助识别信号路径上的阻抗不匹配点,从而指导解决阻抗不匹配问题。

- 进行误码率测试 :

- 使用测试设备对PCIe信号进行误码率测试,确保误码率在可接受范围内。

- 如果误码率超标,应进一步排查信号完整性问题。

- 检查时钟同步 :

- 确保时钟源准确、无漂移,并且与所有设备同步。

- 时钟同步问题可能导致数据传输错误和信号完整性问题。

综上所述,解决PCIe信号完整性问题需要从硬件连接、电源管理、信号再生和补偿、软件配置以及故障排除和诊断等多个方面入手。通过综合运用这些解决方案,可以显著提高PCIe信号的稳定性和可靠性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

连接器

+关注

关注

105文章

16357浏览量

147860 -

数据传输

+关注

关注

9文章

2226浏览量

67726 -

信号完整性

+关注

关注

68文章

1497浏览量

98237 -

PCIe

+关注

关注

16文章

1477浏览量

88906

发布评论请先 登录

相关推荐

热点推荐

IDT信号完整性产品:解决高速信号传输难题

特性的影响,到达终端接收器时可能会恶化到不可接受的水平。Integrated Device Technology(IDT)的信号完整性产品(SIP)系列,包括中继器(Repeaters)和重定时器(Retimers),为解决这些问题提供了有效的

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

一、应用背景 在现代电子设备架构中,PCIe、USB 3.0等高速数字总线是实现数据高速传输的核心载体,其信号完整性测试已成为保障设备性能稳定性与运行可靠性的关键环节。随着数据传输速率的持续攀升

Cadence工具如何解决芯粒设计中的信号完整性挑战

在芯粒设计中,维持良好的信号完整性是最关键的考量因素之一。随着芯片制造商不断突破性能与微型化的极限,确保组件间信号的纯净性与可靠性面临着前所未有的巨大挑战。对于需要应对信号

技术资讯 I 信号完整性与阻抗匹配的关系

本文要点PCB走线和IC走线中的阻抗控制主要着眼于预防反射。防止互连路径上发生反射,可确保功率传输至负载,同时避免其他信号完整性问题。使用集成场求解器的PCB设计软件可以评估阻抗匹配并提取互连网

深圳 9月12-13日《信号完整性--系统设计及案例分析》公开课,即将开课!

涉及信号完整性问题。仿真或者guideline的确可以解决部分问题,但无法覆盖全部风险点,对高危风险点失去控制经常导致设计失败,保证设计成功需要系统化的设计方法。

了解信号完整性的基本原理

作者:Cece Chen 投稿人:DigiKey 北美编辑 随着支持人工智能 (AI) 的高性能数据中心的兴起,信号完整性 (SI) 变得至关重要,这样才能以更高的速度传输海量数据。为确保信号

上海 6月20-21日《信号完整性--系统设计及案例分析》公开课,即将开课!

涉及信号完整性问题。仿真或者guideline的确可以解决部分问题,但无法覆盖全部风险点,对高危风险点失去控制经常导致设计失败,保证设计成功需要系统化的设计方法。

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

前言 在这一期的Samtec虎家大咖说节目中,Samtec信号完整性(SI)和电源完整性(PI)专家Scott McMorrow、Rich Mellitz和Istvan Novak回答了观众的提问

发表于 05-14 14:52

•1244次阅读

受控阻抗布线技术确保信号完整性

核心要点受控阻抗布线通过匹配走线阻抗来防止信号失真,从而保持信号完整性。高速PCB设计中,元件与走线的阻抗匹配至关重要。PCB材料的选择(如低损耗层压板)对减少信号衰减起关键作用。受控

信号完整性测试基础知识

在当今快速发展的数字时代,高速传输已成为电子设备的基本要求。随着数据传输速率的不断提升,信号完整性(Signal Integrity,简称SI)问题变得越来越重要。信号完整性是高速互连

PCIe信号完整性问题解决方案

PCIe信号完整性问题解决方案

评论