“ 本章将介绍如何使用设计规则检查(DRC)。 ”

4.8 7-设计规则检查(DRC)

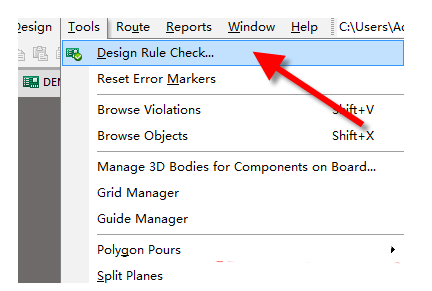

我将在本章中完成 PCB Layout 工作流程的第六步。虽然我在整个 Layout 工作流程中经常进行设计规则检查,尤其是在布线步骤中,但我总是在导出 Gerber 文件用于制造之前进行最后一次检查。在这个简单的项目中,我已经在第四步运行了 DRC,没有发现任何错误,因此我不希望新的检查会显示任何违规。不过,我可以忽略警告,继续制造。

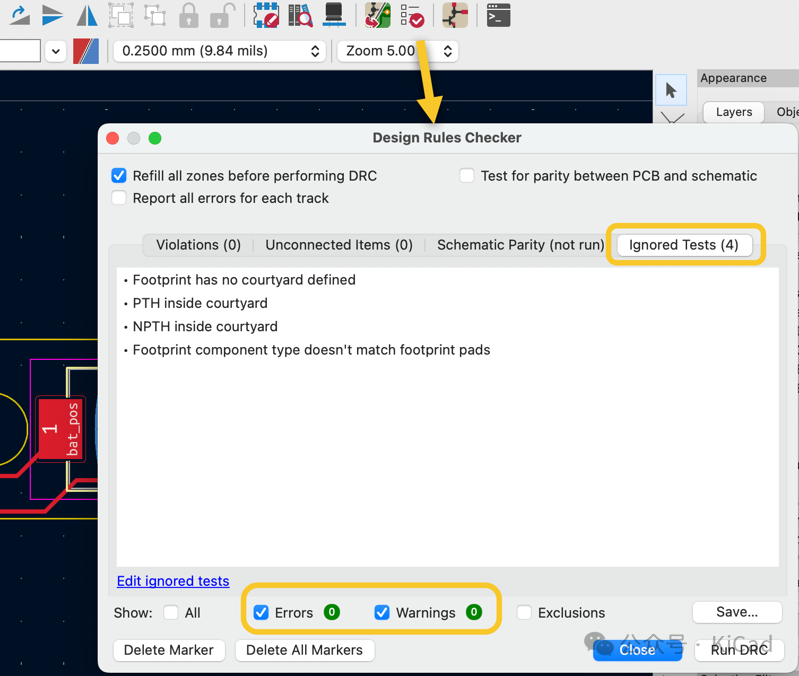

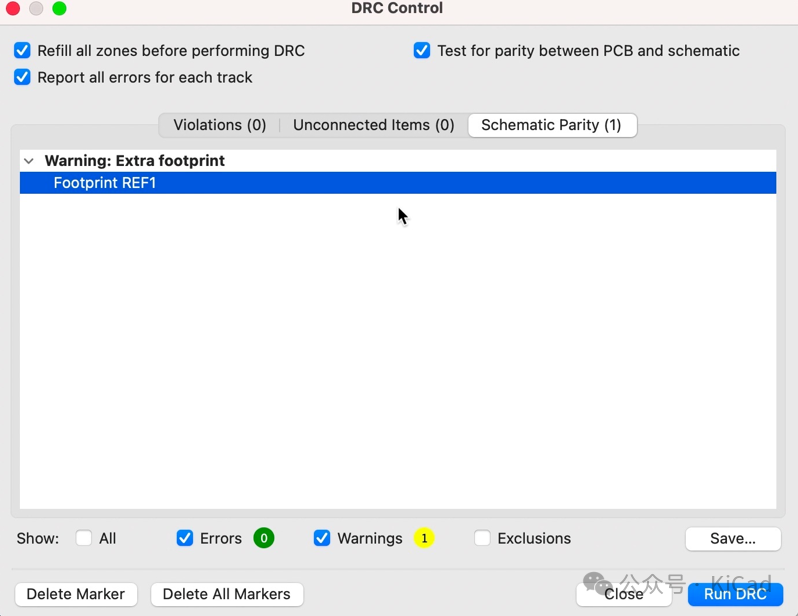

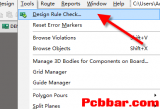

让我们继续进行 DRC。单击顶部工具栏中的 DRC 按钮,然后单击“运行 DRC”。结果如下:

图 4.8.1: 最后一次DRC检查的结果

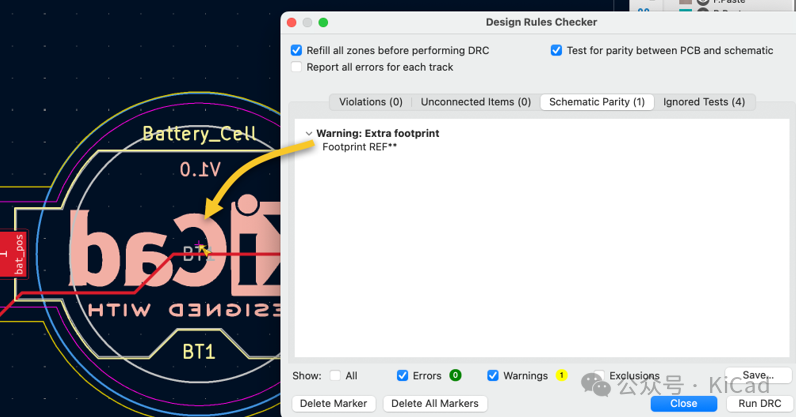

好消息是:没有违规,也没有未连接的项目。在“电路板设置” 窗口的 “设计规则”、“违规严重程度” 下定义了四个被忽略的测试。请注意,“检查 PCB 与原理图是否一致”复选框未被选中,因此没有测试奇偶校验。如果启用奇偶校验并重新运行 DRC,检查将报告有关“额外封装” 的警告。这指的是我在底层丝网层中放置的 KiCad 徽标,在原理图中没有匹配的符号。我可以放心地忽略该警告。

图 4.8.2: 警告与底层丝印中放置的 logo 封装有关

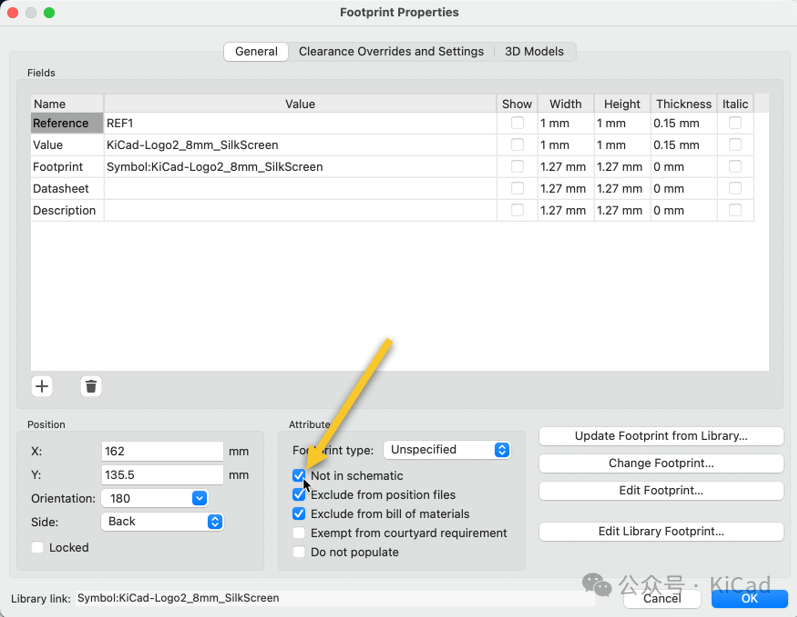

您可以放心地忽略该警告,继续工作流程的下一步(导出 Gerber 文件),因为它不会影响电路板的任何功能或器件。警告表明,Logo 封装的位号号在其名称末尾包含“**”,因此未定义。虽然我可以忽略该警告,但还是要对其进行修正,以便 DRC 不会返回错误或警告。双击 KiCad Logo 封装,调出其属性:

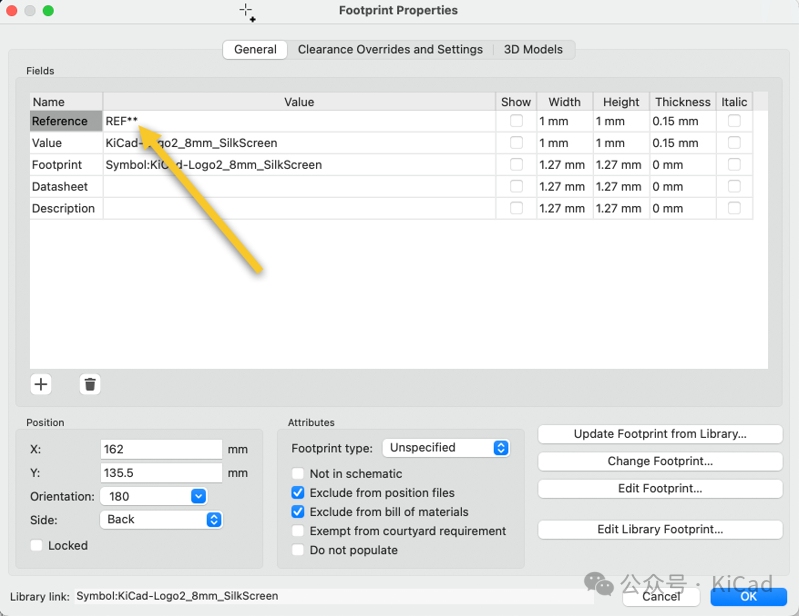

图 4.8.3: 设置位号

注意原位号为“REF**”。我将把它改为 “REF1”,这在这块电路板上唯一的,然后点击 “确定”。再次运行DRC,看看是否消除了原来的警告:

图 4.8.4: DRC中出现了一个新的警告

该警告表明,在PCB编辑器中存在位号为“REF1 ”的封装,但在原理图编辑器中却不存在。这是因为我在设计工作流程的第五步中将该封装添加到了 PCB 中。与 PCB 中的其他封装不同,REF1 在原理图编辑器中没有对应的符号。现在,我有三个选择:

1. 返回原理图编辑器,添加一个新符号,并将其与徽标封装关联。

2. 忽略此警告。

3. 打开封装属性,选中 “不在原理图中”复选框(见下文)。

图 4.8.5: 封装属性中的“不在原理图”选项

制造商只会使用Layout中 Gerber 文件的数据。原理图编辑器中的数据在最终制造的PCB板中不起作用。因此,我现在所做的任何额外工作都不会影响最终产品,只会影响项目的内部一致性。由于我想完成项目,因此我将选择方案二,忽略 DRC 警告。Logo不是我的 PCB 的功能器件,无论它是否存在于原理图中,PCB 都将正常工作。

我已经完成了设计规则检查,并忽略了它返回的唯一警告。现在我准备导出 Gerber 文件并制造我的 PCB。

-

文件

+关注

关注

1文章

598浏览量

26124 -

DRC

+关注

关注

2文章

157浏览量

38352 -

KiCAD

+关注

关注

6文章

330浏览量

10538

发布评论请先 登录

电气设计规则检查工具HyperLynx DRC

Altium-Designer-6-DRC规则检查的英汉对照表

PCB设计电气规则检查器解决DRC问题

Altium designer对DRC的常规检查

PCB layout有DRC检查,为什么还要用DFM?

【实用干货】PCB layout有DRC检查,为什么还要用DFM?

KiCad 教程:集成电路测试 LoadBoard 设计指南

和 Dr Peter 一起学 KiCad 4.9~4.10:导出Gerber并下单(收到成品)

和 Dr Peter 一起学 KiCad 4.5:布线(添加走线)

和 Dr Peter 一起学 KiCad 4.4:移动封装

和 Dr Peter 一起学 KiCad 4.1~4.2:启动PCB 编辑器,导入封装

和Dr Peter一起学KiCad 4.8:设计规则检查(DRC)

和Dr Peter一起学KiCad 4.8:设计规则检查(DRC)

评论