在追求极致性能与效率的科技浪潮中,Rambus再次引领行业前行,正式宣布推出面向下一代高性能台式电脑与笔记本电脑的DDR5客户端时钟驱动器(CKD)。这一创新举措标志着Rambus将其在服务器领域的先进内存接口技术成功扩展至广阔的客户端市场,为PC用户带来前所未有的性能飞跃。

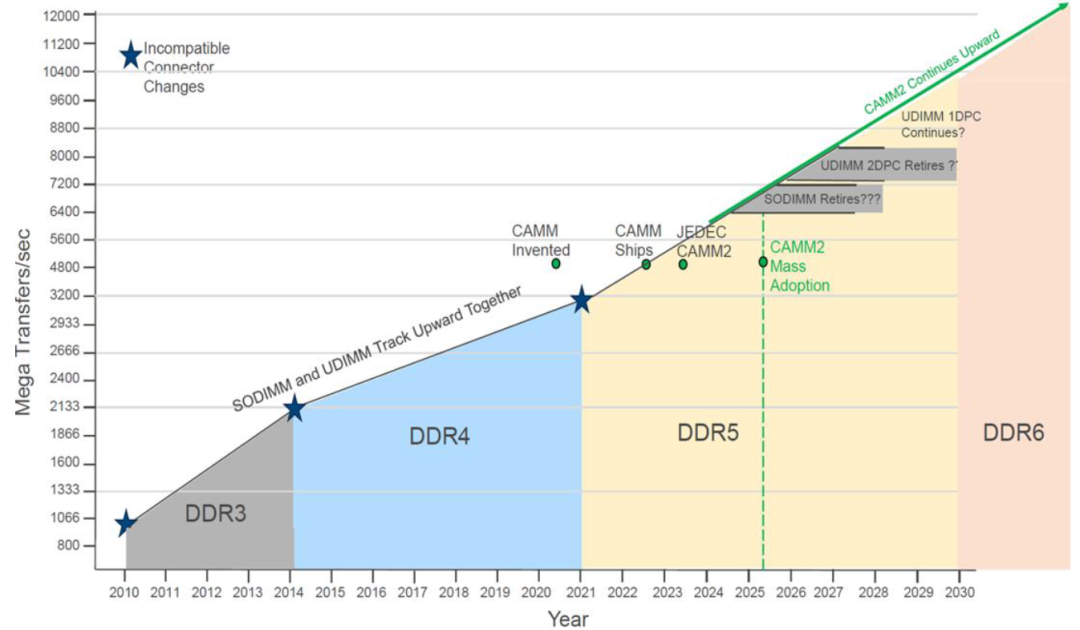

作为Rambus全新客户端内存接口芯片家族的明星成员,DDR5 CKD携手SPD Hub,共同构建起了一套高效、稳定的内存解决方案。依托Rambus超过30年的深厚内存系统专业积累,DDR5 CKD能够完美驾驭下一代客户端DIMM(包括CSODIMM与CUDIMM),推动数据传输速率直冲云霄,最高可达惊人的7200 MT/s,彻底改写PC性能版图。

此次发布不仅是对Rambus技术实力的有力证明,更是对PC行业发展趋势的精准把握。随着数据处理需求的日益增长,高性能、高带宽的内存解决方案已成为提升整体系统性能的关键。Rambus DDR5 CKD的问世,无疑为下一代PC用户打开了通往极致性能体验的大门,无论是处理复杂的多任务场景,还是享受高清流畅的游戏体验,都能轻松应对,游刃有余。

展望未来,Rambus将继续秉持创新精神,不断推动内存接口技术的革新与发展,为全球PC用户带来更多惊喜与可能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Rambus

+关注

关注

0文章

68浏览量

19349 -

时钟驱动器

+关注

关注

0文章

124浏览量

14419 -

DDR5

+关注

关注

1文章

485浏览量

25822

发布评论请先 登录

相关推荐

热点推荐

解析SN74SSQEA32882:DDR3/DDR3L注册时钟驱动器的卓越之选

解析SN74SSQEA32882:DDR3/DDR3L注册时钟驱动器的卓越之选 在DDR3和DDR3L内存模块设计领域,SN74SSQEA3

探索MAX9310:高性能1:5时钟驱动器的设计与应用

探索MAX9310:高性能1:5时钟驱动器的设计与应用 在电子工程师的日常工作中,时钟驱动器的选择对于系统的性能和稳定性至关重要。今天,我们将深入探讨MAXIM公司的一款优秀产品——MAX9310

CDC2351:高性能时钟驱动器的卓越之选

- LINE TO 10 - LINE时钟驱动器,看看它在时钟分配和生成应用中能为我们带来哪些出色的表现。 文件下载: cdc2351.pdf 产品概述 CDC2351是一款高性能的时钟驱动器电路,主要功能是将一个输入

CDC337时钟驱动器:高性能时钟分配与生成的理想选择

下载: cdc337.pdf 一、产品概述 CDC337是德州仪器(Texas Instruments)推出的一款具有三态输出的时钟驱动器,旨在为时钟分配和时钟生成应用提供低输出偏斜和

CDC339 时钟驱动器:高性价比解决方案

我们就来深入了解一下这款 CDC339 时钟驱动器。 文件下载: cdc339.pdf 器件概述 CDC339 是一款高性能、低偏斜的时钟驱动器,于 1994 年 3 月推出,2020 年 5

深入剖析 CDCLVP215:低电压双差分 1:5 LVPECL 时钟驱动器

Instruments 推出的 CDCLVP215 低电压双差分 1:5 LVPECL 时钟驱动器,了解其特性、应用场景以及电气参数等重要信息。 文件下载: cdclvp215.pdf 一、CDCLVP215 概述

TI SN74SSQEA32882:DDR3/DDR3L注册式DIMM的理想时钟驱动器

TI SN74SSQEA32882:DDR3/DDR3L注册式DIMM的理想时钟驱动器 在DDR3和DDR3L注册式DIMM(RDIMM)的

探索 SN74SSQEC32882:DDR3 注册 DIMM 的理想时钟驱动器

了解 Texas Instruments 推出的 SN74SSQEC32882,一款专为 DDR3 注册 DIMM 量身打造的 28 位至 56 位寄存器缓冲器兼地址奇偶校验测试

TI CDCU2A877:高性能DDR II时钟驱动器的卓越之选

TI CDCU2A877:高性能DDR II时钟驱动器的卓越之选 在电子设计领域,时钟驱动器是确保系统时钟信号准确、稳定传输的关键组件。德州仪器(TI)的CDCU2A877

最高支持9200 MT/s速率!澜起科技推出新一代DDR5时钟驱动器(CKD)芯片

电子发烧友网综合报道 11月10日,澜起科技正式推出新一代DDR5时钟驱动器(CKD)芯片,该芯片最高支持9200 MT/s的数据传输速率,可有效优化客户端内存子系统性能,为下一代高性

澜起科技推出支持9200 MT/s速率的DDR5时钟驱动器(CKD)芯片

澜起科技今日正式推出新一代DDR5时钟驱动器(CKD)芯片,该芯片最高支持9200 MT/s的数据传输速率,可有效优化客户端内存子系统性能,为下一代高性能PC、笔记本电脑及工作站提供关

澜起科技成功量产DDR5第四子代寄存时钟驱动器芯片

澜起科技今日正式宣布,已完成DDR5第四子代寄存时钟驱动器芯片(RCD04)的量产。该芯片是高性能服务器及数据中心内存系统的核心组件,将为下一代计算平台带来显著的内存性能提升。

DDR5 设计指南(一):DDR5 VS LPDDR5

“ 本文将详细介绍 DDR5、LPDDR5 的技术细节以及 Layout 的规范要求。然后比较 CAMM2 模组与 SODIMM 的差别。 ” 本文将介绍什么是 DDR5,DDR5

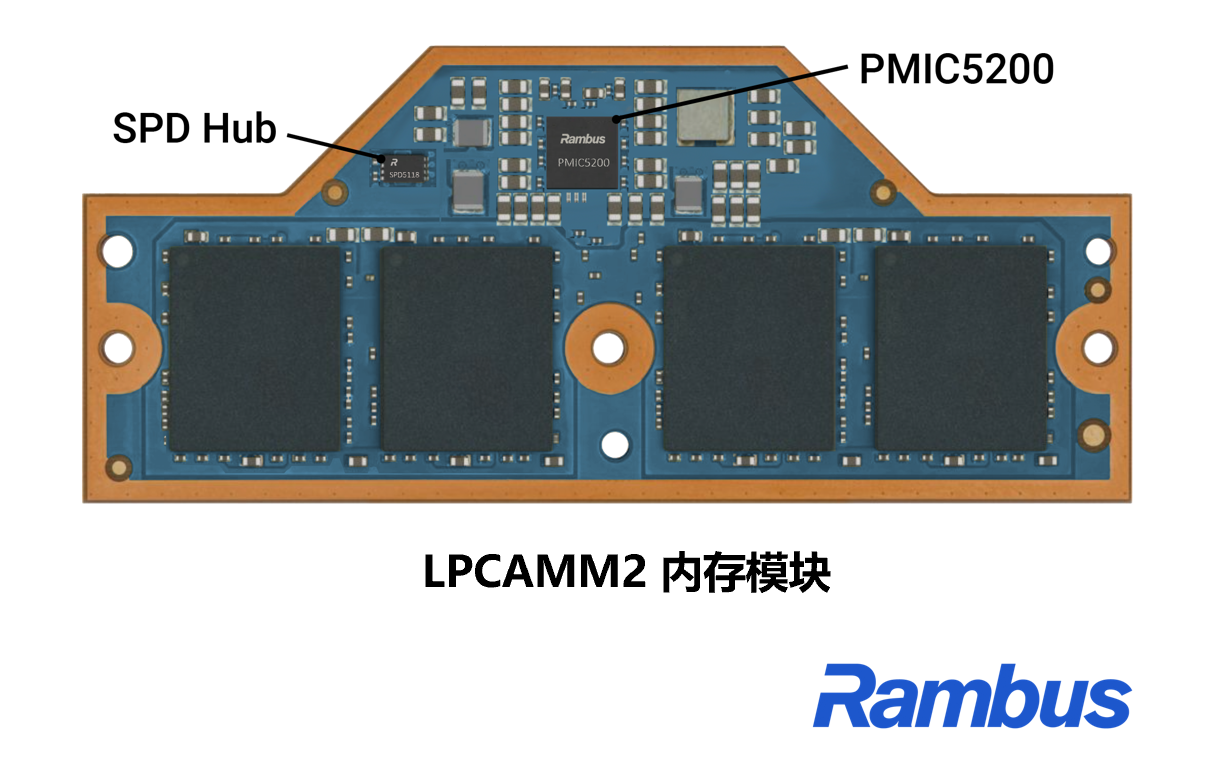

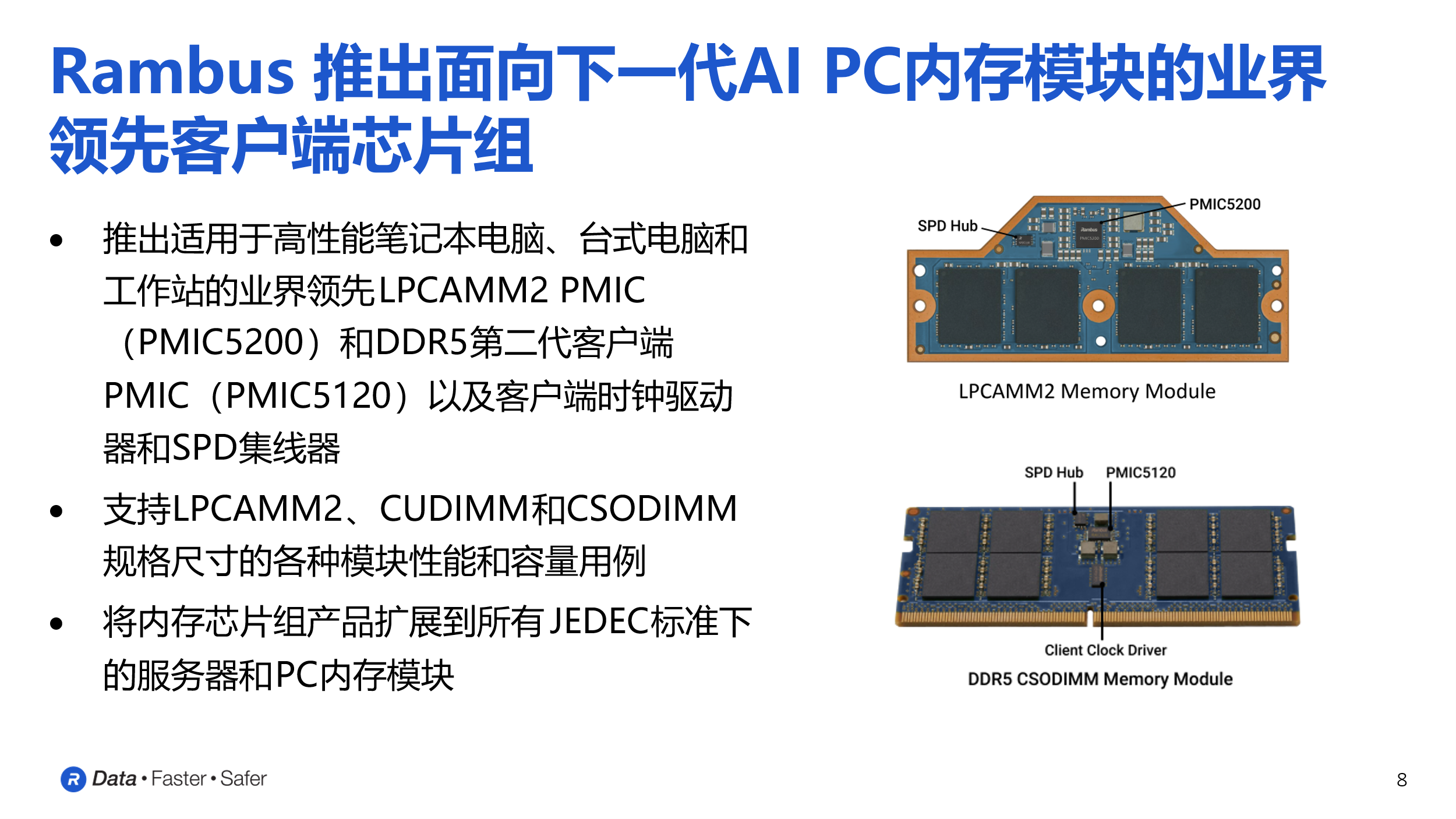

Rambus推出面向下一代AI PC内存模块的业界领先客户端芯片组

图 1: 搭载 Rambus PMIC 和 SPD Hub 芯片的 LPCAMM2 内存模块 图 2:搭载 Rambus PMIC、CKD 和 SPD Hub 芯片的 DDR5 CSODIMM

发表于 05-15 11:19

•1761次阅读

Rambus推出DDR5客户端时钟驱动器

Rambus推出DDR5客户端时钟驱动器

评论