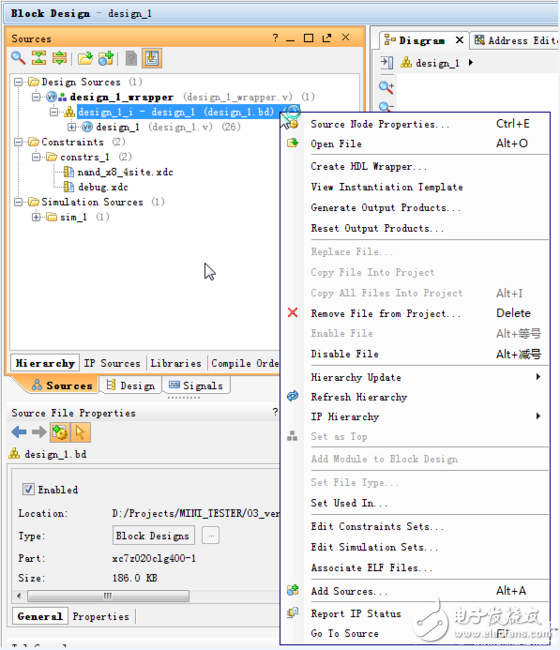

本文详解综合实现和出bit文件。各Block都搭建完成后,选中这个bd右键,Generate Output Products主要是把IP参数和连接信息update到project中,同时也会检查错误。(一般synth也会更新,但是有目标的update下更放心)

没有错误的话,再右键Create HDL Wrapper,给整个bd加个hdl的壳。(因为综合工具不处理原理图bd,所以再次倒腾回hdl的code模式)

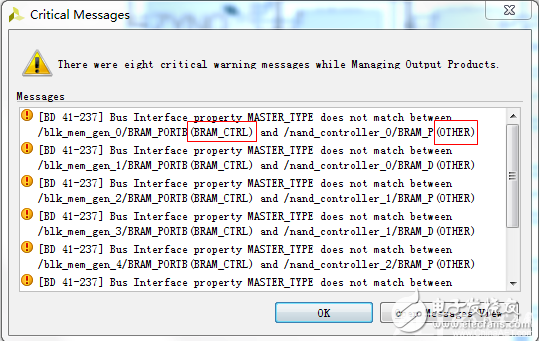

我的project会报这个警告。是BRAM的连接端口不匹配,我自己的IP中BRAM类型是OTHER,可以自己双击BRAM_Port端口把MasterType类型改成BRAM_CTRL,就不报warning了。

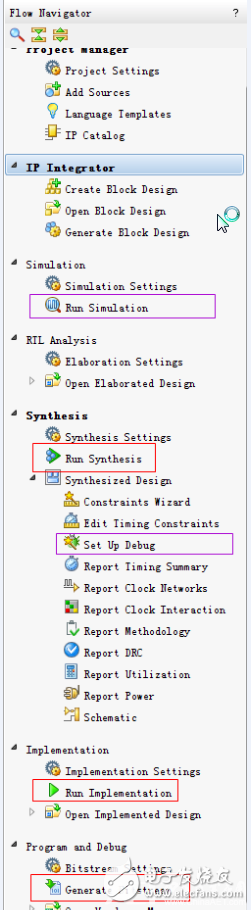

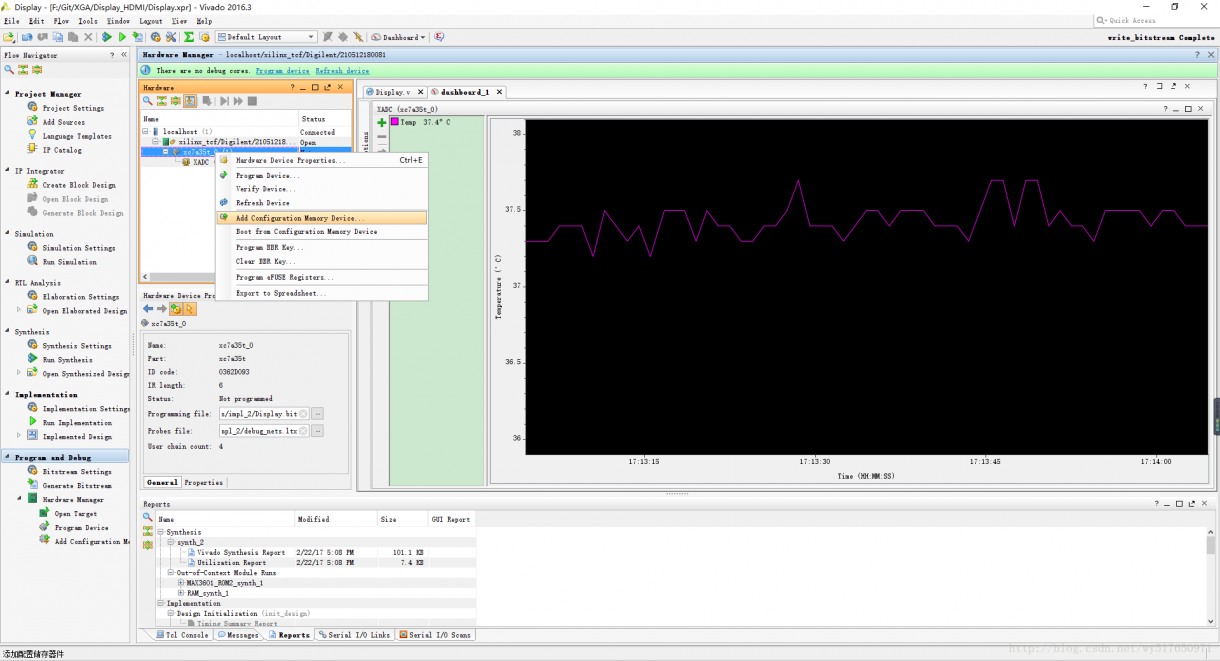

先Run Synthesis,在Run Implementation,最终Generate Bitstream。建议一步一步来,工程大,电脑配置又不顶尖的话,耗时会非常长。一步步来,逐步把错误消了。

上面的Simulation和Debug是两个比较重要的调试环节,后面章节单独介绍。

-

bit

+关注

关注

0文章

48浏览量

32758 -

Vivado

+关注

关注

19文章

848浏览量

70520

发布评论请先 登录

探索Vivado HLS设计流,Vivado HLS高层次综合设计

如何在Vitis中把设置信息传递到底层的Vivado

win10环境下使用vivado生成.bit与.mcs文件

关于Vivado生成的.ll和.bit文件问题

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?

Vivado中综合,实现,编程和调试工程可能会出现的问题及解决方案

使用Vivado 2016.3中IBERT调试的好处及步骤

设置Vivado压缩BIT文件的两种方法

Vivado的安装生成bit文件及烧录FPGA的简要流程教程免费下载

Vivado综合引擎的增量综合流程

Vivado生成bit流失败,怎么解决?

Vivado布线和生成bit参数设置

Vivado中综合实现和出bit文件步骤教程

Vivado中综合实现和出bit文件步骤教程

评论