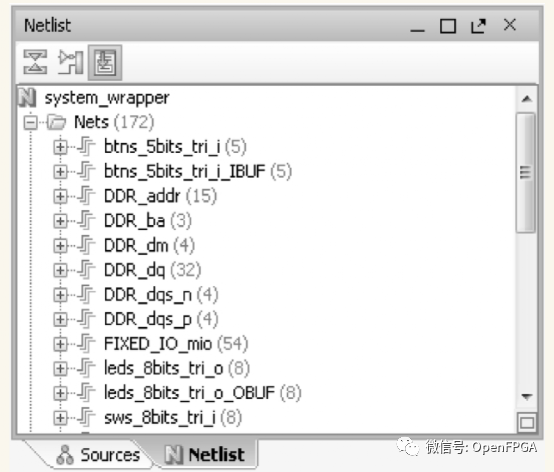

我们都知道FPGA的实现过程分为2步:分析综合与布局布线后就可以产生目标文件,这两个步骤中间有个非常重要的文件,那就是-网表。 下图是Vivado中网表列表示例:

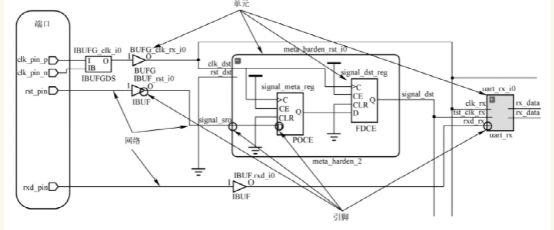

Vivado中网表列表示例 在vivado集成环境中,网表时对设计的描述,如网表由单元(cell)、引脚(pin)、端口(port)和网络(Net)构成。下图是一个电路的网表结构:

电路的网表结构

(1)单元是设计单元

1、设计模块(Verilog HDL)/实体(VHDL)。

2、元件库中的基本元素(Basic Elements ,BLEs)实例。如LUT、FF、DSP、RAM等。

3、硬件功能的类属表示。

4、黑盒。

(2)引脚是单元上的连接点

(3)端口是设计的顶层端口

(4)网络用于实现引脚之间,以及引脚到端口的连接。

编辑:jq

-

dsp

+关注

关注

559文章

8216浏览量

364008 -

RAM

+关注

关注

8文章

1398浏览量

119830 -

端口

+关注

关注

4文章

1098浏览量

33833

原文标题:【Vivado那些事】Vivado中电路结构的网表描述

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

vivado连接Atry A7-35T死机怎么解决?

Windows系统下用vivado将电路烧写到MCU200T板载FLASH的方法

在VIVADO中对NICE进行波形仿真的小问题的解决

vcs和vivado联合仿真

Vivado无法选中开发板的常见原因及解决方法

如何使用One Spin检查AMD Vivado Design Suite Synth的结果

Vivado HLS设计流程

Vivado FIR IP核实现

数字电路设计中:前端与后端的差异解析

VirtualLab Fusion应用:如何建立一个真实光栅结构的光导

Vivado Design Suite用户指南:逻辑仿真

Vivado中电路结构的网表描述

Vivado中电路结构的网表描述

评论