在今年的IEEE IMW 2024活动中,三星DRAM业务的资深副总裁Lee指出,已有多家科技巨头如三星成功制造出16层3D DRAM,其中美光更是发展至8层水平。

然而,他也强调,现阶段三星正致力于探索3D DRAM及垂直堆叠单元阵列晶体管(VS-CAT)的可行性,暂无大量量产的计划。值得注意的是,Lee曾在美光担任过未来存储芯片的研究工作,后于去年加入三星。

VS-CAT与传统DRAM有所区别,其采用双硅晶圆设计,外围设备和逻辑/存储单元独立连接。若将外围设备直接连接至单元层,会导致表面积过大。

因此,外围设备通常在另一片晶圆上制造,再与存储单元通过键合方式连接。预计3D DRAM将采用晶圆对晶圆(wafer-to-wafer)等混合键合技术进行生产,此项技术已广泛运用于NAND和CMOS图像传感器的制造过程。

此外,三星还计划将背面供电网络(BSPDN)技术引入3D DRAM领域。

同时,三星亦在研究垂直沟道晶体管(VCT)。VCT又称4F2,较之先前的6F2技术,可大幅降低晶粒表面积,最高可达30%。据悉,原型产品有望于明年问世。

-

DRAM

+关注

关注

40文章

2373浏览量

188164 -

硅晶圆

+关注

关注

4文章

276浏览量

21977 -

三星

+关注

关注

1文章

1737浏览量

33692

发布评论请先 登录

三星公布首批2纳米芯片性能数据

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

半导体存储芯片核心解析

下一代高速芯片晶体管解制造问题解决了!

无结场效应晶体管详解

三星在4nm逻辑芯片上实现40%以上的测试良率

三星电子否认1b DRAM重新设计报道

三星否认重新设计1b DRAM

三星重启1b nm DRAM设计,应对良率与性能挑战

消息称三星正为苹果iPhone开发三层堆叠式相机传感器

【半导体存储】关于NAND Flash的一些小知识

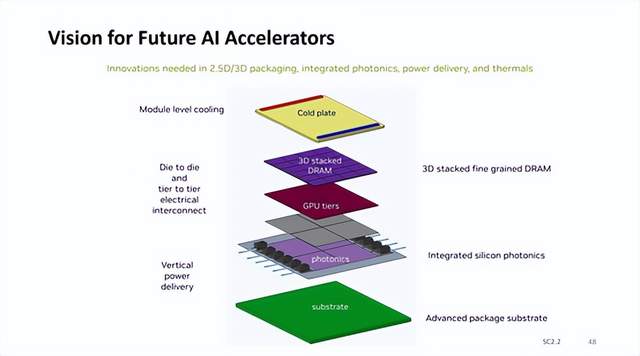

英伟达AI加速器新蓝图:集成硅光子I/O,3D垂直堆叠 DRAM 内存

三星电子研发16层3D DRAM芯片及垂直堆叠单元晶体管

三星电子研发16层3D DRAM芯片及垂直堆叠单元晶体管

评论