一、DTCM和AXI连接的RAM

STM32H7系列处理器内部有多个RAM空间,每个RAM空间的大小和响应速度都不一样。这里面我们重点关注DTCM总线矩阵连接的128KB RAM和AXI总线矩阵连接的512KB RAM。

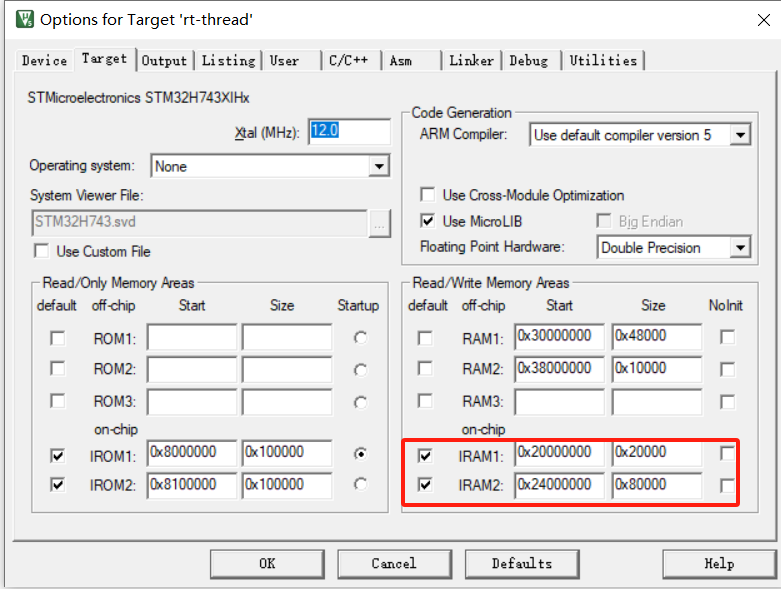

DTCM RAM 128KB:MDK配置是IRAM1:起始地址是0x20000000,大小是0x20000,128KB

AXI RAM 512KB: MDK配置是IRAM2:起始地址是0x240000000,大小是0x80000,152KB

二、lds链接脚本的内存分配

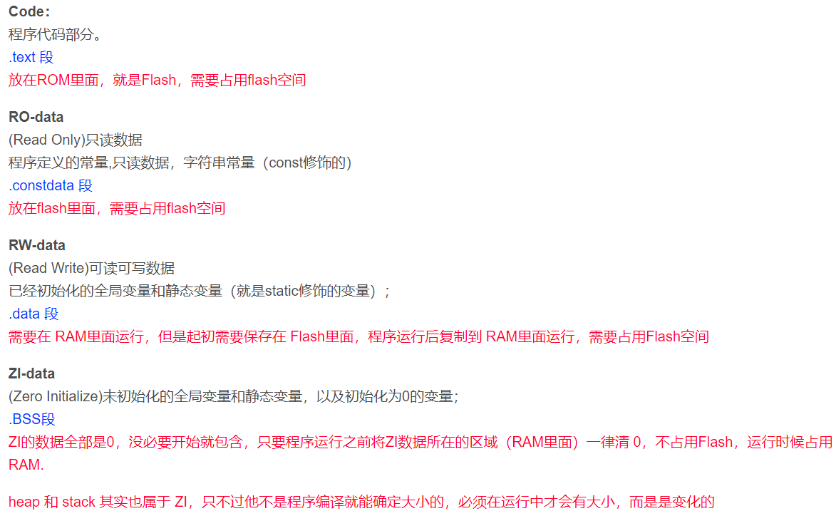

通过上述的分析,我们知道AXI RAM空间要比DTCM RAM空间是要大很多的,那么我们lds链接脚本该如何设置,才能使上电后start_xx.s汇编文件启动能将RW段、ZI段、HEAP、STACK能分配到AXI RAM 512KB 区域呐?取决于lds链接脚本的内存分配。首先我们分析一下RW段、ZI段、HEAP、STACK在内部RAM中是如何分配的(HEAP和STACK实际上也属于ZI段),这里面有几个概念需要清楚。通过下图的描述,我们能看到各个段的含义。

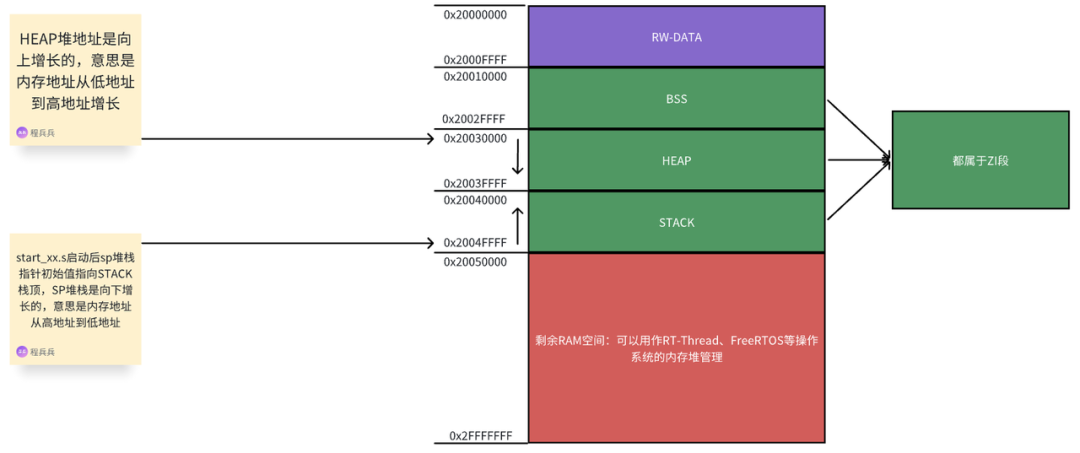

RAM中上述的段分配情况通过以下图表进行说明。从RAM起始地址开始依次存放RW-DATA,BSS、HEAP、STACK和剩余空间。这里举例是以0x20000000开始的128KB AXI RAM进行举例说明。

既然有两个RAM存储区,那么我们的RW-DATA、BSS、HEAP、STACK应该链接在哪一个RAM区,这个时候就需要用到.lds链接脚本,链接脚本的作用就是对RAM和FLASH的分配做指定。

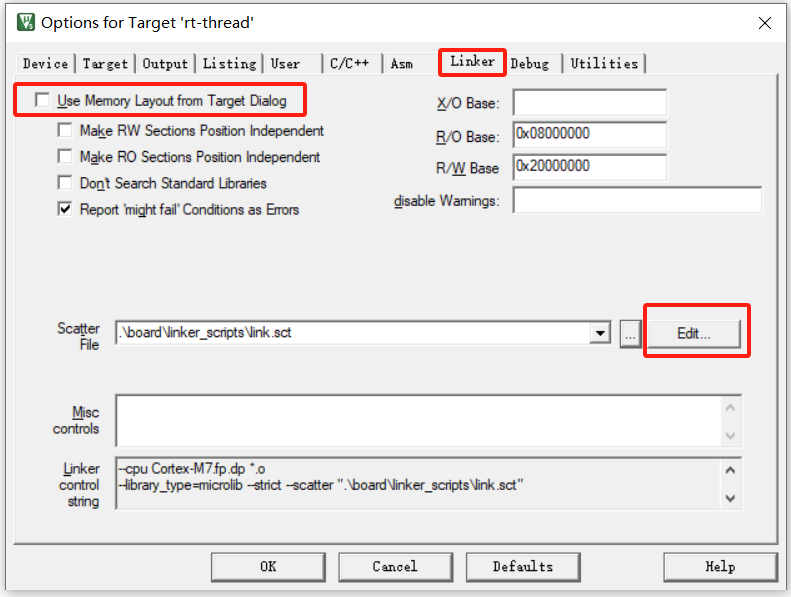

在MDK里有两种类型的链接脚本,一种链接脚本是MDK编译器自动指定,用户不需要关注,另外一种脚本是用户自定义,通过自定义脚本设定多片RAM的指定,和每一片RAM的具体用法。

用户自定义的用法是通过点击魔术棒->linker->按照下图的设置,然后点击Edit按钮就会打开链接脚本。

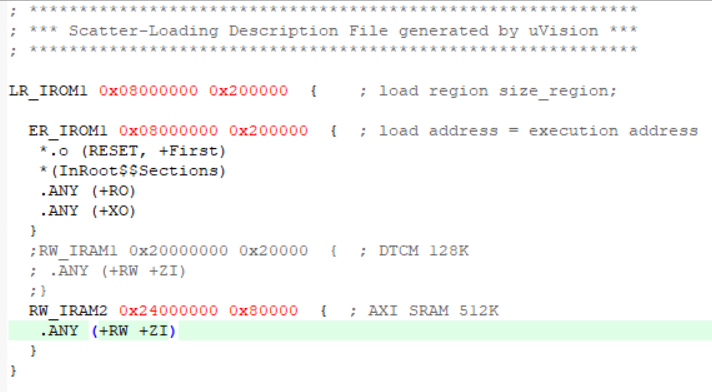

链接脚本的定义如下:通过注释我们知道有俩片RAM区,一片是RW_IRAM1(DTCM RAM:128KB,地址是0x20000000),一片是RW_IRAM2(AXI RAM:512K,地址是0x24000000),这里配置为RW_IRAM1注释掉不使用,使用RW_IRAM2。

.ANY (+RW +ZI),意思是将RW-DATA、ZI(BSS、HEAP、STACK)分配到RW_IRAM2内存区域。在程序上电启动时就会将此RAM使用起来,程序运行的临时变量、全局变量等都在RW_IRAM2中运行。

此时我们发现AXI RAM 128KB空间没用到。如何将这个空间利用起来?rs485_sample_master.o (+RW +ZI)这句话的意思是将rs485_sample_master.c的这个文件中所有定义在RW_DATA段、ZI段的变量全部分布在RW_IRAM1这个RAM空间,也就是AXI RAM 128KB空间。

.ANY (axi_ram_128kb)这句话的意思是用户可以将任意的变量等按照一定的规则定义到RW_IRAM1这个RAM空间,也就是AXI RAM 128KB空间, (axi_ram_128kb) 的含义是这个将RW_RAM1这个内存区声明为axi_ram_128kb section。

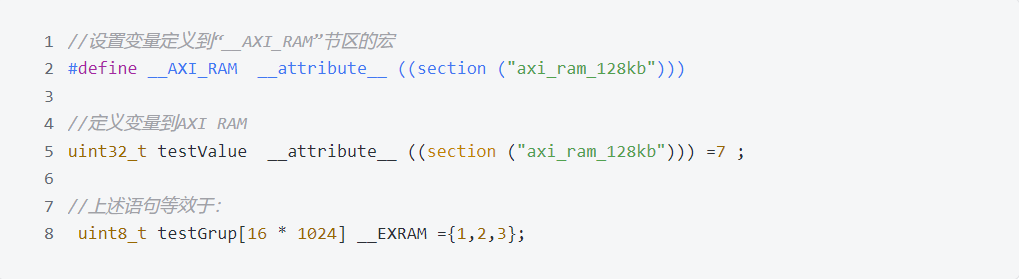

在具体的C语言代码中的定义方式如下:

我们查看.map文件可以看到具体的定义是否有效,或者通过串口查看变量分配地址。通过.map文件的查看,我们可以确定程序中定义的变量确实分配到0x20000000为起始地址的AXI RAM 128KB空间了。

rs485_sample_master.o文件的RW、ZI段也分配在了0x20000000为起始地址的AXI RAM 128KB空间了。

-

处理器

+关注

关注

68文章

20335浏览量

255052 -

RAM

+关注

关注

8文章

1401浏览量

121012 -

总线

+关注

关注

10文章

3060浏览量

91870

发布评论请先 登录

块RAM存储器中的地址冲突场景

深入解析MXD1210非易失性RAM控制器

深入解析DS1557:功能强大的非易失性计时RAM

你的EMC瓶颈,不是经验不够,是体系不全

技术剖析:Cypress CY15B004Q 4 - Kbit 串行 F - RAM

探索MXD1210非易失性RAM控制器:特性、应用与设计要点

FM25V10 1-Mbit 串行 F-RAM 芯片的特性与应用解析

Infineon SEMPER NOR Flash与HYPERRAM™ 2.0 Gen2 Flash+RAM MCP产品解析

Amphenol 38999 Ram-Lock 推拉接口连接器:设计与应用指南

MCU代码需要搬到RAM中才能运行吗?不这样做会有什么不妥嘛?

使用J-Link Attach NXP S32K3导致对应RAM区域被初始化成0xDEADBEEF

你以为的RAM不是你以为的RAM~

你以为的RAM不是你以为的RAM~

评论