问题:为了提高应用的安全性,TLD7002-16ES的帧间延迟应该更长还是更短?

答案:根据数据表,https://www.infineon.com/dgdl/Infineon-TLD7002-16ES-DataSheet-v01_00-EN.pdf?fileId=8ac78c8c81ae03fc0...当主导(“0”)总线通信时间均短于帧间延迟时,HSLI中止处理通信。主帧的等待时间要超过两个连续帧之间的帧间延迟。帧间延迟可以通过OTP进行配置。

帧间延迟有两种类型:

· 短帧间延迟(例如50us)

如果需要实现动画播放等快速数据传输,则需要配置短帧间延迟,这是因为帧的发送间隔极短

· 长帧间延迟(例如500us)

如果HSLI速度较慢(例如200kbps),则需配置长帧间延迟,这是因为在这种速度下,简单的0xFFFF传输有助于使总线在足够长的时间内保持隐性状态,从而触发帧间延迟。

此外,如果HSLI命令器(例如BCM)的串行端口在帧的传输字节之间存在延迟,那么字节之间的延迟(即使它们在同一帧中)可能会错误地触发重置TLD7002-16ES协议处理程序的帧间延迟。

什么是最安全的选择:

最安全的帧间延迟选择应该丢弃不必要的命令(即微控制器应用卡住和重复命令)。此外,应尽可能缩短帧间延迟,以便在传输错误的情况下,能够快速刷新HSLI协议处理程序,并接收新命令。

因此,最安全的帧间延迟选择是,使帧间延迟略长于预期HSLI帧更新周期与最长HSLI帧持续时间的差值。

示例:

如果计划在尾灯标准运行期间每1ms发送一次HSLI命令,则传输速度为1Mbps。在运行期间可以发送的最长帧将是具有380位的DLC6(数据长度代码)的占空比更新,因此它将持续380us。位数的计算方式是对数据表“主帧类型”这一段中描述的DC_UPDATE(DLC6)帧中存在的所有位进行计数。因此,帧间的隐性位距离最大可达1ms-380us=620us。

因此在这种情况下,可将帧间延迟设置为500us(长帧间延迟)。长帧间延迟的缺陷是,如果在传输过程中出现错误,那么命令器在发送新命令之前必须等待的时间比帧间延迟更长。

审核编辑 黄宇

-

微控制器

+关注

关注

49文章

8827浏览量

165577 -

数据表

+关注

关注

0文章

299浏览量

12085

发布评论请先 登录

探索 onsemi NTA7002N 和 NVTA7002N MOSFET:高性能小信号解决方案

请问VisionFive 2 的热安全性如何?

TLD5191HB2W-EVAL评估板:汽车LED驱动的高效解决方案

探索TLD5191IVREG-EVAL评估板:高效驱动与灵活配置的完美结合

探索TLD6098-2DPVB2G_EVAL评估板:双相升压到地电源的卓越之选

电子工程师必备:TLD6098 - 2ES Boost和SEPIC评估套件分析

TLD6099-2ES:一款多功能LED驱动用双路DC-DC控制器

探索TLD7002-16SYS_EVAL评估板:多通道LED驱动的理想之选

迅通科技模块PTR7002的SPI时钟能跑多高

有哪些技术可以提高边缘计算设备的安全性?

如何利用硬件加速提升通信协议的安全性?

宏集分享 | 集中告警管理如何提升设施安全性?

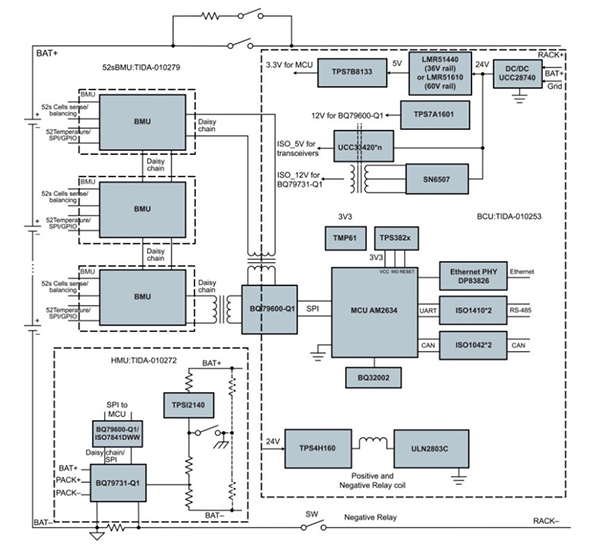

高压 BMS 如何增强安全性并延长电池的使用寿命

为了提高应用的安全性,TLD7002-16ES的帧间延迟应该更长还是更短?

为了提高应用的安全性,TLD7002-16ES的帧间延迟应该更长还是更短?

评论