1CDC常见错误

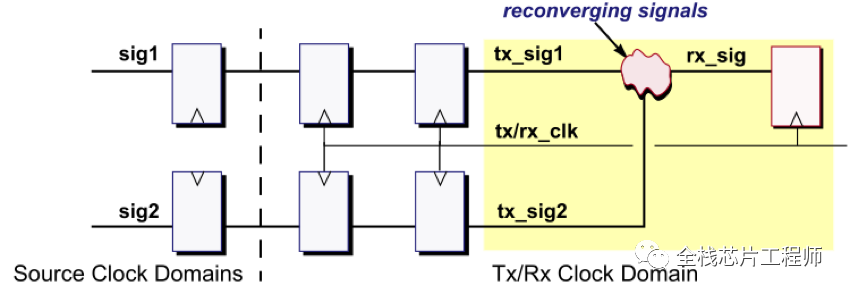

1.1Reconvergence

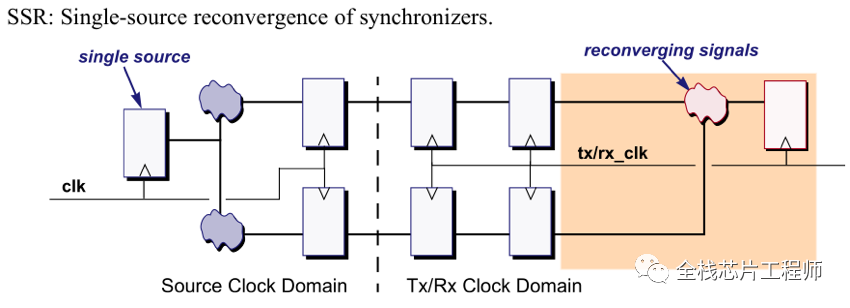

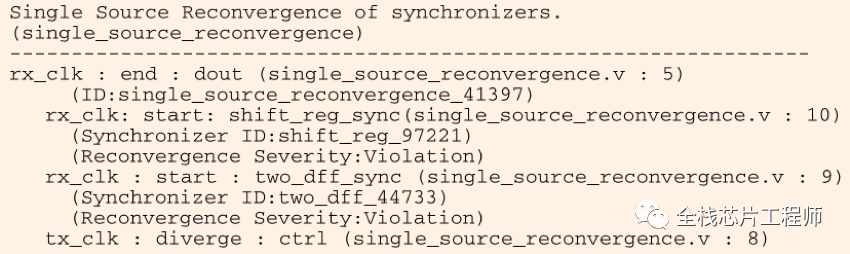

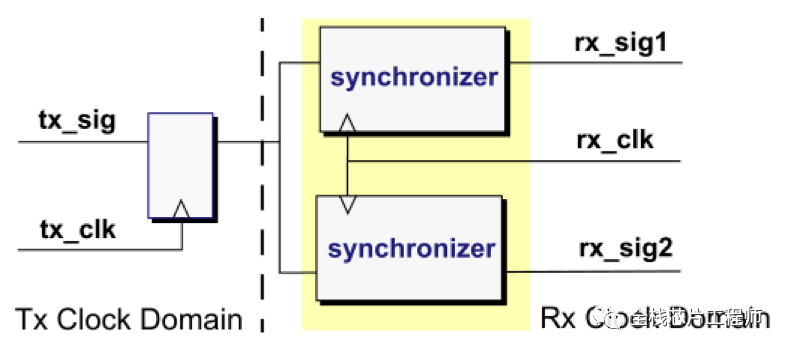

1.1.1single_source_reconvergence

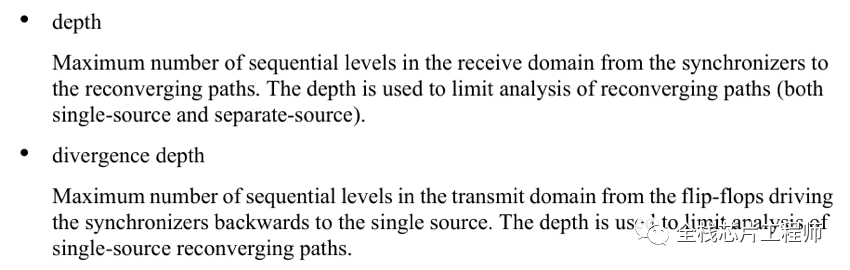

结构:同一个信号源头,两个同步处理器。这里提一下,有两个CDC分析工具的参数配置:

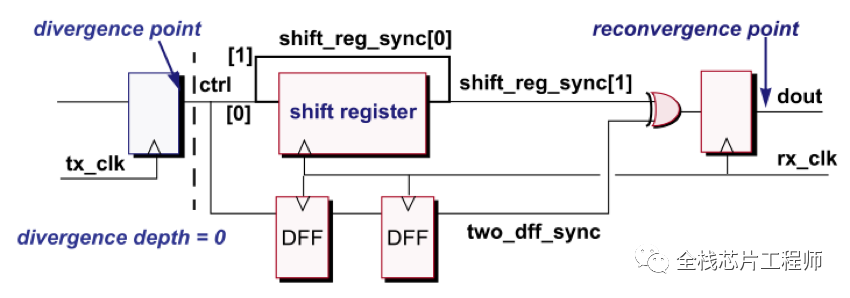

1.1.2案列1:divergence_depths为0

// divergence point

always @ (posedge tx_clk)

ctrl <= ci0 | ci1 ;

// two_dff synchronizer

always @ (posedge rx_clk) begin: two_dff

reg temp;

temp <= ctrl;

two_dff_sync <= temp;

end

// shift_reg synchronizer

always @ (posedge rx_clk) begin: shift_reg

shift_reg_sync <= {shift_reg_sync[0], ctrl};

end

// reconvergence point

always @ (posedge rx_clk)

dout <= two_dff_sync ^ shift_reg_sync[1];

电路如下:divergence_depth为0

CDC报告如下:

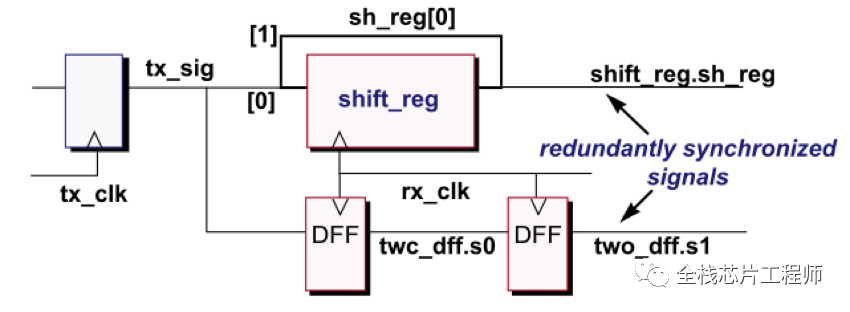

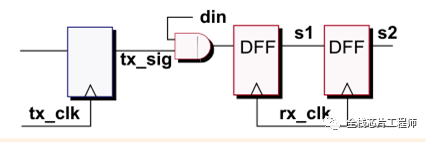

1.2Redundant

案例1:

// two_dff synchronizer of tx_sig

always @ (posedge rx_clk) begin: two_dff

reg s0 , s1;

s0 <= tx_sig; // 1st flop

s1 <= s0; // 2nd flop

end

// two_dff synchronizer of tx_sig

always @ (posedge rx_clk) begin: shift_reg

reg [1:0] sh_reg;

sh_reg <= {sh_reg[0], tx_sig};

end

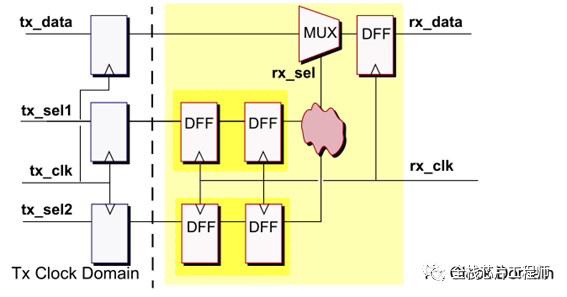

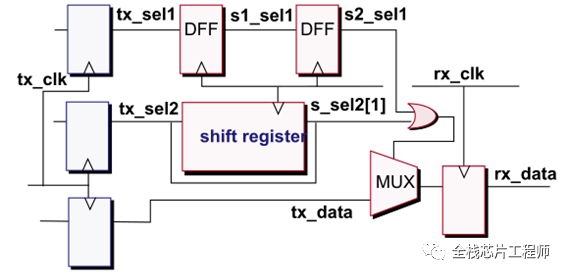

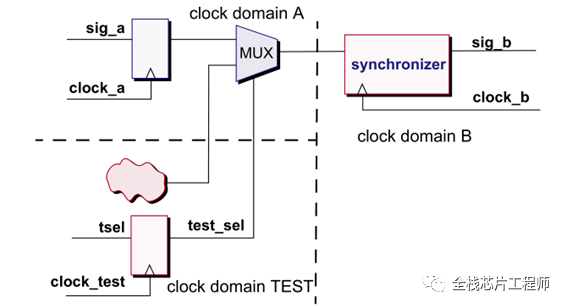

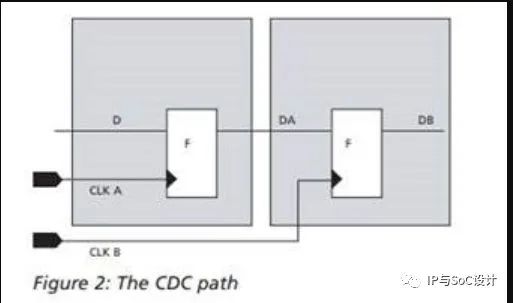

1.3multi_sync_mux_select (DMUX)

MUX的sel端fan-in信号超过一组同步器,不推荐。通常MUX的sel端只能有一组同步器。

案例1:

always @(posedge rx_clk) begin

reg s1_sel1, s2_sel1;

reg [1:0] s_sel2;

s1_sel1 <= tx_sel1;

s2_sel1 <= s1_sel1;

s_sel2 <= {s_sel2[0], tx_sel2};

if (s_sel2[1] | s2_sel1)

rx_data <= tx_data;

end

电路如下:

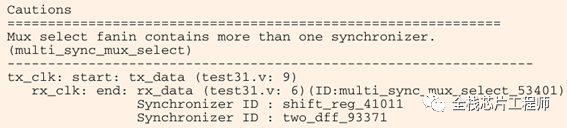

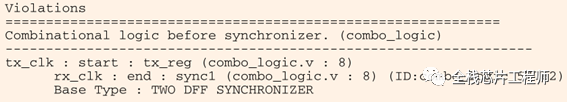

1.4combo_logic

1.4.1错误案列1

always @ (posedge rx_clk) begin

s1 <= tx_sig & din;

s2 <= s1;

end

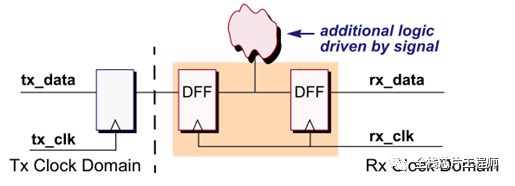

当然还有如下这种错误,除非additional logic全部是静态变量。

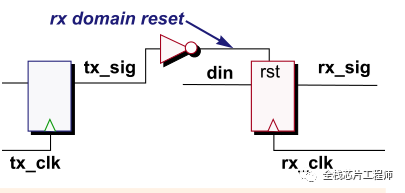

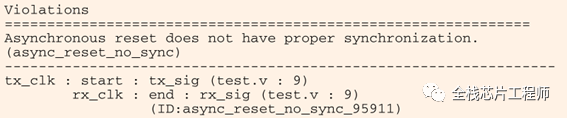

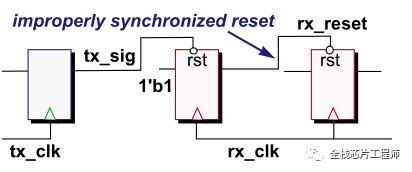

1.5async_reset_no_sync(异步复位、同步撤离)

1.5.1案列1

// Reset triggered by tx_clk always @(posedge tx_clk) tx_sig <= rst; // Unsynchronized reset used in // Rx domain always @(posedge rx_clk,negedge tx_sig) if (!tx_sig) rx_sig <= 1’b0; else rx_sig <= din;

1.5.2错误案列2

// Reset triggered by tx_clk always @(posedge tx_clk) tx_sig <= rst; // Improperly synchronized reset used // in Rx domain always @(posedge rx_clk,negedge tx_sig) if (!tx_sig) rx_reset <= 1’b0; else rx_reset <= 1’b1;

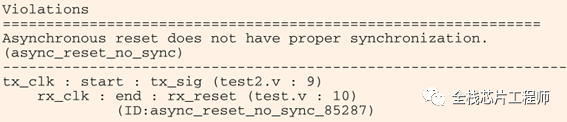

正确的结构如下:

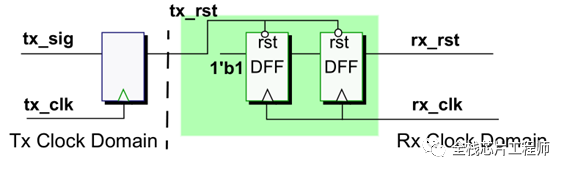

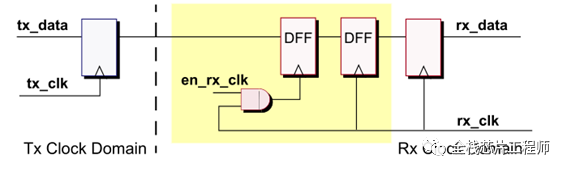

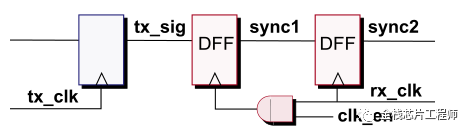

1.6dff_sync_gated_clk

案列1,与门做时钟gating有毛刺,需要clock gating cell。

// gated clock expression

assign gclk = rx_clk & clk_en;

always @(posedge gclk)

sync1 <= tx_sig; // 1st DFF

always @(posedge rx_clk)

sync2 <= sync1; // 2nd DFF

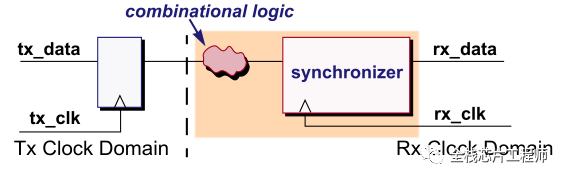

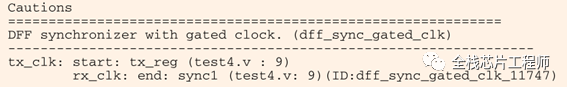

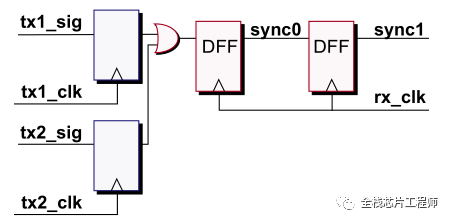

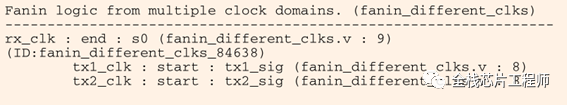

1.7fanin_different_clks

同步器的输入由两个异步时钟域的组合逻辑构成,如下图所示:(还有combo logic)

值得注意的是,如果sig_a或者sig_b中有一个信号是stable静态变量,那么上图结构的电路就不会被报fanin_different_clks或者combo_logic错误。

假设有sig_a、sig_b、sig_c三个信号及以上的fan_in呢?抛开静态变量后,

若所有信号都是同一个时钟域,CDC错误类型就是combo_logic;

若所有信号来自至少2个时钟域,CDC错误类型就是fanin_different_clks;

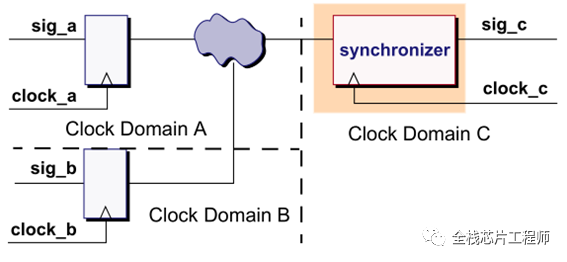

举个例子,如下图:

上图电路仍会报fanin_different_clks,但是电路确实是设计者的意图,我们只需要将TEST时钟域的test_sel设置为常数0即可。

1.7.1案列1

always @ (posedge tx1_clk)

tx1_sig <= in1;

always @ (posedge tx2_clk)

tx2_sig <= in2;

always @ (posedge rx_clk) begin

sync0 <= tx1_sig | tx2_sig;

sync1 <= sync0;

end

审核编辑:刘清

-

处理器

+关注

关注

68文章

20329浏览量

254838 -

芯片设计

+关注

关注

15文章

1171浏览量

56775 -

CDC

+关注

关注

0文章

58浏览量

18594 -

异步电路

+关注

关注

2文章

48浏览量

11560 -

静态变量

+关注

关注

0文章

13浏览量

6886

原文标题:芯片设计之CDC异步电路(五)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA User Guide之report_cdc

如何使用report_cdc命令分析、调试和修复CDC问题

ic设计——CDC的基本概念

要实现CDC验证标准,ASIC开发团队将会面临哪些挑战

ASIC/FPGA设计中的CDC问题分析

XDC约束技巧之CDC篇

芯片设计进阶之路—SpyGlass CDC流程深入理解

芯片设计之CDC异步电路分析(五)

芯片设计之CDC异步电路分析(五)

评论