台积电推出更先进封装平台,晶体管可增加到1万亿个。

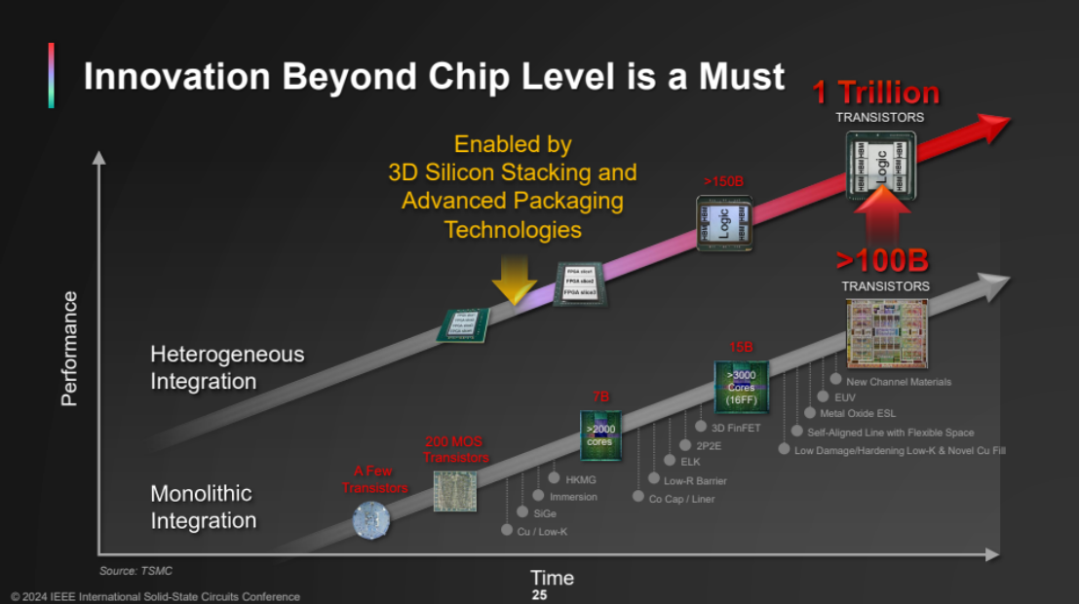

在ISSCC 2024上,台积电正式公布了其新的先进封装平台,该技术有望将晶体管数量从目前的1000亿提升到1万亿。

台积电业务开发资深副总裁张晓强(Kevin Zhang)在国际固态电路大会ISSCC 2024 介绍公司最新技术,并分享未来技术演进、对于先进制程展望,以及各领域中所需要的最新半导体技术。

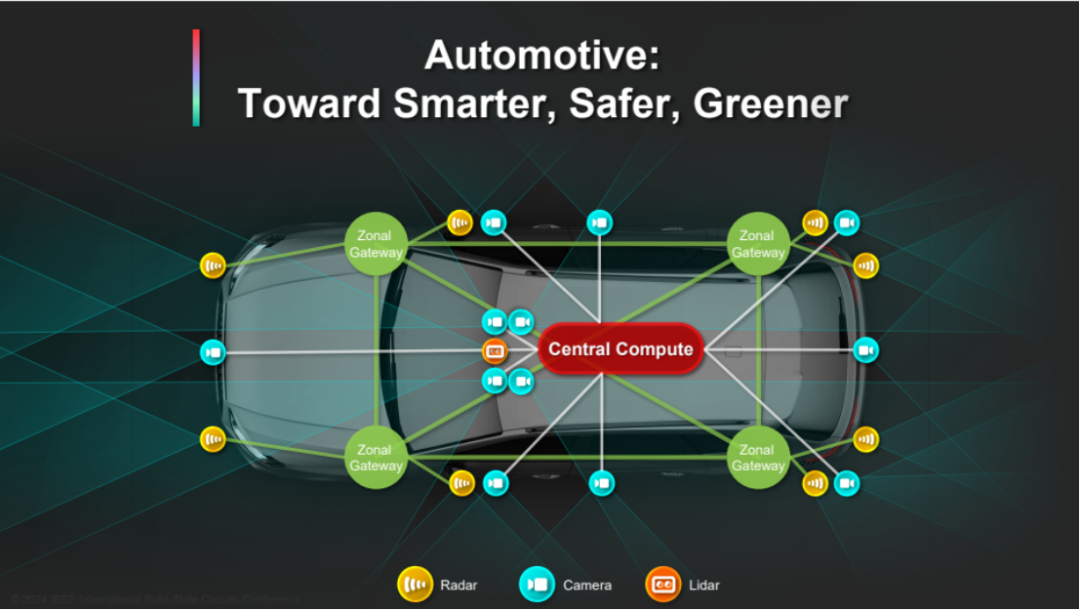

Kevin Zhang指出,随着ChatGPT、Wi-Fi 7 出现,已经需要大量半导体,我们也进入半导体高速成长期。在车用部分,汽车产业正经历一场革命,许多人说新的汽车将是定义软件,但他觉得是“硅定义汽车(silicon-defined automotive)”,因为软件需要在硅上运作,推动未来的自动驾驶能力。

本文整理了Kevin Zhang的演讲内容。

从高性能计算、AI机器学习到通信,从交通到医疗保健,凡是目之所及都与半导体相关。Kevin Zhang最开始从商业的角度谈了半导体。

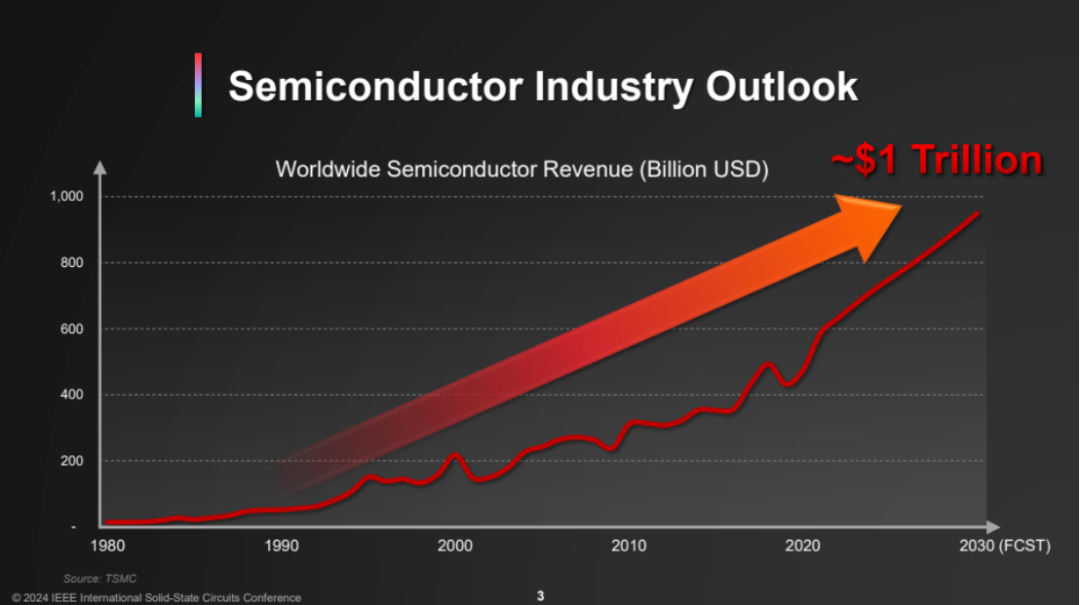

正如我们今天所见,全球半导体收入大约在五千亿美元。业内都认为,到了本十年末,这个数字将翻一番。但Kevin Zhang在这里加上一个限定词:随着人工智能的激增。一万亿数字并不能反映出Open AI的Sam Altman计划投资半导体的数万亿。这个不算最新的预测。AMD的Lisa SU认为,到2028年,仅人工智能市场就能够达到4000亿美元。

Kevin Zhang说到:“没有人能够确切的知道人工智能将如何塑造这条增长曲线。只有一件事能够确定,我们正在进入半导体的加速增长期。”

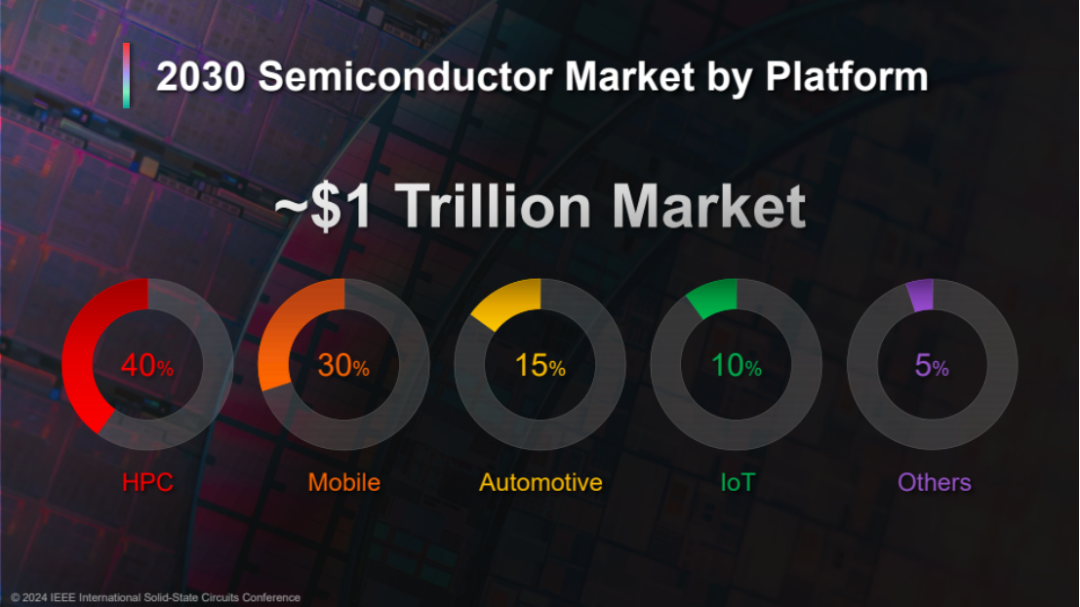

如果更深入的了解这个潜在的万亿市场的高点,高性能计算将占据40%的份额,超过移动设备成为第一大领域。在几年前,如果说到与物联网结合,那是不可想象的。因为传统观点始终认为,边缘设备是用户消费数据的地方,但是到了现在有了AI。

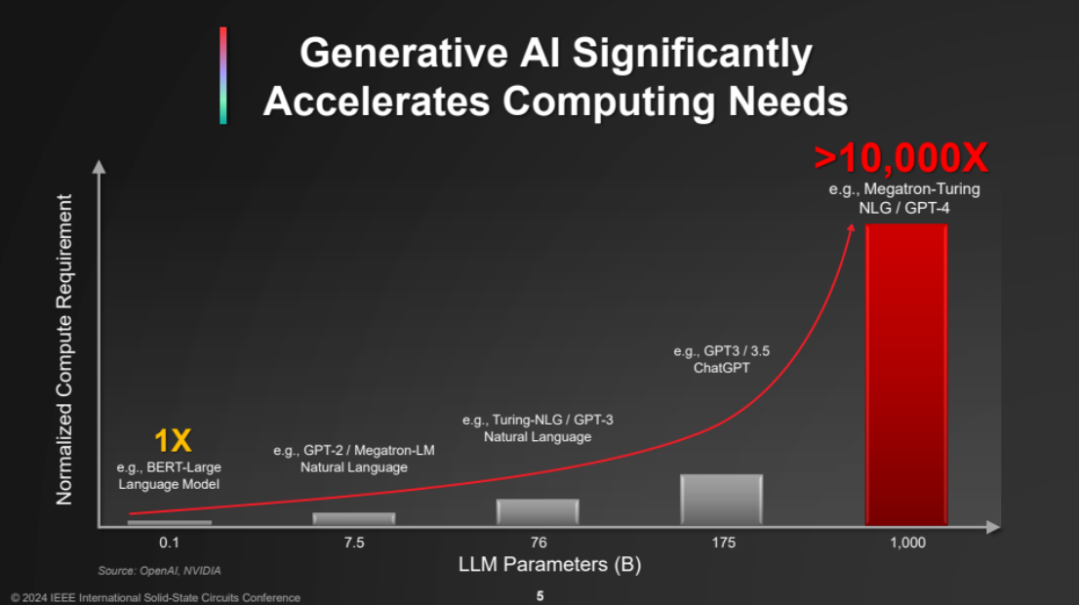

当谈到AI,那不可避免的需要谈到Chat GPT。自从一年半以前Chat GPT推出以来,我们已经看到半导体行业的格局正在发生变化。

看图上陡峭的曲线,这背后其实是对算力的永不满足。因此,英伟达首席执行官黄仁勋曾说到:“Chat GPT是人工智能的iphone 时刻。”我们可以使用不同的方式描述AI,但确定的是,AI需要大量先进的半导体,这个需求数超越人们的想象。

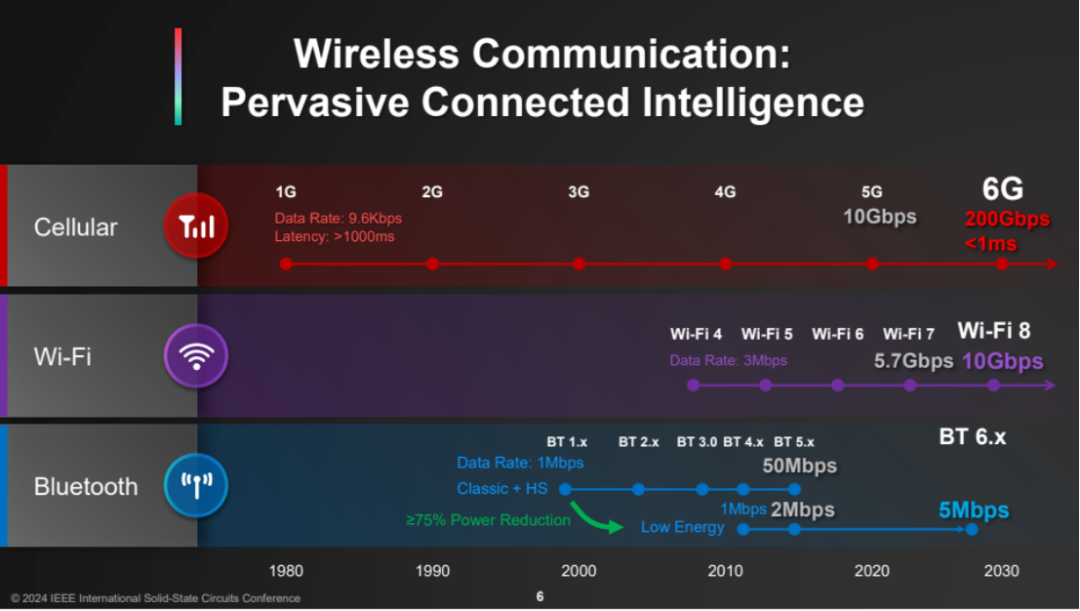

之后,Kevin Zhang也谈到了无线通信。通信在生活中非常的重要,上图展示了三种通信技术:蜂窝、WI-FI、蓝牙。正如所见,所有高级标准都需要更高的数据速率,更先进的信号处理,这将继续推动加速采用先进的技术,例如Wi-Fi 7。台积电今年也正在着手生产Wi-Fi 7的产品。从一开始,Wi-Fi 7的产品就必须采用7nm技术才能够达到功耗性能目标。

在汽车领域,汽车正在经历一场根本性的革命。很多人认为新汽车将是软件定义汽车,但Kevin Zhang认为更好的术语是:“硅定义汽车(silicon-defined automotive)”。因为所有的软件都必须在硅上运行。无论是传感器、通信、网络都在推动最先进的半导体自主的向前发展技术。

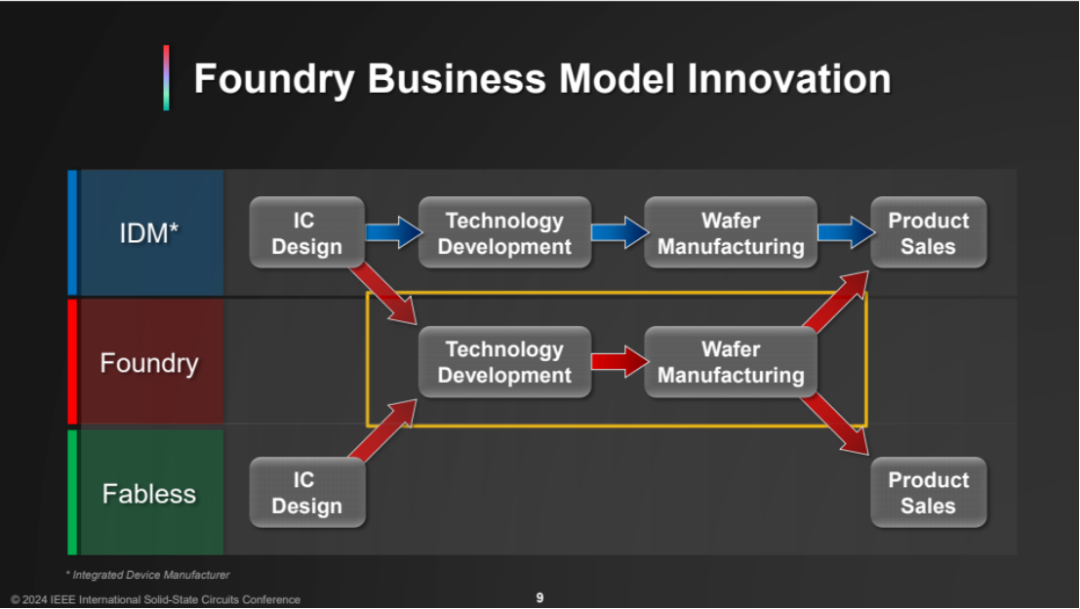

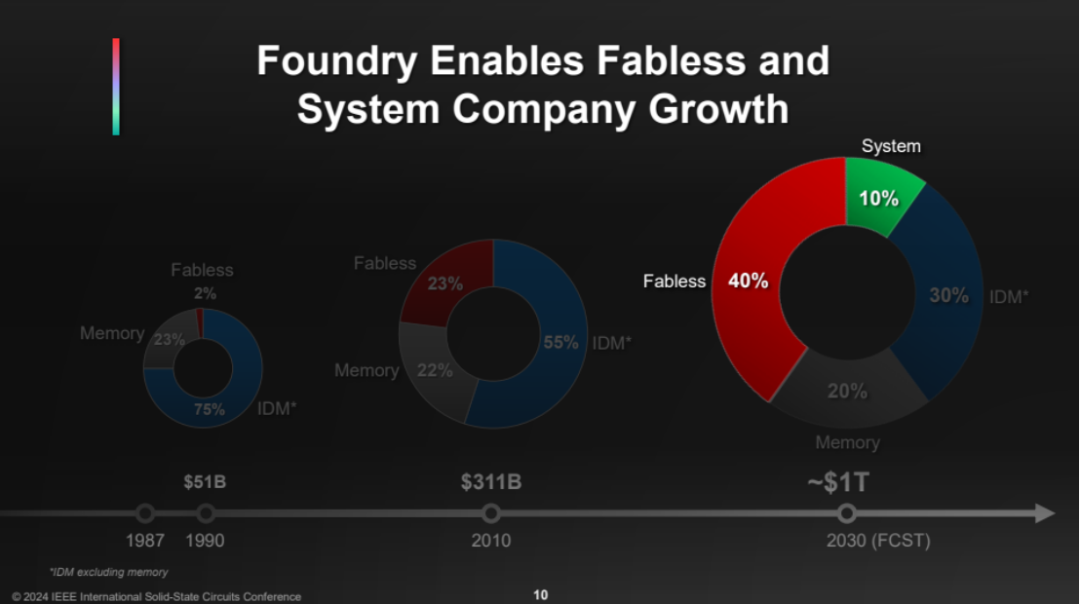

在谈技术前,Kevin Zhang还花费了时间谈到了半导体行业业务的创新——纯代工业务的出现,这项创新从根本上改变了半导体行业的格局。通过从传统的IDM模式中剔除非常复杂、成本高昂的晶圆制造,让无晶圆企业能够专注产品开发和创新。与代工厂的合作,共同极大的加速了行业的创新。

由于代工厂的引入,出现了很多新玩家。快进到2030年,如上图所见,超过50%的半导体收入由优秀的无晶圆公司、系统公司或云公司贡献。这些都是因为业务创新、代工厂的出现。

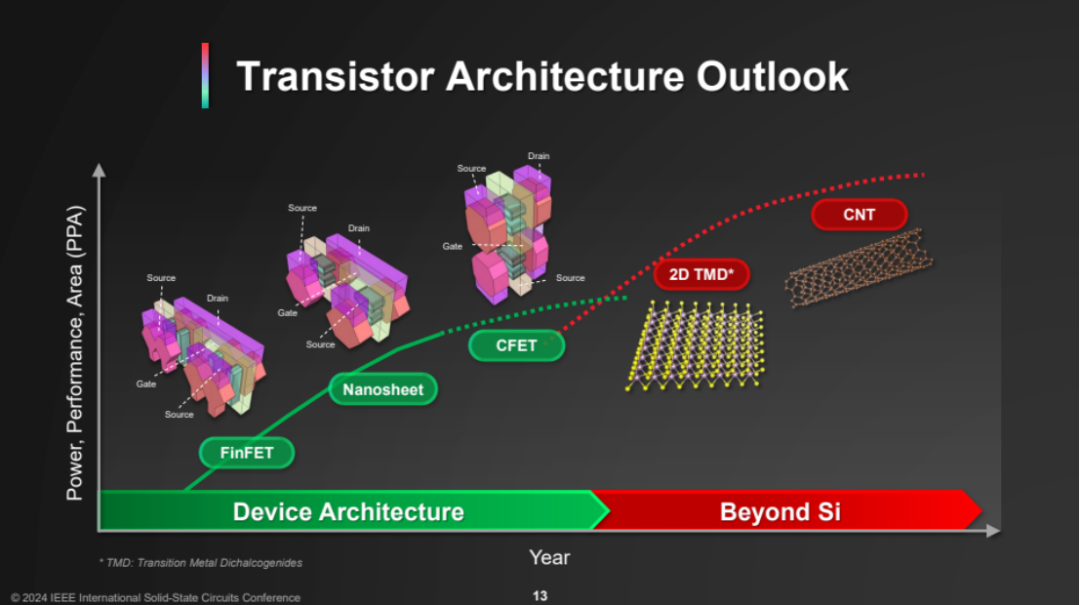

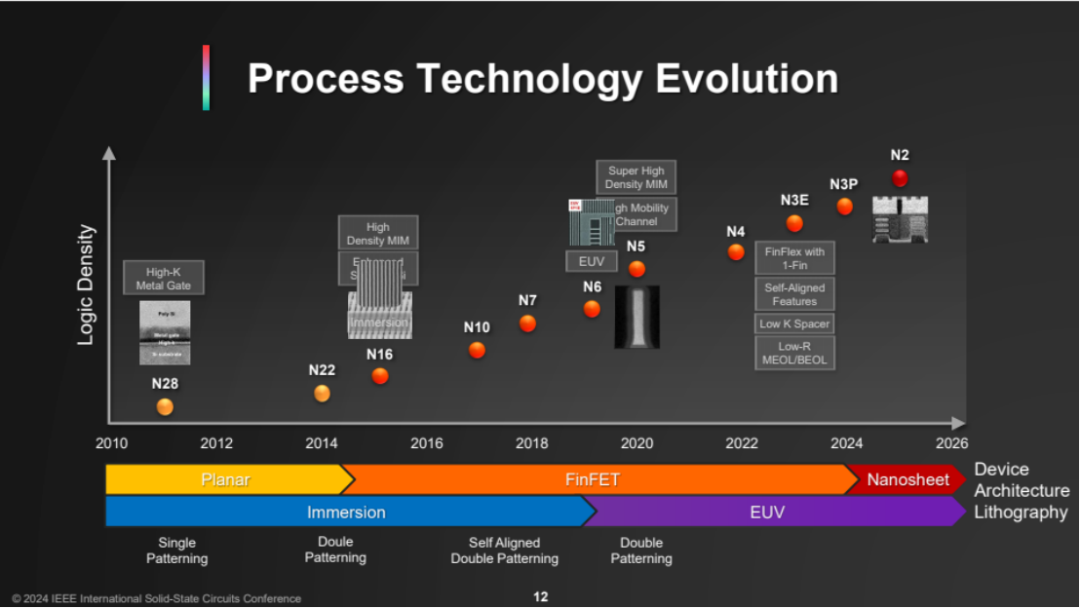

之后,Kevin Zhang开始谈到了本次演讲的重点:先进技术。Kevin Zhang认为,晶体管仍然是创新的核心,即硅创新(silicon innovation)。几十年来,晶体管经历了多次重大的演变。如上图可见,早期的晶体管创新主要集中在围绕几何减少,但现在情况不再如此。最近一代,一切都集中在晶体管架构的创新以及新材料的使用上。

比如说,16nm将从平面晶体管转向FinFET晶体管。今天,台积电在2nm层面即将推出一种全新的晶体管:Nanosheet。可以极大的改善设备的漏电,提高传导能力,并且在更低的电压下更好的工作。这对于高性能计算来说非常重要。

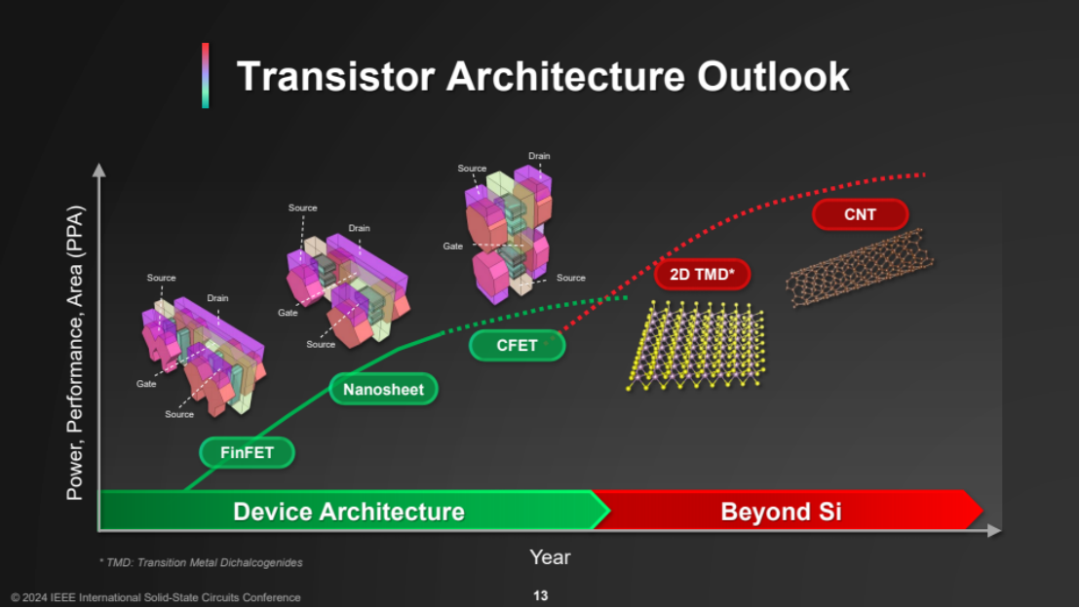

图案化技术方面,7纳米中,EUV的引入为我们铺平了道路,推动几何缩放向前发展。很多人会问:下一步是什么?Kevin Zhang表示,下一步需要利用Nanosheet,经过几代人的努力获得最佳值,即这个新晶体管的极限。与此同时,台积电也在忙于制造全新的晶体管架构:CFET。本质上,是通过将N-transistor、NMOS和PMOS堆叠在一起,可以将密度大大提高近两倍。

在材料方面,台积电也致力于新材料,例如一种低维材料,通过使用这种新材料,我们可以实现更加节能的目标,远超当今的器件或者晶体管。

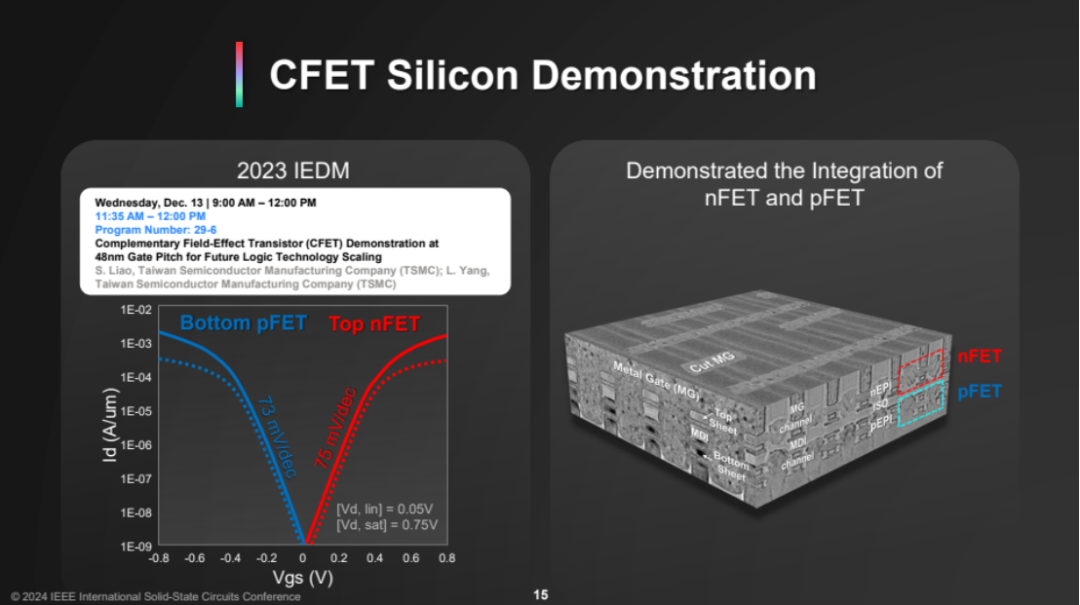

进一步了解CFET可以带来的好处,如上图可见,CFET(互补式场效晶体管CFET)是将nMOS和pMOS 垂直堆叠,可大幅改善零组件电流,使晶体管密度提升1.5~2 倍。

这项技术将硅(Si)和锗(Ge)等不同材料从上下方堆叠,使p型和n型的场效晶体管更靠近。通过这种叠加方式,CFET 消除n to p 分开的瓶颈,将运作单元活动区域(cell active area)面积减少2 倍。

Kevin Zhang展示了一张图片,指出这并不是仅仅在PPT上的想法。从上图可以看到,这是台积电实验室制造的真正集成设备,还有晶体管IV优美的曲线。就推动创新而言,这是晶体管架构的一个重要里程碑。

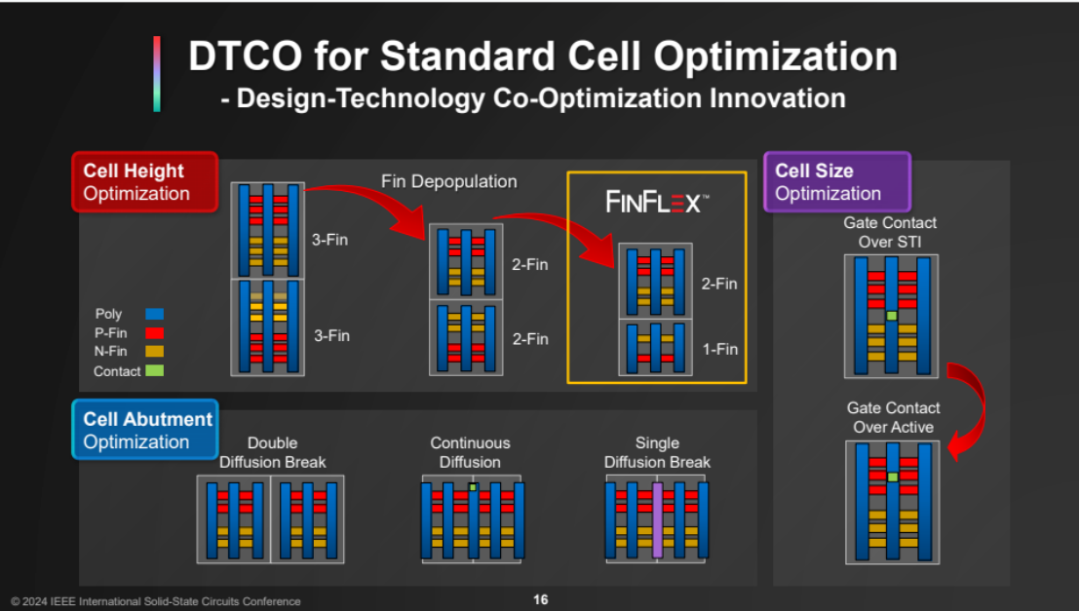

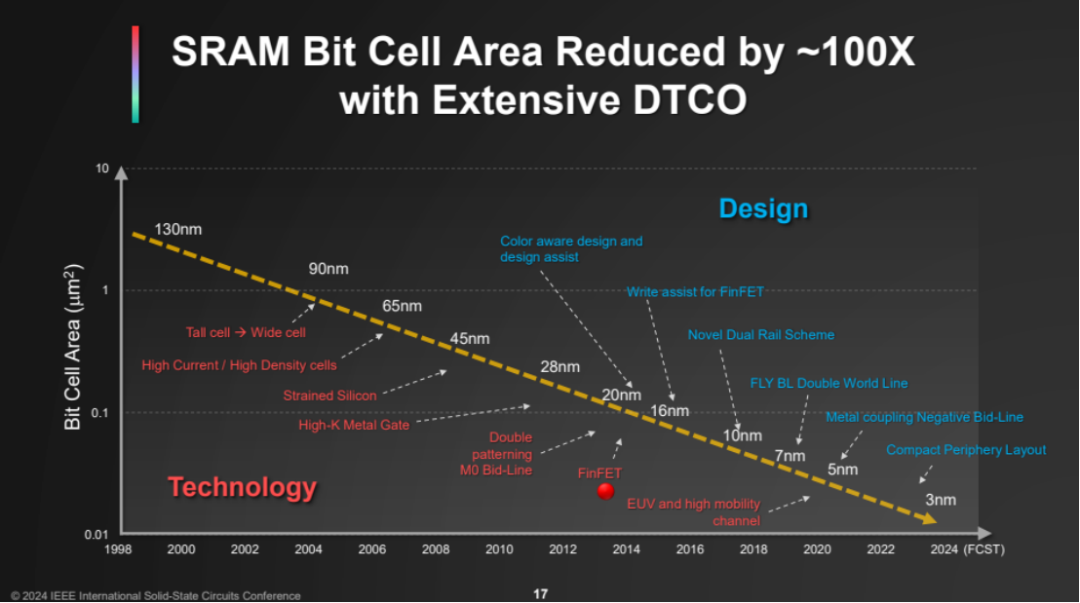

随着晶体管尺寸的缩小,继续缩小晶体管的几何形状变得越来越困难,成本也越来越高。设计师和工程师必须共同努力才能够实现产品层面效益的最佳缩放。因此,台积电经常将其成为设计技术联合组织,或DTCO。

上图展示了一个基于FinFET技术的数学图书馆设计示例。通过使用D-POP技术,减少每个部分的鳍片数量,可以在减小几何尺寸的同时降低功耗。但是当每个设备达到两个鳍片式,设计人员会面临困境。

通过DTCO,台积电的设计和技术团队共同努力,创新的提出了FinFlex的新想法。本质上,允许设计人员混合和匹配单鳍器件、双鳍器件或者双鳍器件和三鳍器件,因此我们可以同时实现最佳的性能、密度和功耗。

另一个很好的例子是SRAM位单元。上图展示了SRAM从130nm一直到今天的3nm,实现了超过100倍的密度提升,这种规模化实际上是流程创新和协作结合的成果,采用更先进的设计技术。

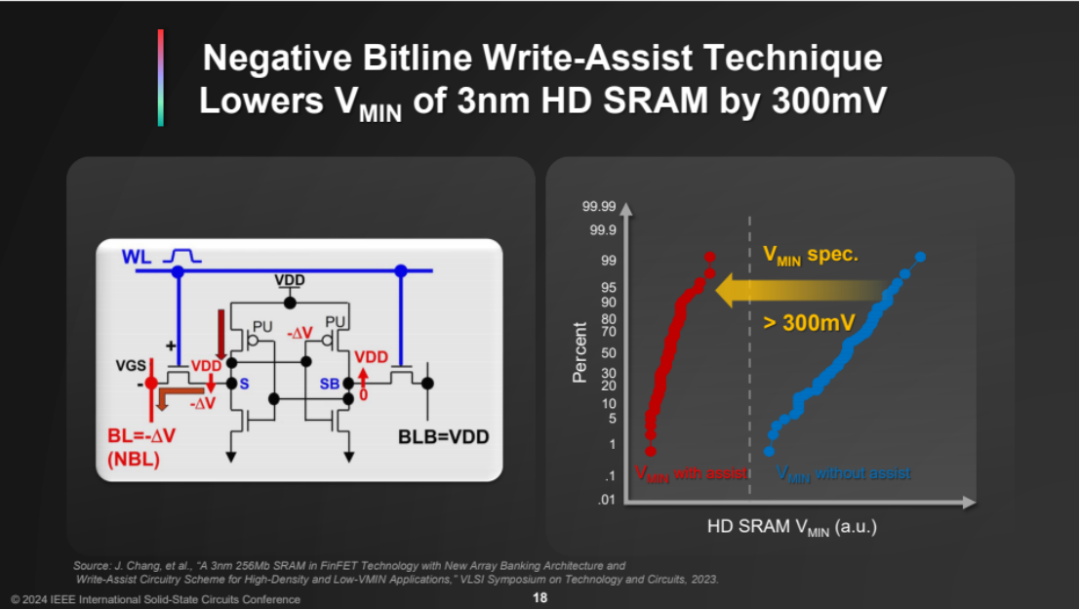

说到SRAM,就不得不谈到最低工作电压,或者说Vmin。在过去很长时间,为了降低电压,必须采用更大的存储单元。通过应用创新的设计技术,我们可以实现超过300毫伏的Vmin改善,这对于低功耗运行非常重要。

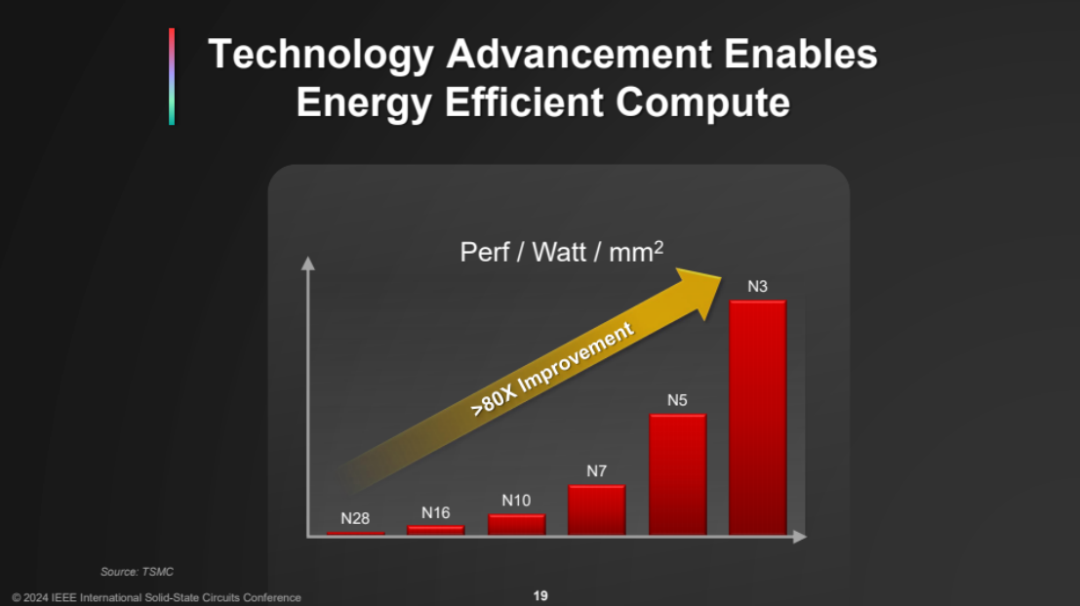

技术扩展的本质是为了节能计算。整个半导体行业走了很长一段路。上图展示十年多的规模,台积电实现了超过80倍的能源效率。

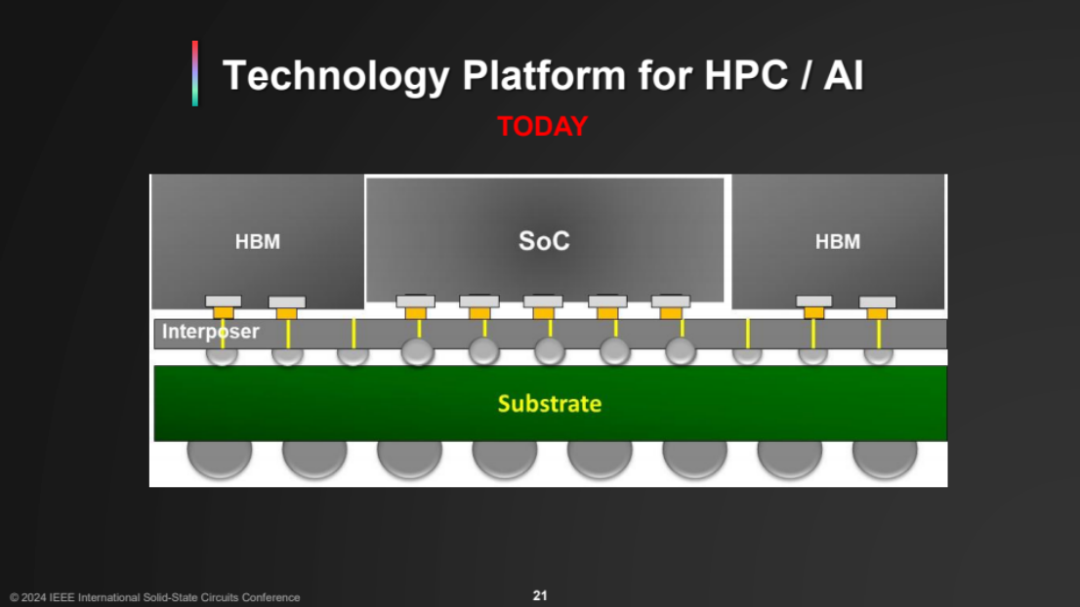

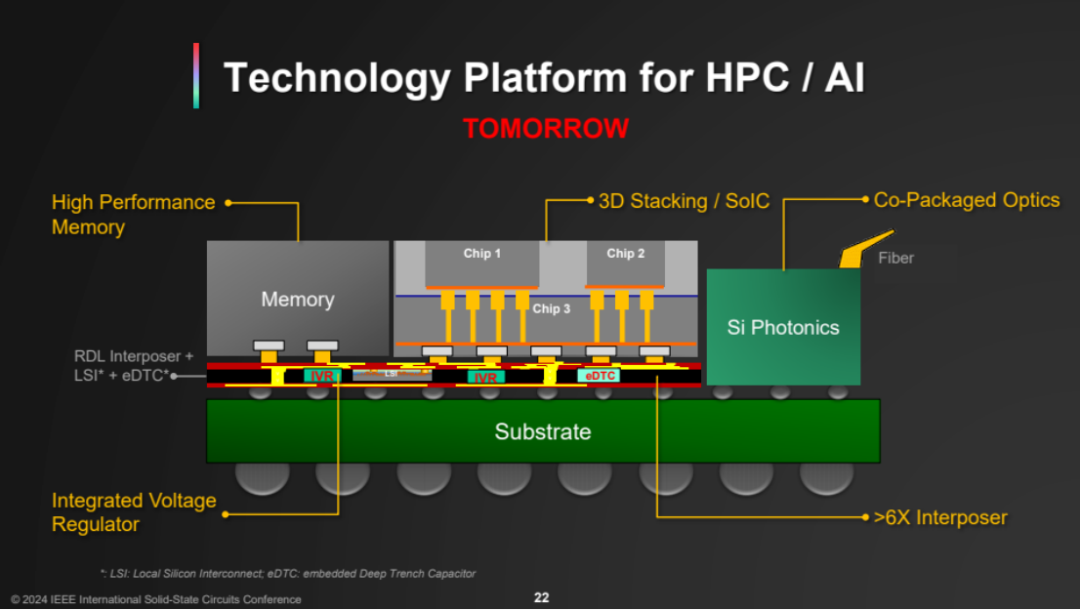

关于HPC和AI方面,如果看看今天所有的人工智能加速器,无论是GPU还是TPU或者是定制的ASIC,这些本质上是具有某种特定的集成方案。基本上,使用CowoS技术带来的先进芯片。如今主要是5nm技术和HBM在一起,Kevin Zhang认为这还远远不够。

展望未来,这个平台需要大幅提升以满足高性能计算的需求。因此,这种配置的核心实际上是更高密度、低能耗的计算。需要去栈才能达到计算密度,需要多个最先进的芯片垂直堆叠在一起,以提供所需的计算密度。并且还需要大量的内存,因此需要加入更多的HBM。这就是为什么,硅中介层和CoWoS必须进一步扩展。

这仍然不够,电力传输是一个问题,因此需要集成稳压器才能解决电力输送的挑战。I/O和带宽互联密度也是一个问题,因此需要将硅光子学引入封装中,这就是未来的发展方向。

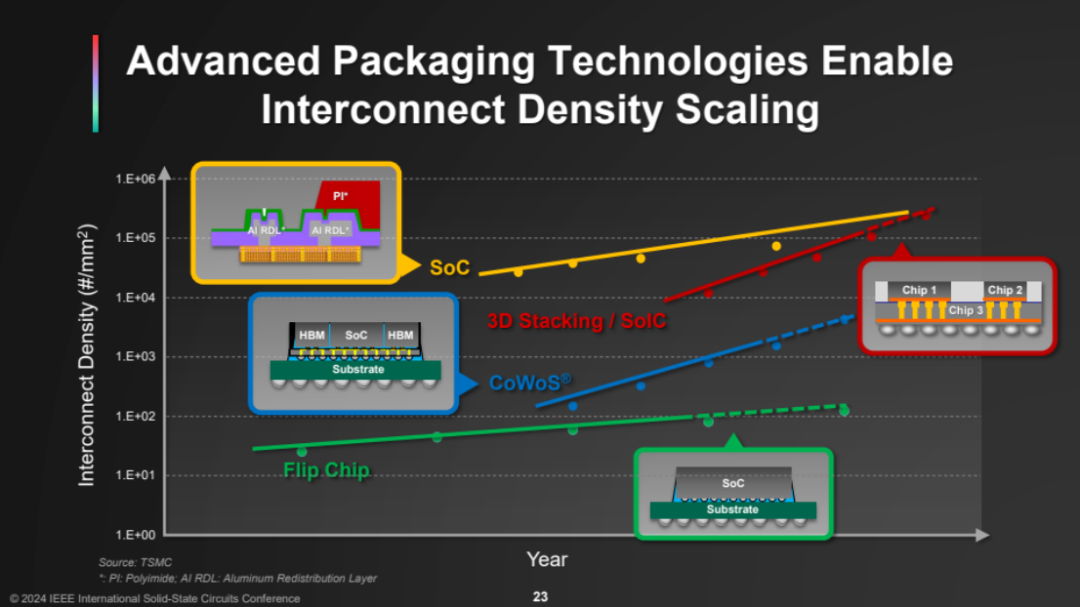

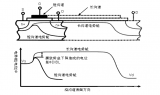

谈一谈3D堆叠,上图展示了互连密度。我们进行堆叠的原因是为了实现芯片到芯片之间的高密度互连。图中的曲线顶部曲线是SoC,本质上是单片互连。底部曲线是常规封装能够达到的密度。中间部分是CoWoS封装。

谈到3D 堆叠,Kevin Zhang展示一张图,并表示为达到更高的互连密度(Interconnect Density),即Chip To Chip 连结,透过3D 堆叠可以使接合的Pitch 一路缩小到几微米,实现单晶(Monolithic)的互连密度,“所以3D堆叠才是未来”。

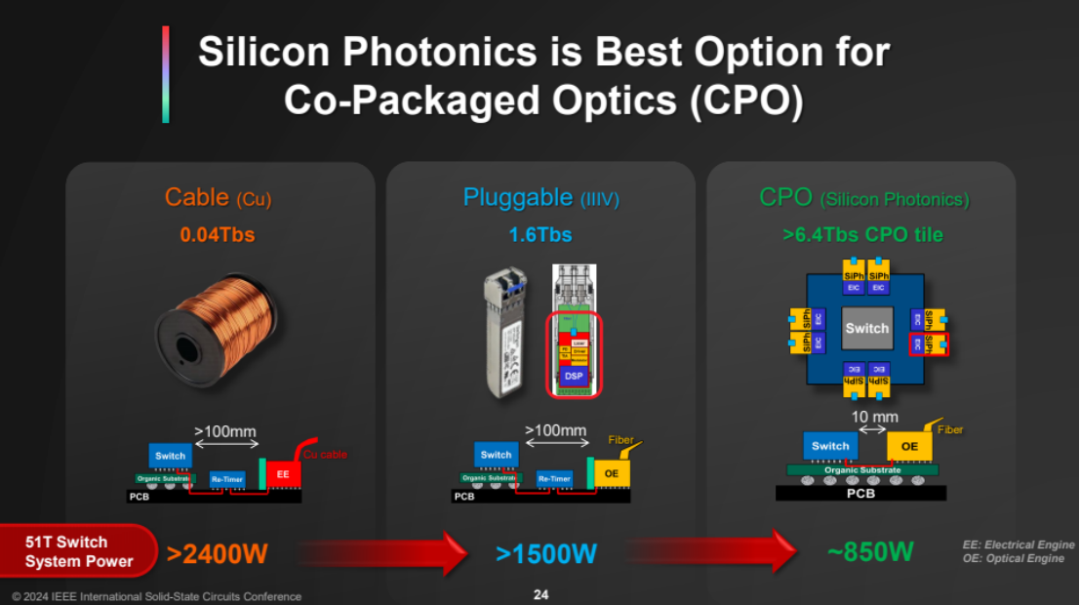

谈到硅光子/共封装光学(CPO)方面,Kevin Zhang指出,电子擅长运算,但光子在信号或通信时比较好。他以50T交换机举例,如果全都用电子并采用铜线材质的系统,会烧掉2,400 W。

目前解决方案是采用插拔式模组(Pluggable),可省下40% 功耗(> 1500W),但随着未来需要更高速信号、更大频宽,这远远不够,因此需要把硅光子技术把光子能力带进来。使用共封装光学的先进封装技术来正确实现光子功能。

在图示中,需要用先进堆叠技术,把光子芯片和电子芯片堆叠,可使功耗可再降低50%,约5 皮焦耳(picojoules per bit),使功耗约在850W。

如今,使用最先进的晶体管技术,我们可以将大约1000亿个晶体管封装在同一个芯片中,但这还不足以解决未来的AI机器学习应用。必须利用先进的3D封装技术,才能够将晶体管的数量真正增加到一万亿个,以满足计算需求。

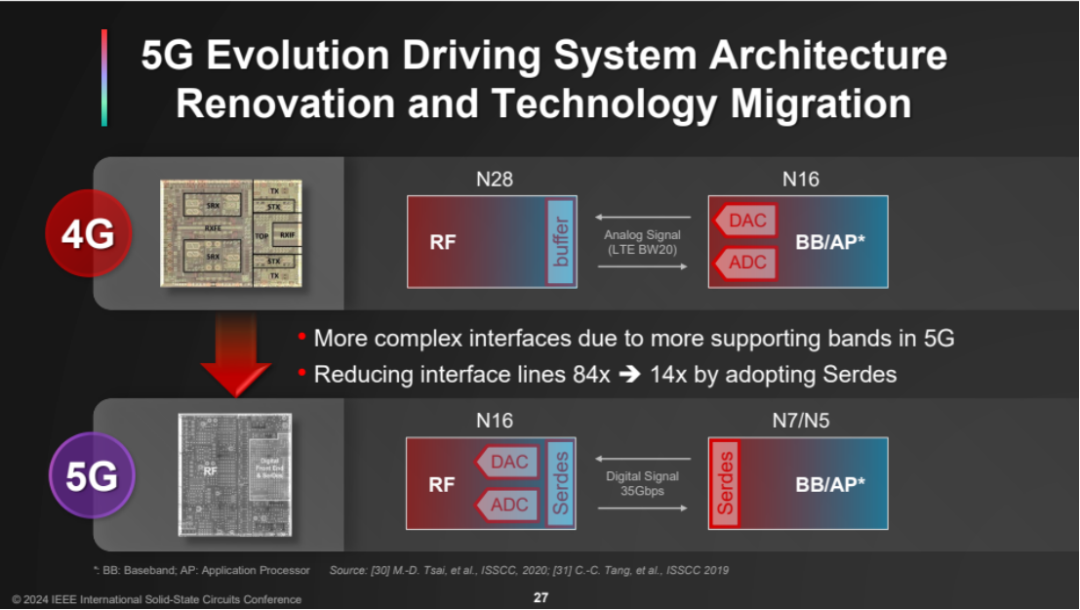

谈到蜂窝射频方面,他提到,当从4G向5G过渡时,为了将数据速率提高十倍,需要结合更多的数字电路,比如先进的ADC、先进的信号处理能力。在这样做时,射频设计、射频收发器设计都可从28nm发展到16nm中收益。

如果展望未来,比如6G,就需要覆盖更广泛的频率范围,与FR3一样需要提高数据速率。这就需要更先进的半导体,因此未来收发器的设计,如果使用7nm、5nm不必感到太过惊讶。

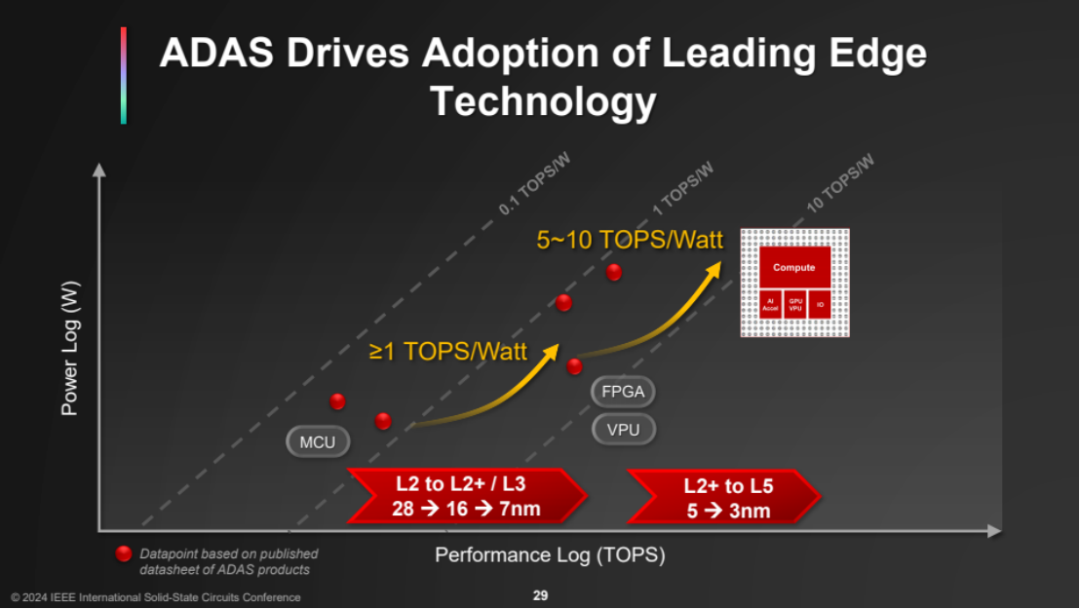

谈到汽车方面,从根本上看,最新的汽车技术需要大量运算能力,但功耗正成为问题,尤其是由电池供电的汽车。

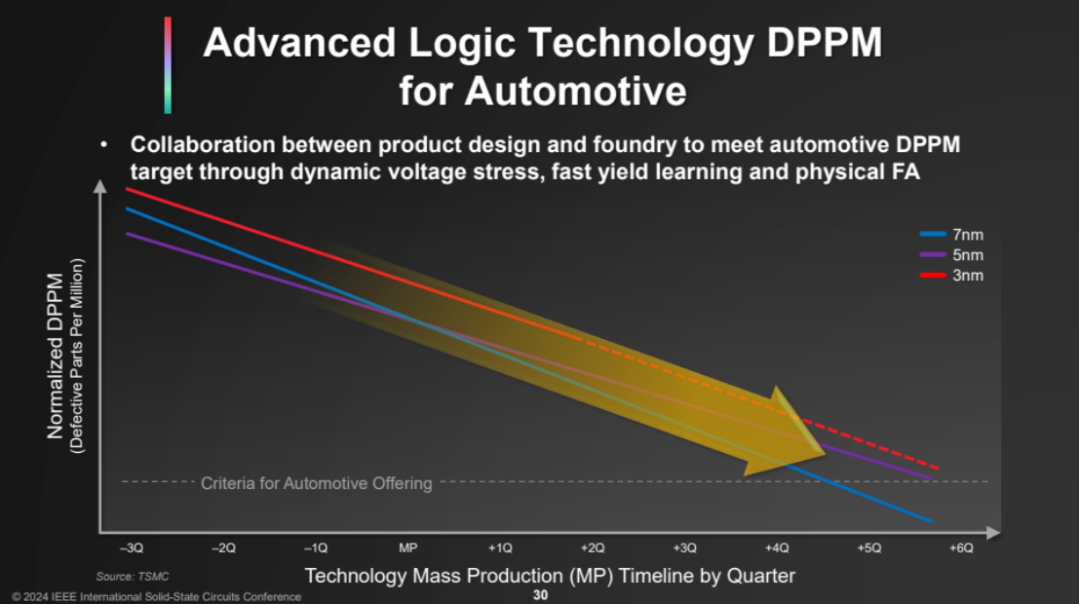

Kevin Zhang认为,车用半导体技术在导入上一直落后消费性或HPC 几个世代,是因为非常需要严格的安全性要求,汽车应用的DPPM(缺陷率)必须接近零,也因此晶圆厂、半导体制造和汽车设计人员必须更密切地合作,以加快这个速度。

台积电正在预先应用自动设计规则降低缺陷密度,Kevin Zhang承诺到:“在不久之后,你们会看到3nm导入汽车。”

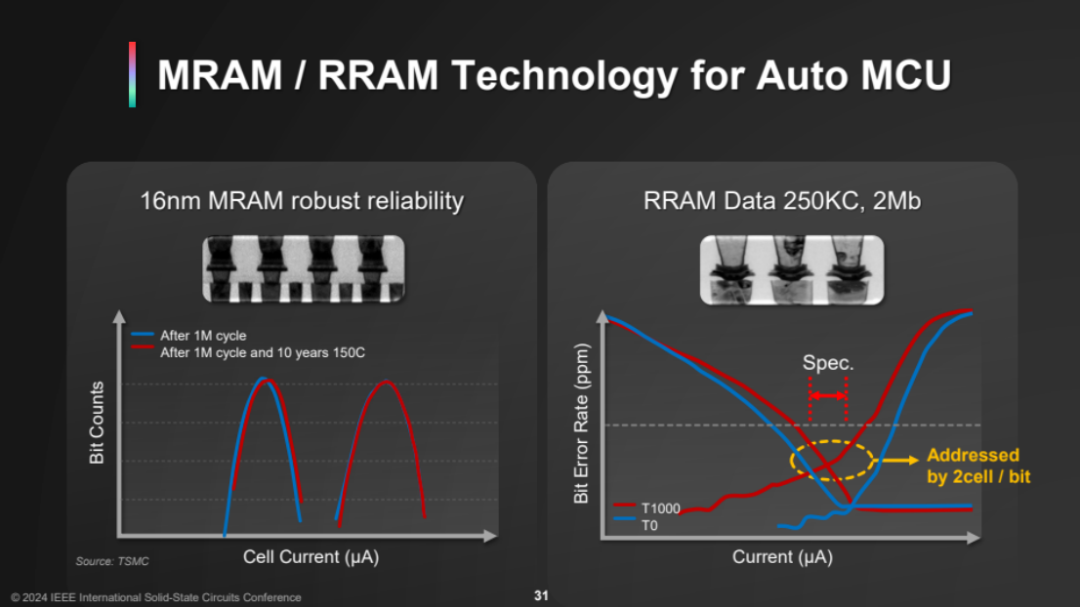

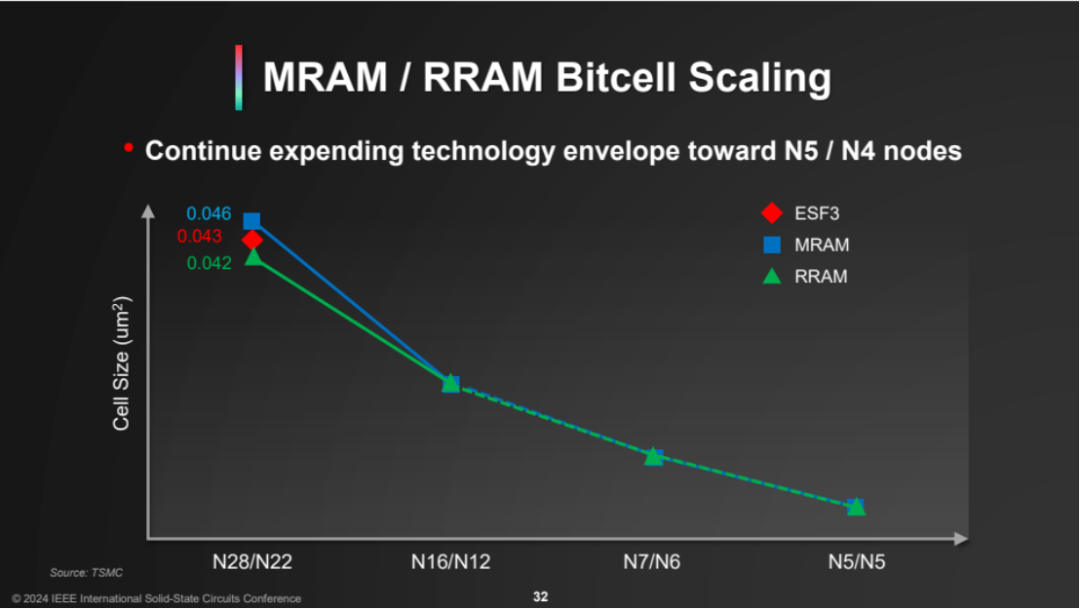

谈到MCU方面,MCU在汽车转型为区域架构后变更重要,也需要先进半导体技术给MCU 提供运算能力。传统MCU 大都采用浮动闸极(floating gate)为基础的技术,但浮动闸极技术在28 nm以下就卡关,所幸业界已经投资新内存技术,包括新的非挥发性存储器如磁性随机存取存储器(MRAM)或电阻式存储器(RRAM)。

也因此,从MCU 转移到MRAM、RRAM为基础的技术,有助于推动技术持续微缩,从28 nm缩小到16 nm、甚至是7 nm。

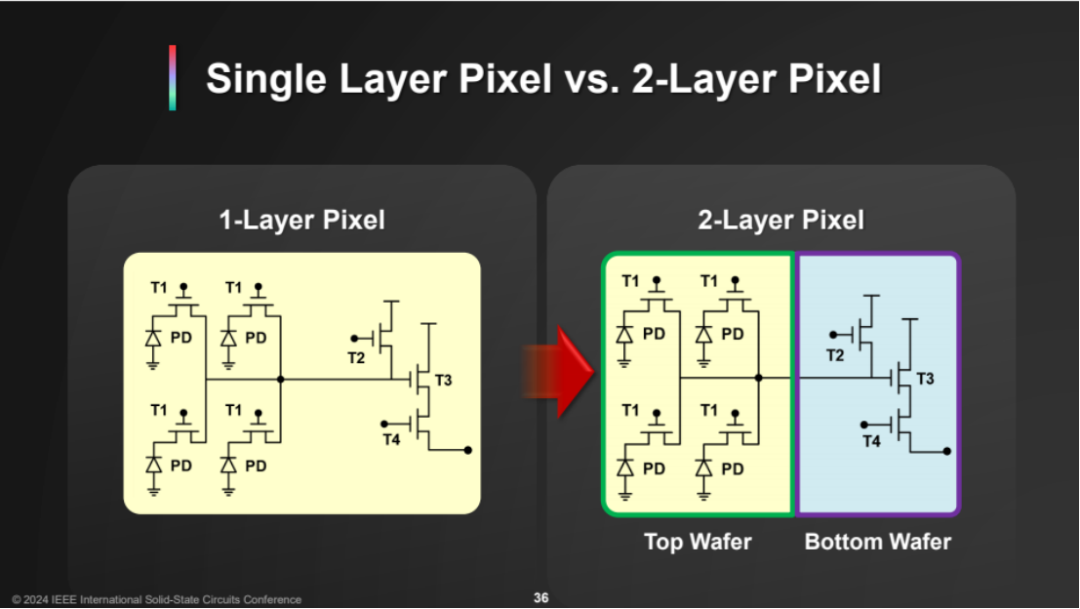

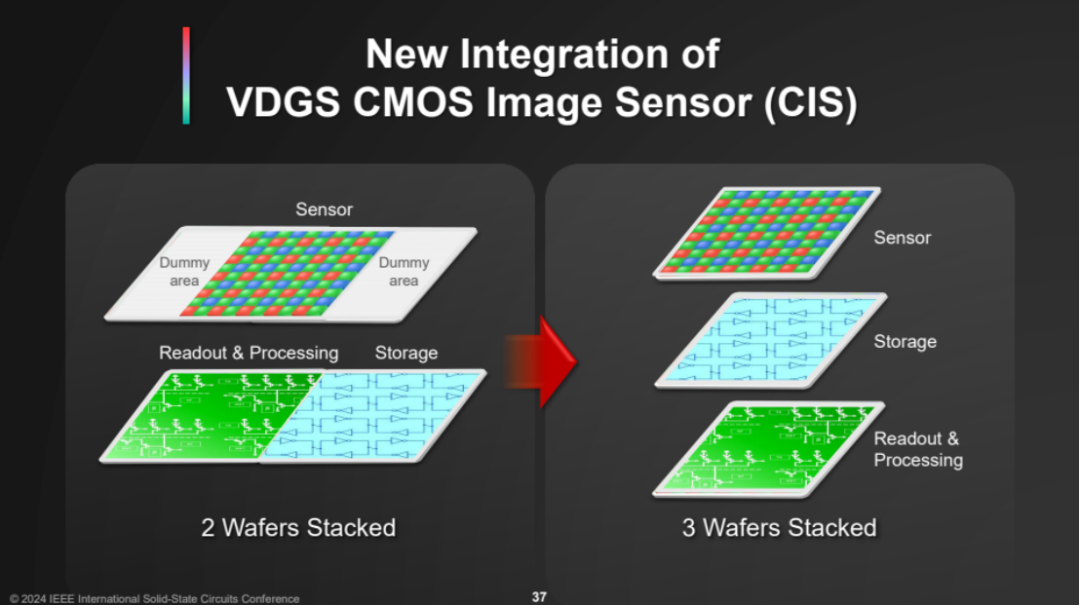

传感器和显示器方面,传感器技术从最简单的2D 设计、单层设计,到现在3D 晶圆堆叠的智能系统,基本上将信号处理层叠在传感层上。Kevin Zhang也表示:“我们技术已经开始投资、研究多层设计的技术。”

进行三层或多层设计能追求画素最佳化,继续推动画素尺寸缩小同时兼顾解析度需求,也能同时达到最佳传感能力;另一个例子是AR、VR,透过将不同层的存储器分开,再堆叠到其他逻辑芯片,可有效缩小尺寸,同时维持高效能需求。

最后Kevin Zhang分享自己的故事,他表示7 年前离开当时最大的半导体公司,去了中国台湾。他离开的时候心想,他的半导体黄金时代已经过去了,去亚洲是要迎接职涯的日落时刻,但时间快转7 年后,他表示:“我没看到日落,而是明亮的日出。随着AI 出现,半导体将驱动许多新应用,触及人类生活每一个面向,并改变人类历史的轨迹,所以我看到明亮、黄金的全新时刻,我们最好的日子还在前头,让我们一起努力使其成真。”

审核编辑:刘清

-

台积电

+关注

关注

44文章

5810浏览量

177054 -

晶体管

+关注

关注

78文章

10439浏览量

148610 -

机器学习

+关注

关注

67文章

8565浏览量

137226 -

ChatGPT

+关注

关注

31文章

1600浏览量

10393

原文标题:最新!ISSCC 2024台积电谈万亿晶体管,3nm将导入汽车

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

台积电拟投资170亿,在日本建设3nm芯片工厂

台积电2026年资本支出激增,应对AI驱动产能危机

1.4nm制程工艺!台积电公布量产时间表

漏致势垒降低效应如何影响晶体管性能

台积电2纳米制程试产成功,AI、5G、汽车芯片,谁将率先受益?

台积电Q3净利润4523亿元新台币 英伟达或取代苹果成台积电最大客户

台积电2纳米制程试产成功,AI、5G、汽车芯片

台积电预计对3nm涨价!软银豪掷54亿美元收购ABB机器人部门/科技新闻点评

ISSCC 2024台积电谈万亿晶体管,3nm将导入汽车

ISSCC 2024台积电谈万亿晶体管,3nm将导入汽车

评论