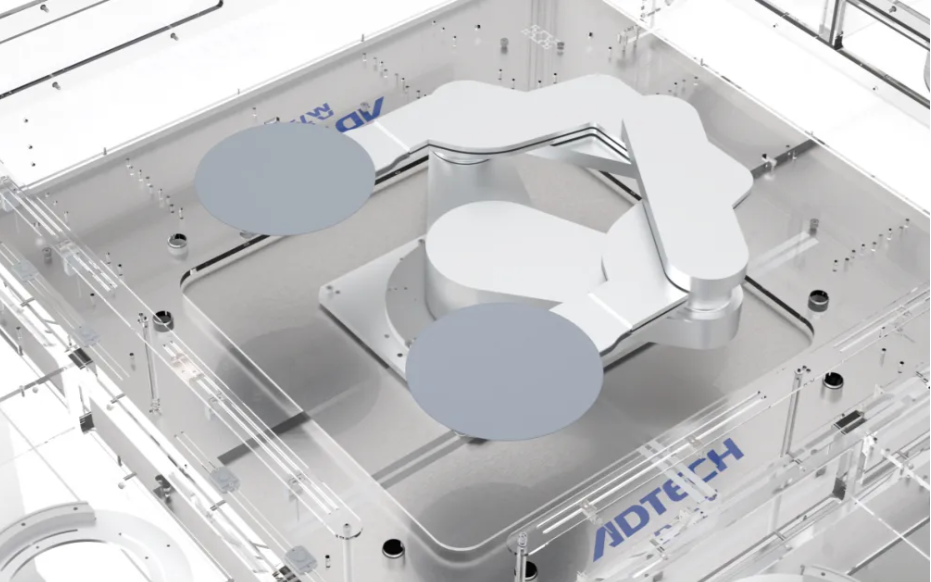

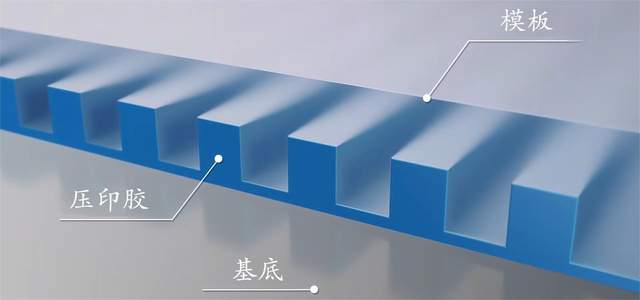

佳能去年10月发布了采用纳米压印技术的FPA-1200NZ2C,该设备工作原理区别于传统光刻机,无须依赖光学图像投影实现芯片微观结构转移,而更接近印刷工艺,通过压制印出图案,能制造出5nm芯片。

佳能近日表示,计划年内或明年上市使用纳米压印技术的光刻设备FPA-1200NZ2C。对比已商业化的EUV光刻技术,虽然纳米压印的制造速度较传统方式缓慢,但由于制程简化,耗电仅为EUV的十分之一,且投资额也仅为EUV设备的四成。因此,佳能此举有望击败市场竞争对手,使得高端芯片生产价格更为亲民。

该项目由佳能工业部门负责人竹西宏明亲自领导。宏明明确表示:“期望今年或明年在市场热度下启动出货。这一独特技术,将助力尖端芯片生产变得更为简易和经济实惠。”他还指出,这项关键性技术成功与否的关键在于能否打动潜在客户,使他们愿意将其引入现有生产线。

据悉,初步阶段,佳能将利用该技术生产3D NAND存储器芯片,并非复杂的处理器。宏明透露,佳能在15年时间内持续研发这一领域,若能成功实现商业化应用,有望扭转竞争态势,帮助新兴企业以更低的成本打造领军半导体产品。然而,新设备的缺陷率、集成难度以及地缘政治影响等因素,仍需考量其中,才能确定佳能能否在此次重大竞争中突出重围。

-

佳能

+关注

关注

3文章

395浏览量

40483 -

EUV

+关注

关注

8文章

614浏览量

88525 -

纳米压印

+关注

关注

0文章

13浏览量

6650

发布评论请先 登录

重塑话语权:新时达硬核技术为中国半导体制造打通自主可控关键链路

BW-4022A半导体分立器件综合测试平台---精准洞察,卓越测量

【「AI芯片:科技探索与AGI愿景」阅读体验】+半导体芯片产业的前沿技术

研华科技如何重塑智能制造未来格局

下一代高速芯片晶体管解制造问题解决了!

压电纳米定位系统如何重塑纳米压印精度边界

佳能推出5nm芯片制造设备,纳米压印技术重塑半导体竞争格局

佳能推出5nm芯片制造设备,纳米压印技术重塑半导体竞争格局

评论