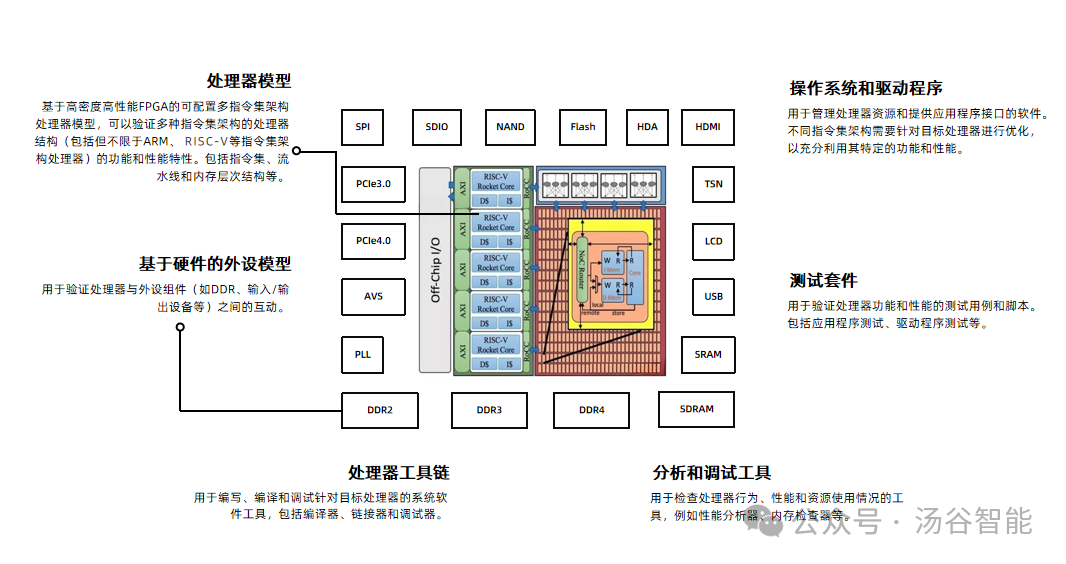

面向高性能计算、IoT、无线接入、音频、多媒体、消费类电子、边缘计算等迅速扩展的RISC-V使用场景,汤谷智能发布了基于自研Logic Giant原型验证硬件平台的全栈RISC-V硬件仿真加速系统方案。

方案可支持阿里玄铁、香山南湖等多款常用RISC-V Core,并同时支持Verilog及Chisel等多种设计语言,配合自研TGOriPartition软件工具,支持多核、大规模分割。支持MCU到AP多个处理器级别,流水线从2级到12级。方案支持基于RISC-V的SoC系统,常用外设齐全,可通过EDA工具选择不同的RISC-V Core和外设,自动生成可直接在原型平台运行的SoC系统,支持适配SoC系统的驱动软件及操作系统运行,极大提高开发效率。

从客户使用效果来看,方案可同时支持8路以上可编程独立时钟源,每一路都能支特全局时钟同步,传输距离为1.5米时,采用LVDS 传输性能可大于1.6Gbps,延迟小于900ps。采用自研的互联IP总线和电缆,超低延迟可同时运行512个RISC-V Core并保持系统统一同步运行,系统主频可达到8~10MHZ以上。

为了支持多个用户的同时使用的场景,方案中单个机箱可支持几十个虚拟用户和真实5用户同时使用,特别是真实5用户可动态独立使用分配到的FPGA逻辑资源,不与其他用户从逻辑、时钟、复位和外设等各种资源产生冲突。

审核编辑:汤梓红

-

处理器

+关注

关注

68文章

20346浏览量

255392 -

仿真

+关注

关注

55文章

4543浏览量

138718 -

RISC-V

+关注

关注

49文章

2961浏览量

53619

原文标题:汤谷智能发布国产化全栈RISC-V硬件仿真加速系统方案

文章出处:【微信号:汤谷智能,微信公众号:汤谷智能】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

深开鸿全栈赋能!开源鸿蒙/RISC-V大赛晋级培训圆满收官

思尔芯、MachineWare与Andes晶心科技联合推出RISC-V协同仿真方案,加速芯片开发

重磅合作!Quintauris 联手 SiFive,加速 RISC-V 在嵌入式与 AI 领域落地

新思科技全栈工具链助力RISC-V设计高效进阶

探索RISC-V在机器人领域的潜力

2025 RISC-V产业发展大会 | 赛昉科技全景展示规模化商用成果

为什么RISC-V是嵌入式应用的最佳选择

硬核加速,软硬协同!混合仿真赋能RISC-V芯片敏捷开发

润开鸿亮相2025 RISC-V中国峰会

RISC-V芯片出货超百亿颗!四大厂商重磅产品来袭,加速边缘AI终端落地

芯华章RISC-V敏捷验证方案再升级

RISC-V 发展态势与红帽系统适配进展

RISC-V 的平台思维和生态思维

DC-ROMA RISC-V AI PC 正式发布!

汤谷智能发布全栈RISC-V硬件仿真加速系统方案

汤谷智能发布全栈RISC-V硬件仿真加速系统方案

评论