前不久,美国应用材料公司(Applied Materials)工艺整合工程师张子辰和合作者基于氮化硅薄膜的固态转移掺杂技术,开发出一种碳纳米管 N 型场效应晶体管,它能与晶体管的延伸区直接接触。相关论文以“Complementary carbon nanotube metal-oxide-semiconductor field-effect transistors with localized solid-state extension doping”为题发表在《 Nature Electronics》。

原文链接:https://www.nature.com/articles/s41928-023-01047-2

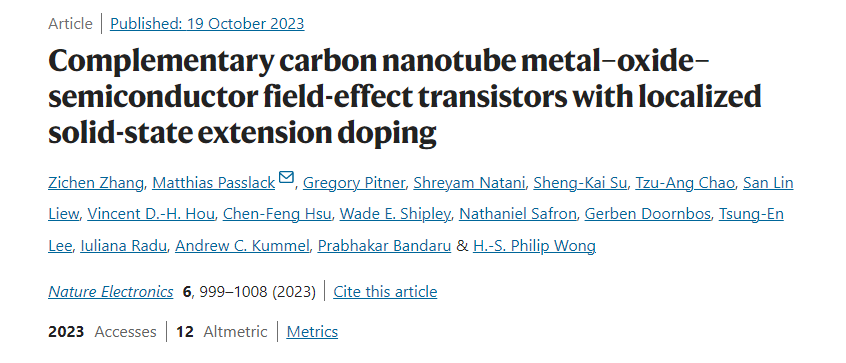

研究中,他们提出了一种顶栅互补碳纳米管金属-氧化物-半导体场效应晶体管结构(Top Gate complementary CNT MOSFETs)。在该结构中,通过将掺杂仅仅局限在延伸部分,而在通道保持未掺杂的状态,凭借这一架构课题组消除了金属电极的重叠、以及相关的寄生电容,此外,他们还使用高电阻率的硅衬底,以便实现最小化的寄生衬底电容。同时,其还在芯片上实现了零开路和零短路的校准结构,让所测得的 Cg-Vg 特性,能与任何剩余的寄生电容分量分离。从而实现了P 型和 N 型半导体器件的性能匹配,获得了 P 型和 N 型的场效应晶体管。

器件结构和电学特性(来源:Nature Electronics)

这些晶体管的器件结构,让其可以更准确地提取固有器件参数。同时,本次工作也解决了碳纳米管均匀可控的掺杂问题,能帮助人们更好地提升碳纳米管半导体器件的性能。

-

晶体管

+关注

关注

78文章

10441浏览量

148612 -

寄生电容

+关注

关注

1文章

303浏览量

20372 -

碳纳米

+关注

关注

0文章

17浏览量

7718

原文标题:碳纳米管晶体管兼容已有半导体制程工艺,解决碳纳米管均匀可控掺杂难题

文章出处:【微信号:DT-Semiconductor,微信公众号:DT半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体晶体管的发明历史

晶体管的定义,晶体管测量参数和参数测量仪器

台积电引领全球半导体制程创新,2纳米制程备受关注

Keithley 2450数字源表纳米级材料测试的精密利器

半导体分层工艺的简单介绍

晶体管架构的演变过程

晶体管光耦的工作原理

下一代高速芯片晶体管解制造问题解决了!

薄膜晶体管技术架构与主流工艺路线

什么是晶体管?你了解多少?知道怎样工作的吗?

半导体芯片中的互连层次

碳纳米管晶体管兼容已有半导体制程工艺,解决碳纳米管均匀可控掺杂难题

碳纳米管晶体管兼容已有半导体制程工艺,解决碳纳米管均匀可控掺杂难题

评论