共读好书

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54463浏览量

469619 -

逻辑芯片

+关注

关注

1文章

167浏览量

32271

发布评论请先 登录

相关推荐

热点推荐

【「龙芯之光 自主可控处理器设计解析」阅读体验】--LoongArch逻辑综合、芯片设计

,关于逻辑综合流程的步骤及实现过程,可以参考书籍相关部分。

二.可测试型设计

可测试性设计(Design For Testability,DFT)主要是通过在芯片中加入可测试性逻辑电路

发表于 01-18 14:15

外延片氧化清洗流程介绍

外延片氧化清洗流程是半导体制造中的关键环节,旨在去除表面污染物并为后续工艺(如氧化层生长)提供洁净基底。以下是基于行业实践和技术资料的流程解析:一、预处理阶段初步清洗目的:去除外延

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

由同一个栅极控制,其结构如图4所示。

此配置既可以采用鳍片对鳍片结构,也可采用其他的结构。

图4 CFET结构示意图

长期以来,芯片上的信号线和电源供电线都是放在硅晶圆的正面,见图5所示。

随着

发表于 09-06 10:37

铲齿散热片CNC加工:精密制造赋能高效散热解决方案

随着电子设备性能的提升,散热问题成为影响设备稳定性的关键因素。铲齿散热片作为一种高效散热组件,通过CNC加工技术实现了精密制造与高效散热的完美结合,广泛应用于通信、汽车、工业控制等领域。 工艺流程

芯片制造中解耦等离子体氮化工艺流程

在5纳米以下的芯片制程中,晶体管栅极介质层的厚度已缩至1纳米以下(约5个原子层)。此时,传统二氧化硅(SiO₂)如同漏水的薄纱,电子隧穿导致的漏电功耗可占总功耗的40%。

VirtualLab Fusion:平面透镜|从光滑表面到菲涅尔、衍射和超透镜的演变

)讲座的文字记录和演示文稿。

1.平面透镜的潜力与局限性

幻灯片 #2-5

在本文的开头,我打算探讨一个问题:将平面透镜集成到光学设计中可以期待什么样的结果?为了回答这个问题,有必要介绍一些与平面

发表于 05-15 10:36

PanDao:简化光学元件制造流程

显示,在10,000片批量生产条件下,单件成本为69欧元(图1)。系统推荐采用磁流变抛光技术加工非球面侧,使用数控抛光处理球面侧。

图1.75mm直径非球面弯月透镜的制造链调制流程示意图(图片来源

发表于 05-08 08:46

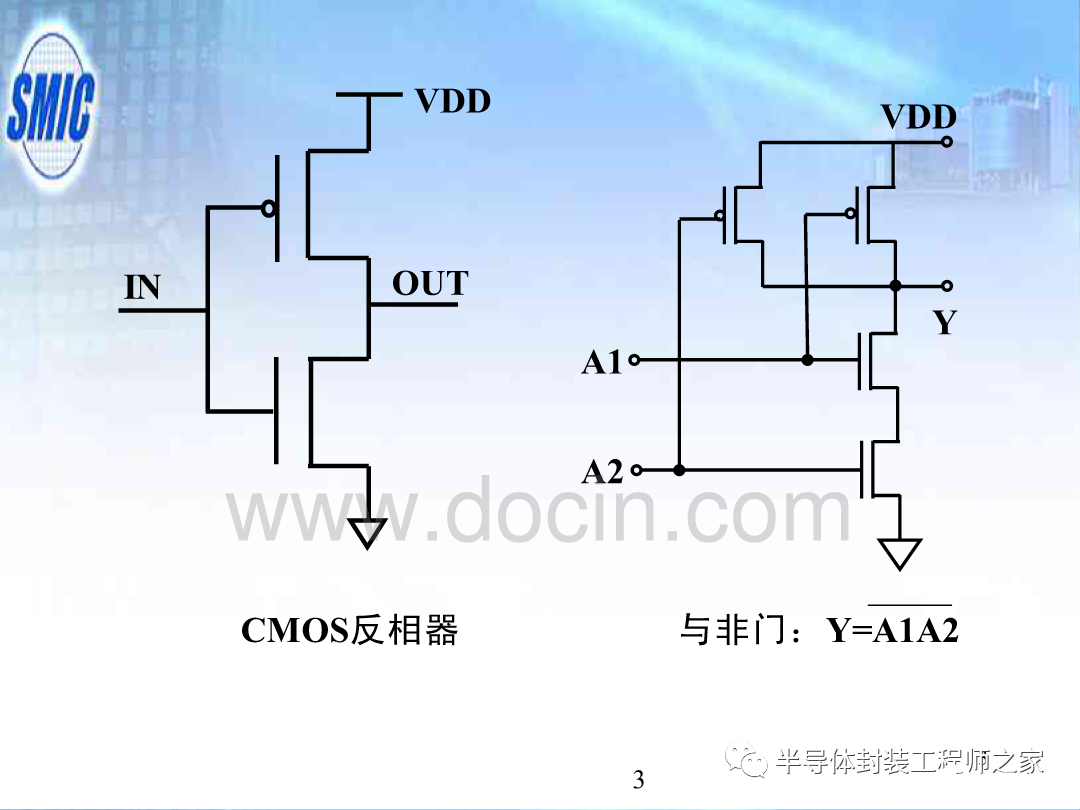

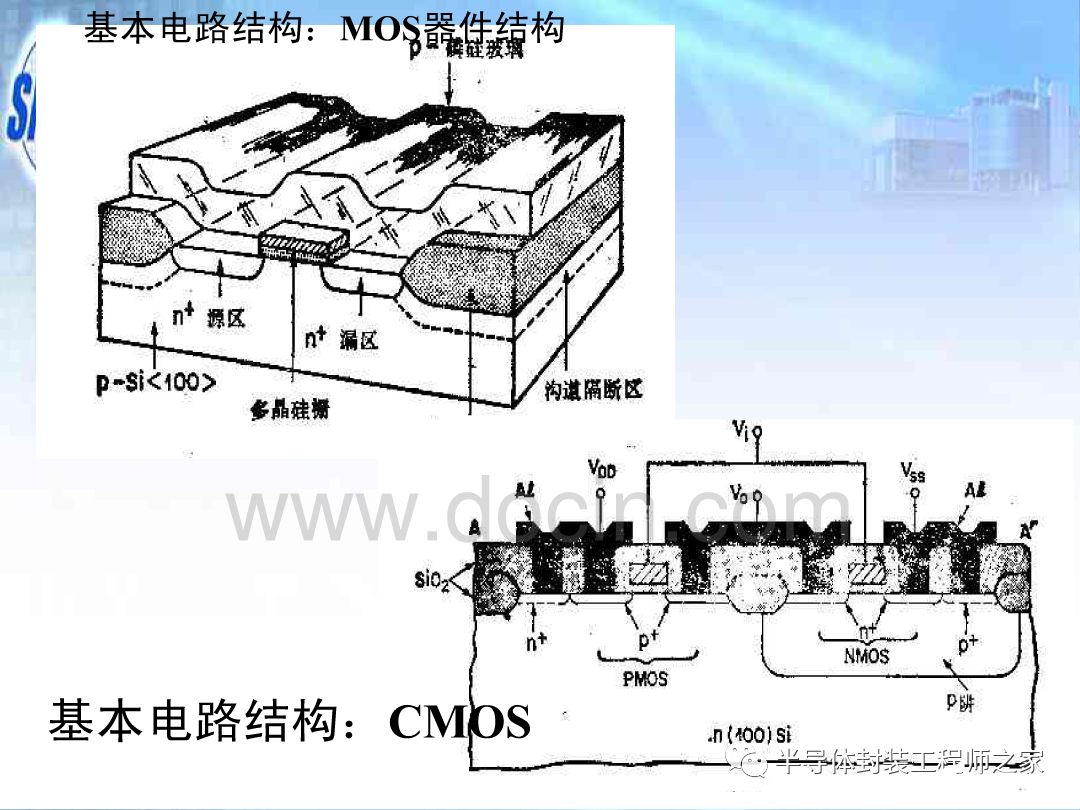

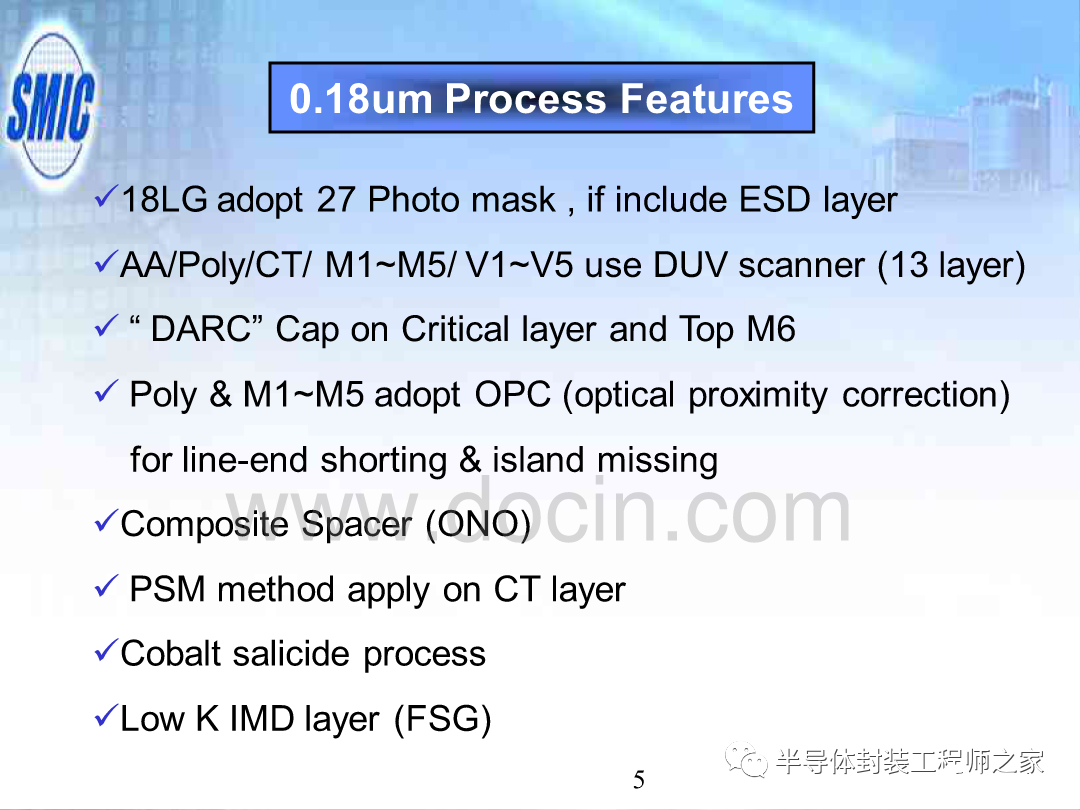

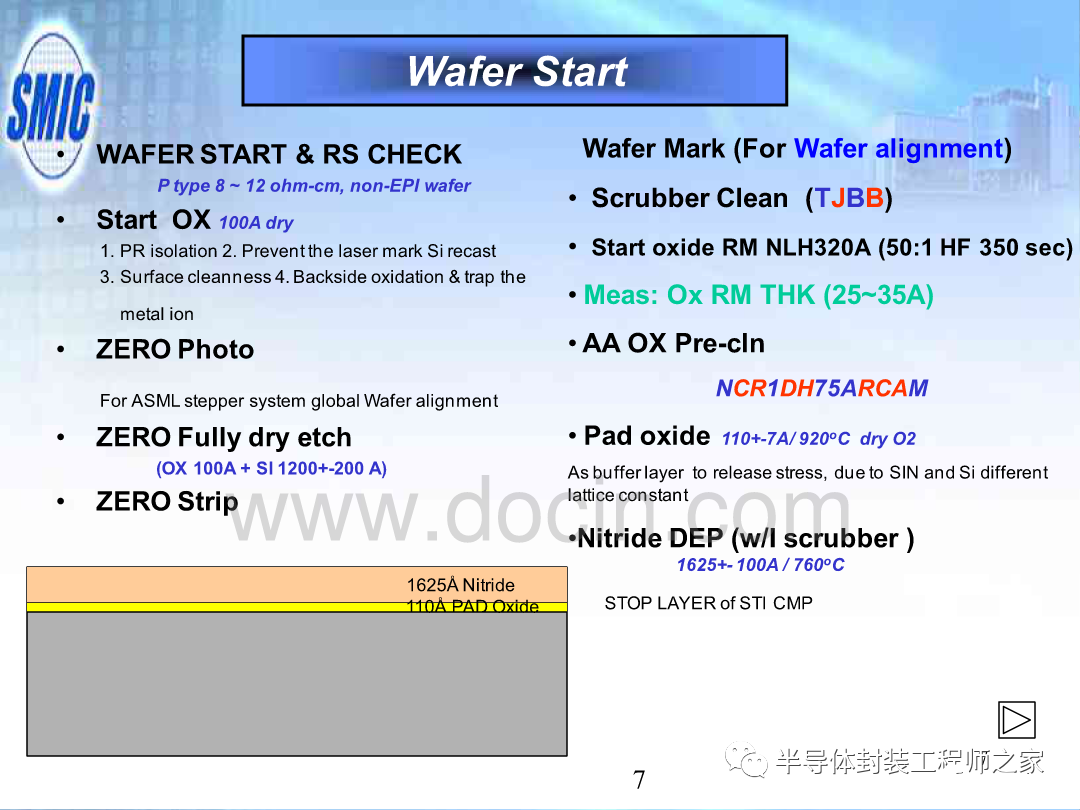

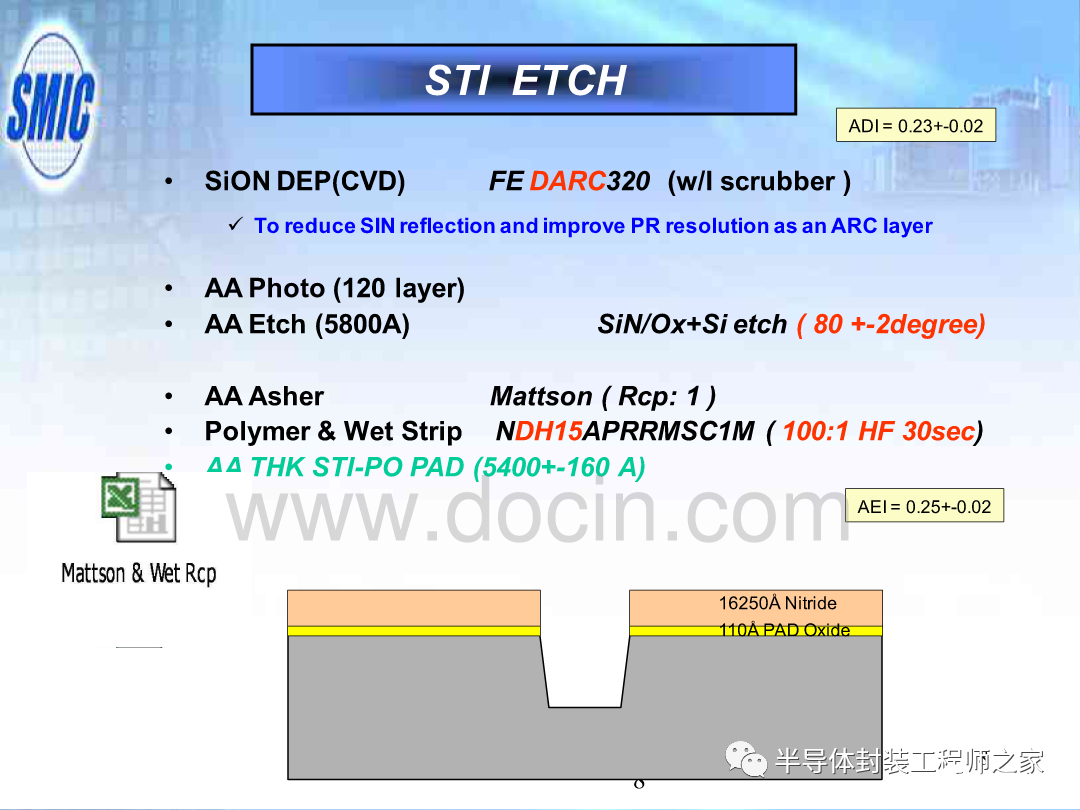

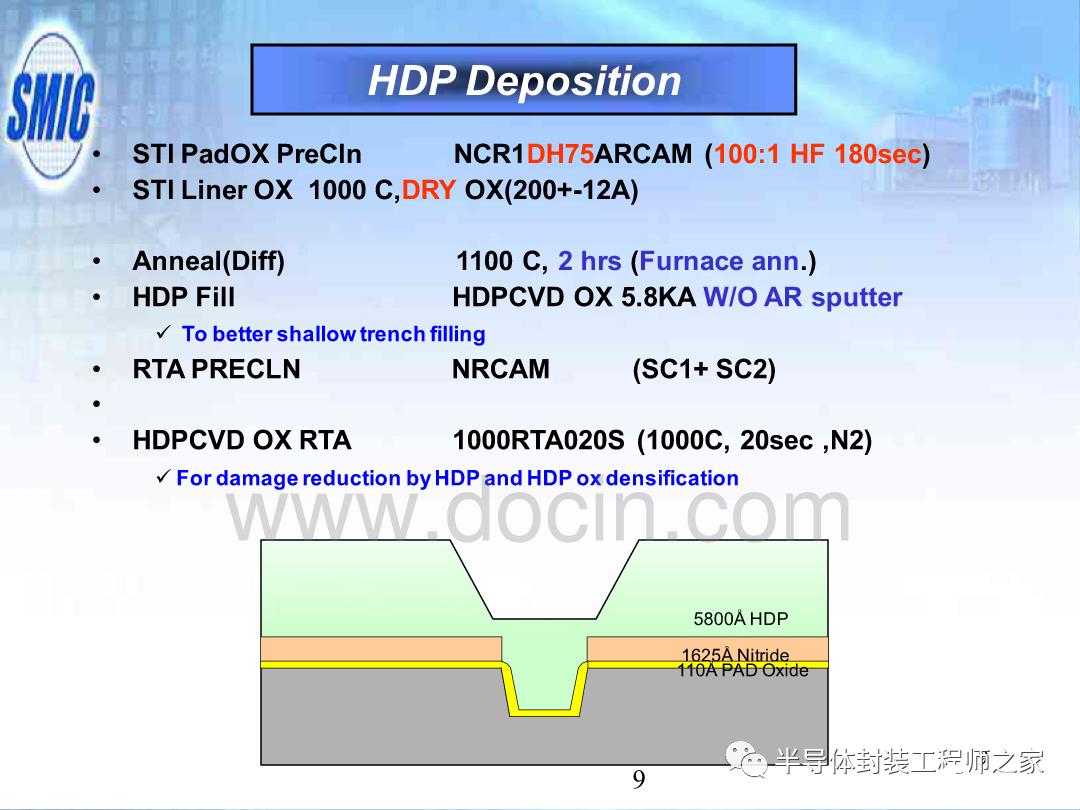

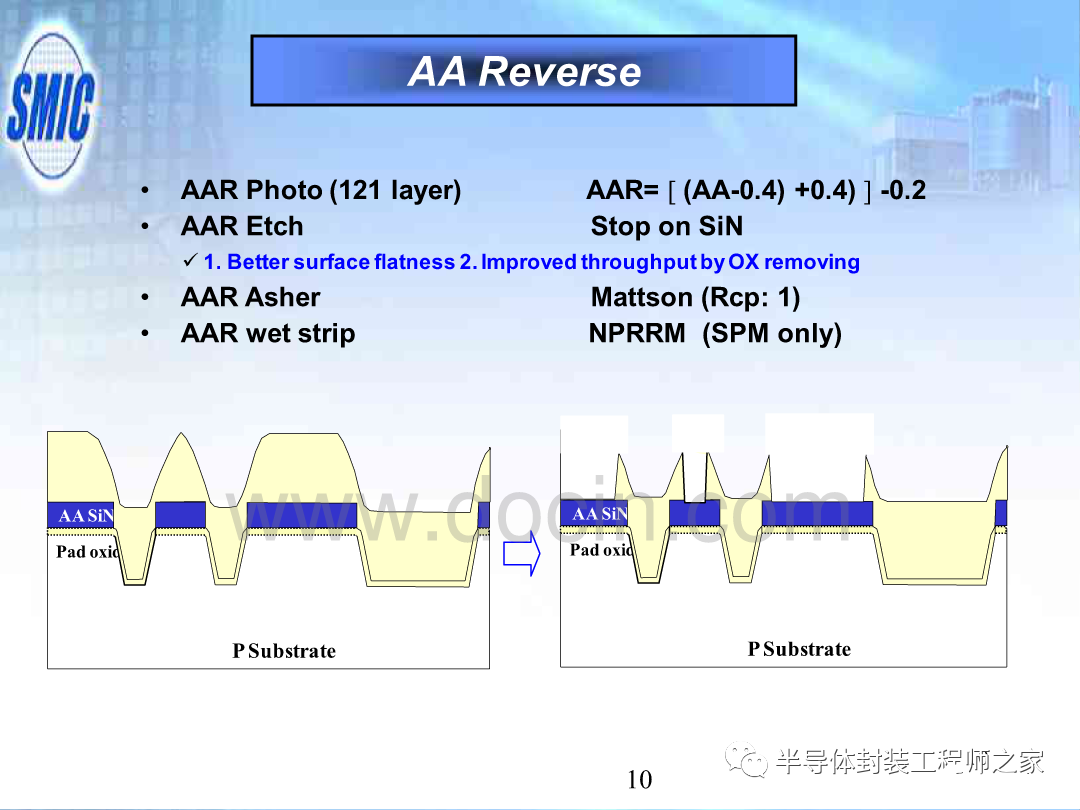

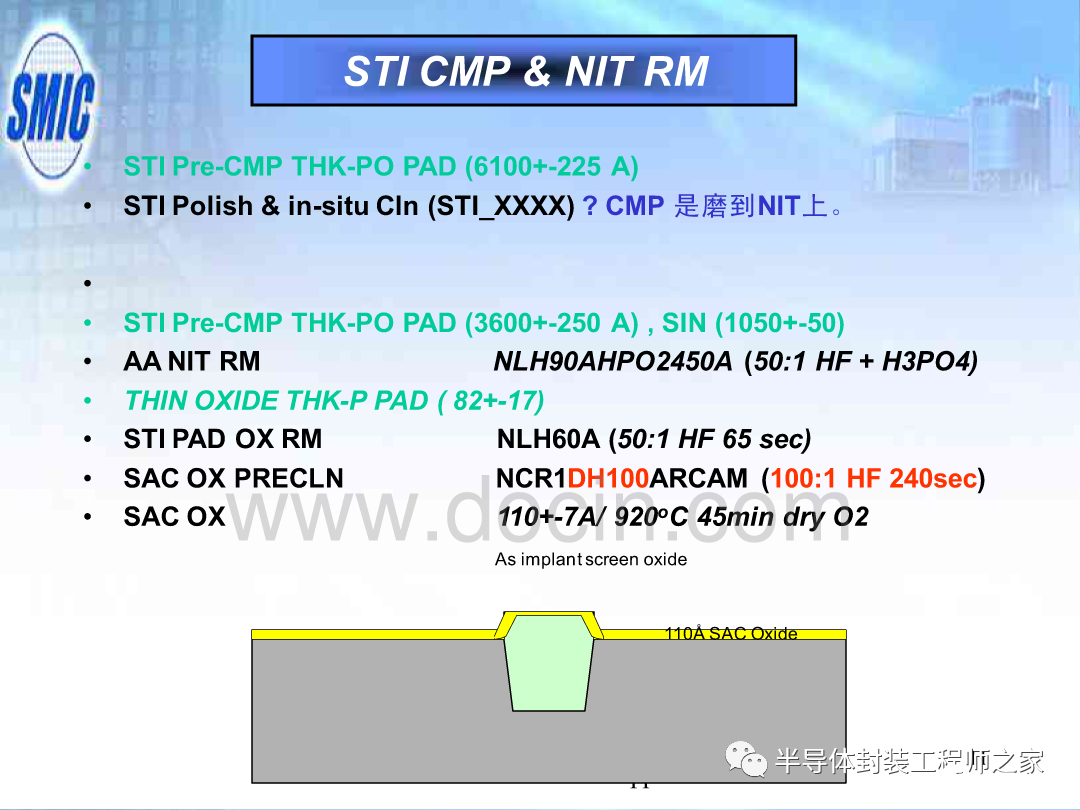

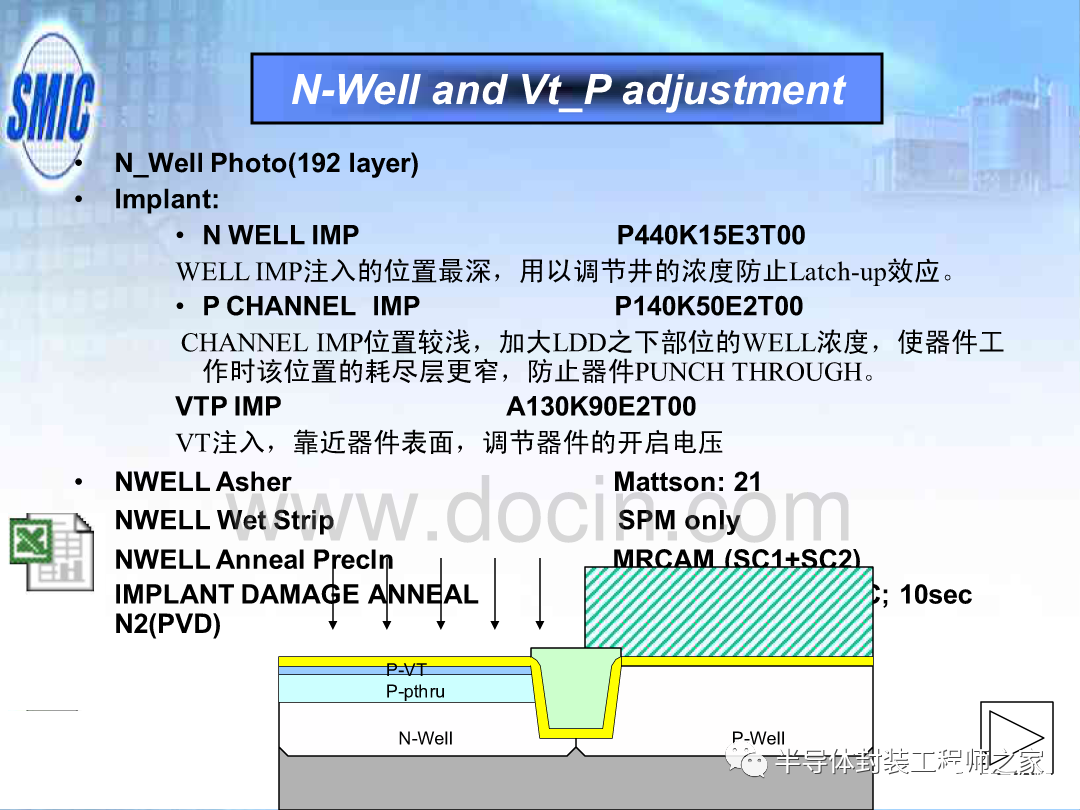

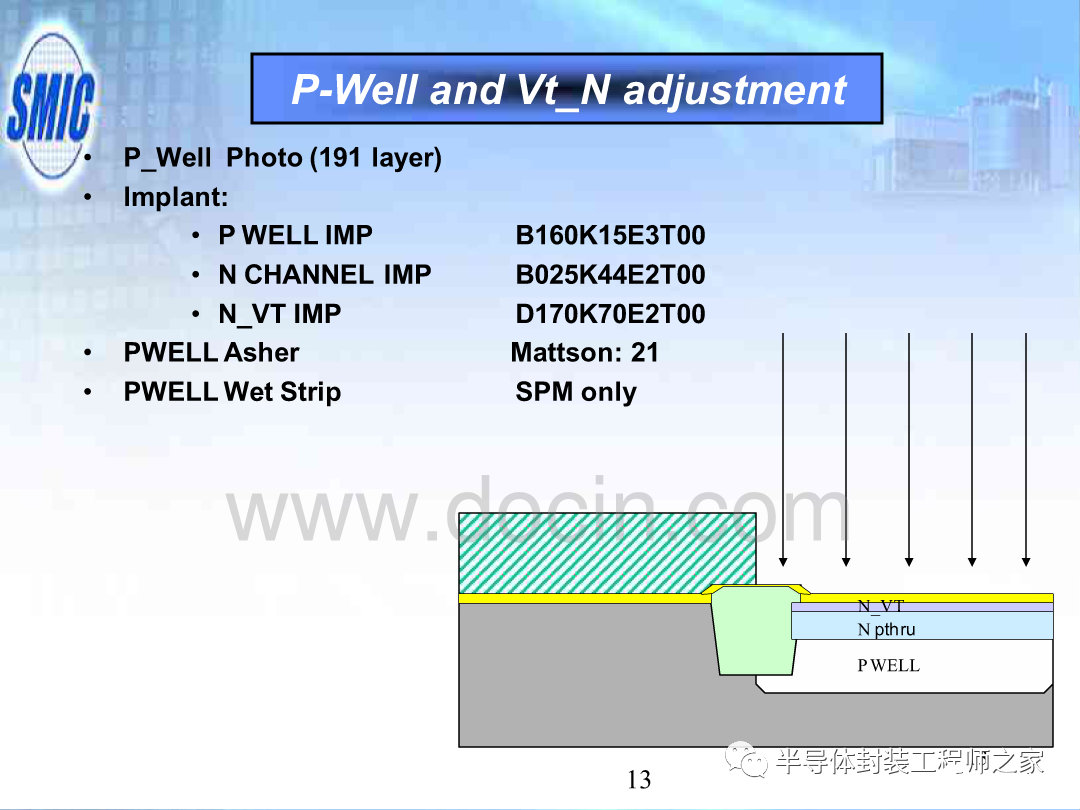

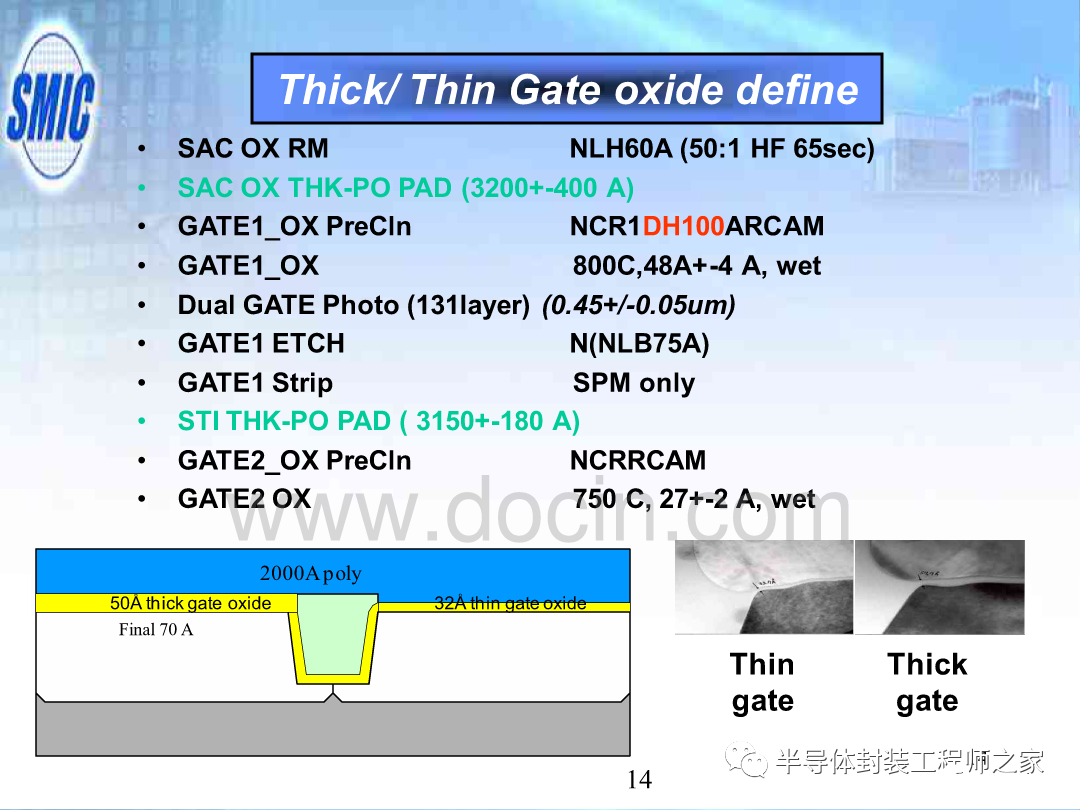

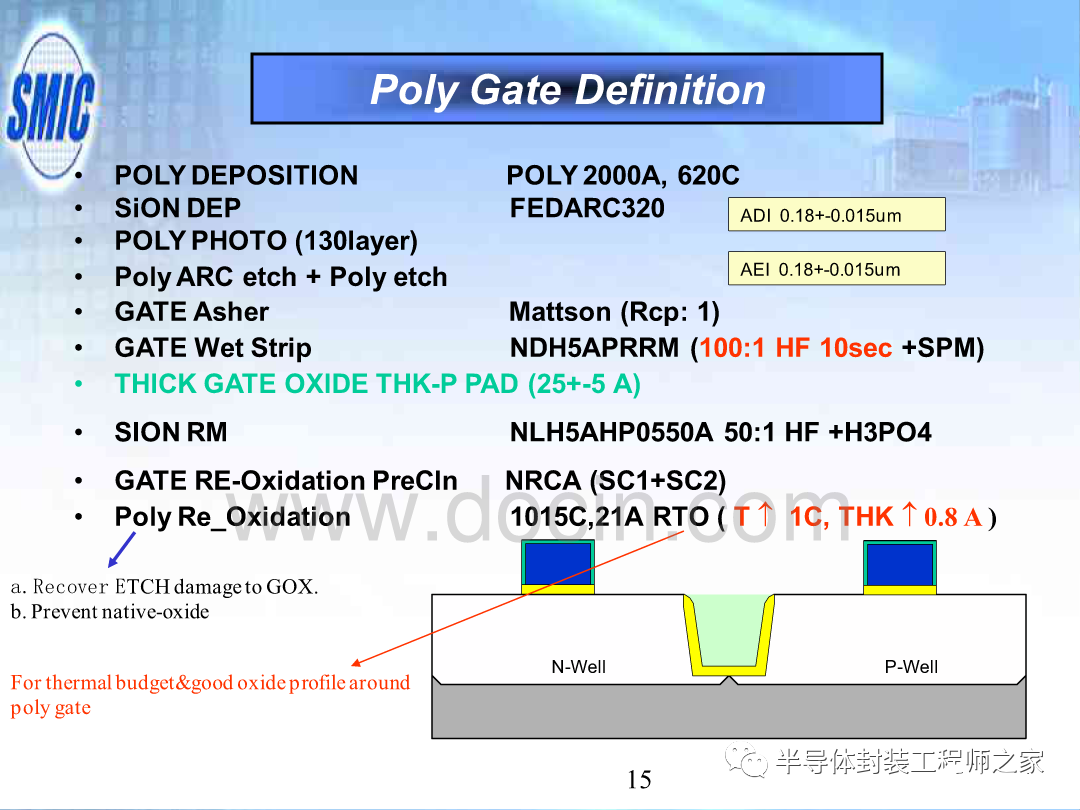

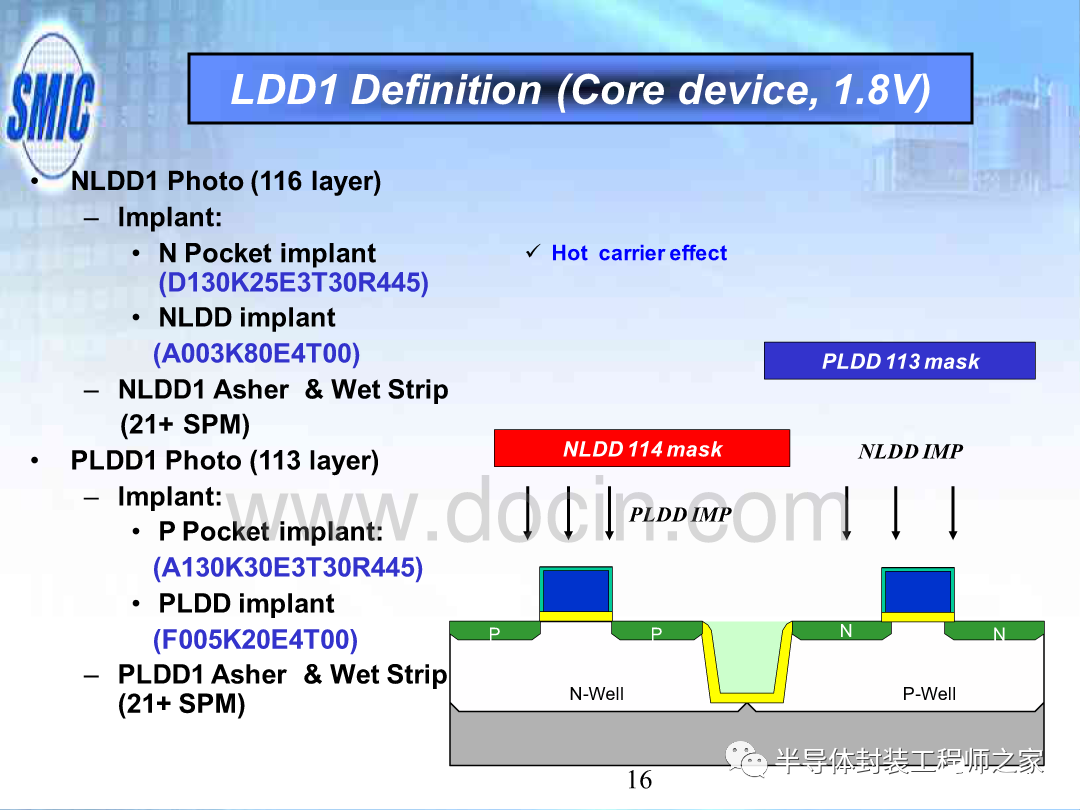

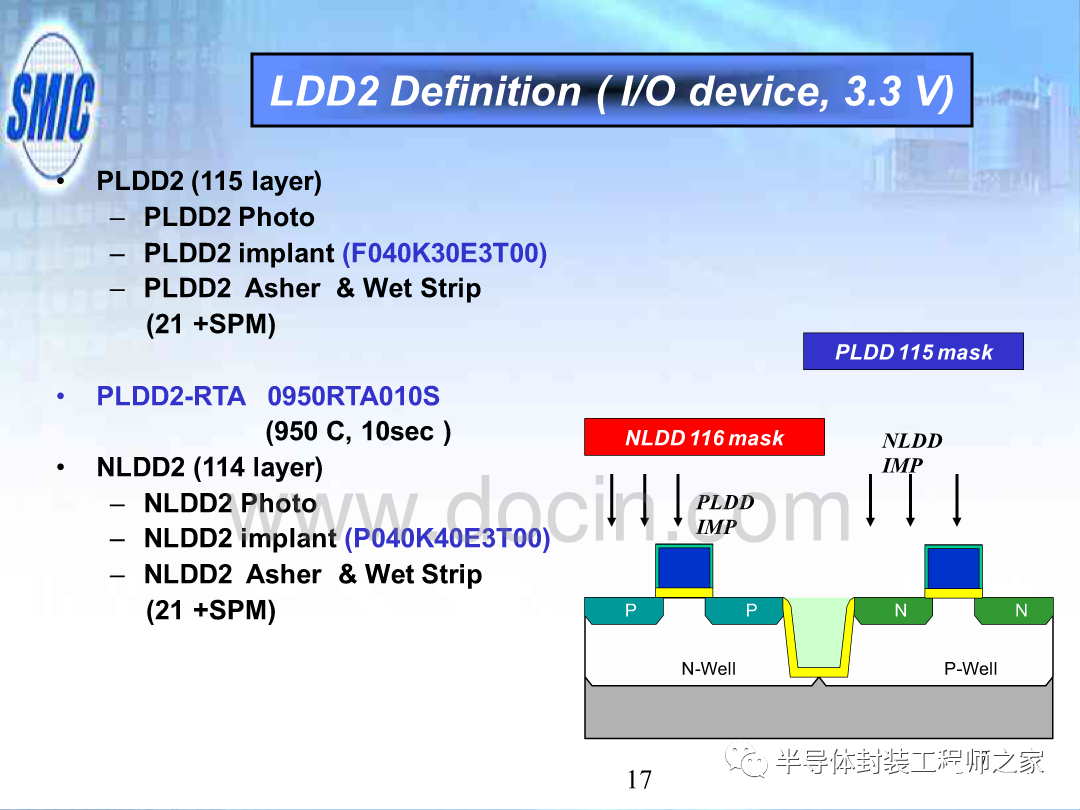

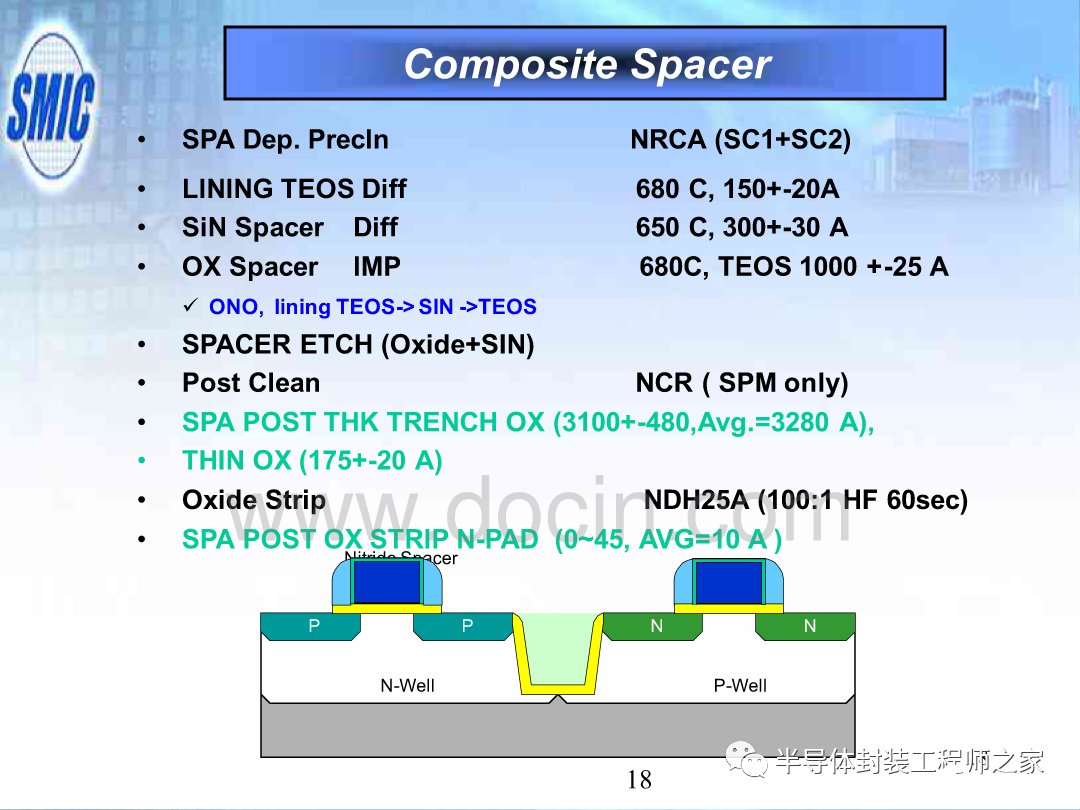

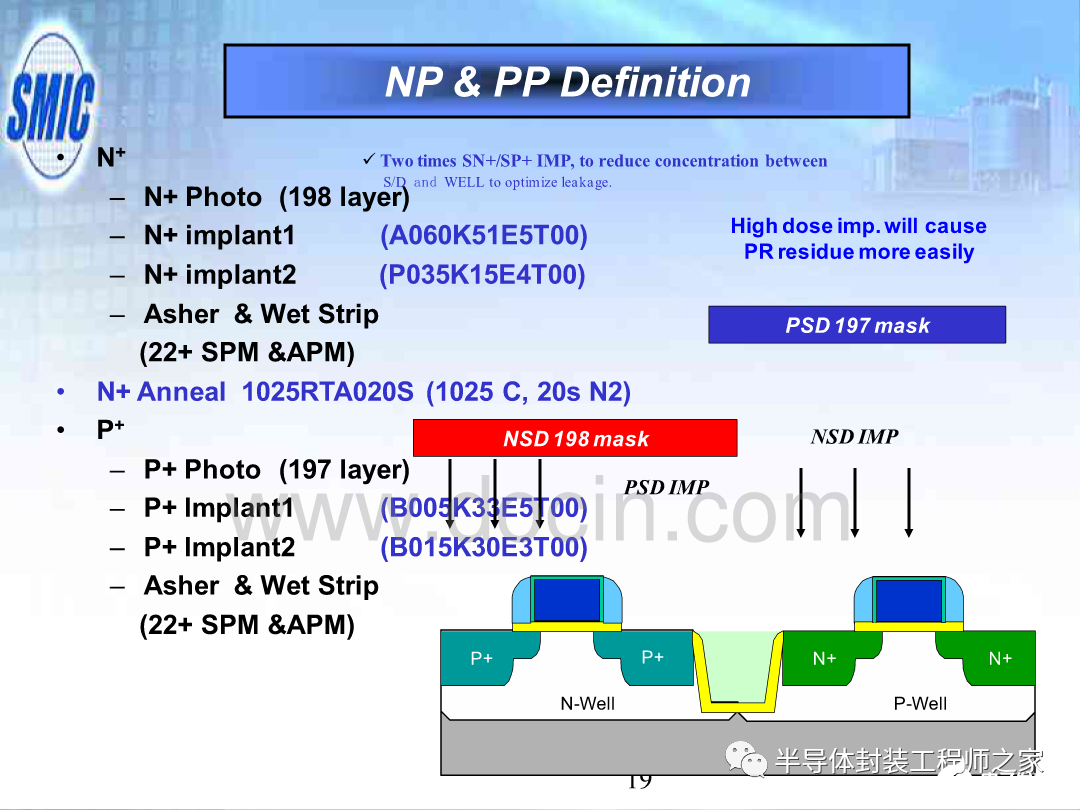

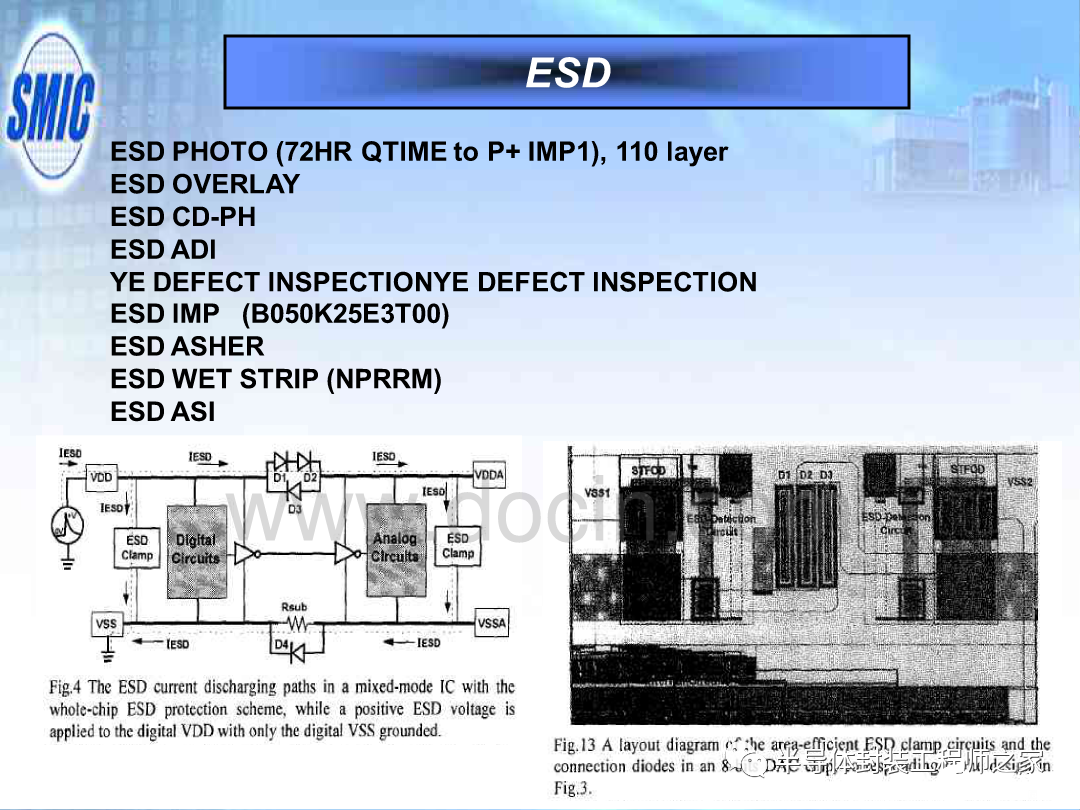

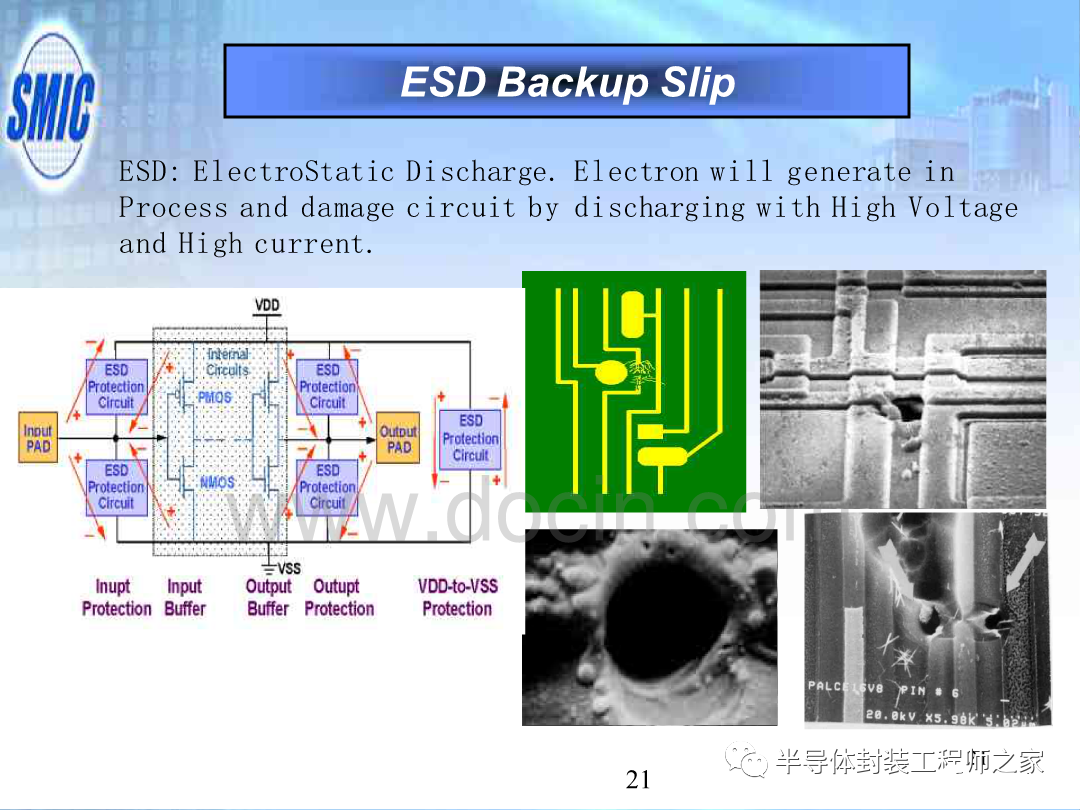

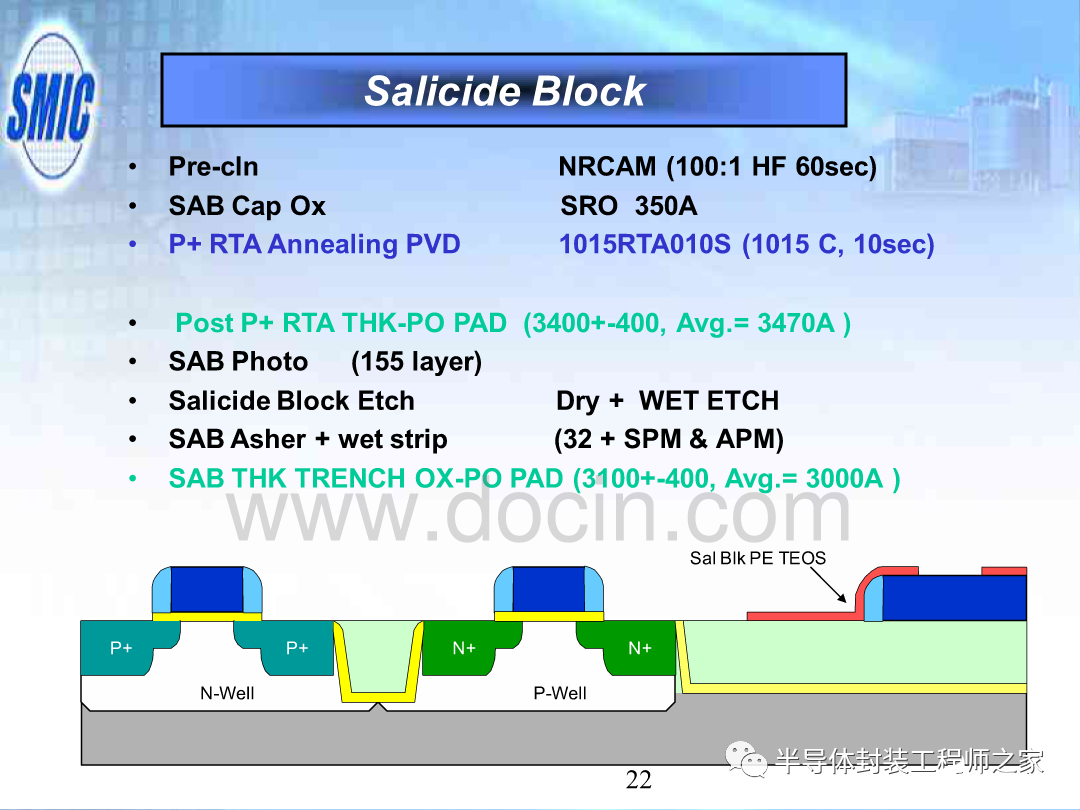

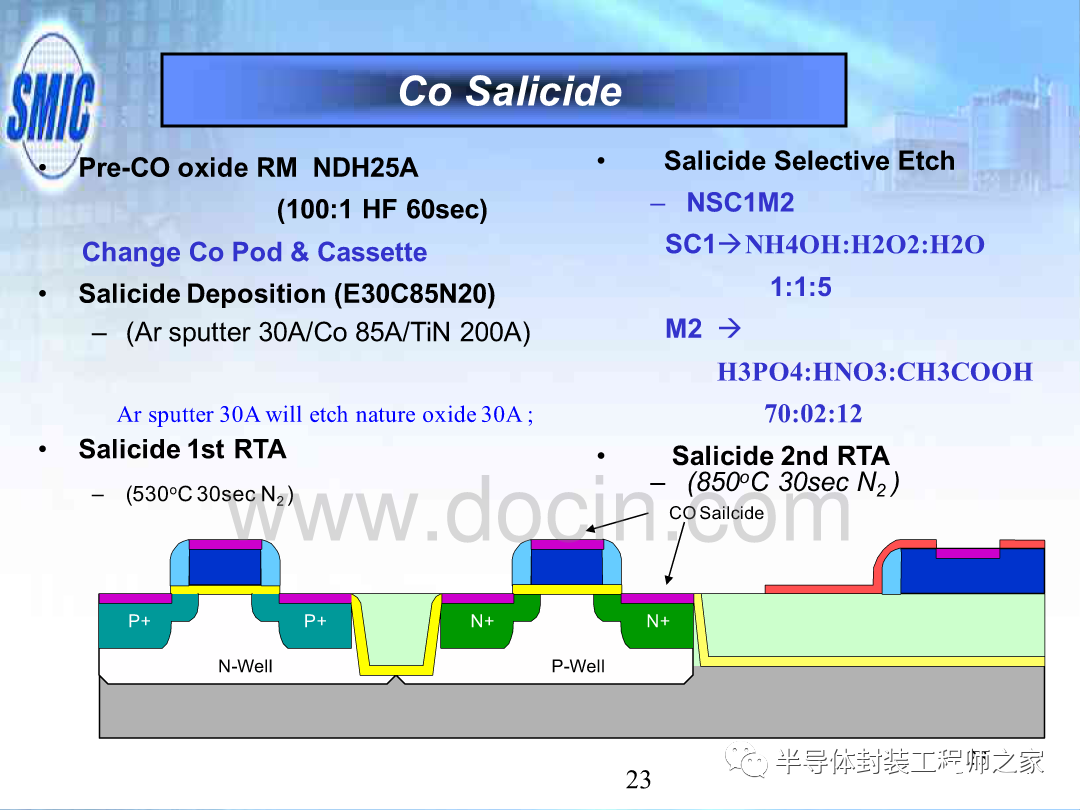

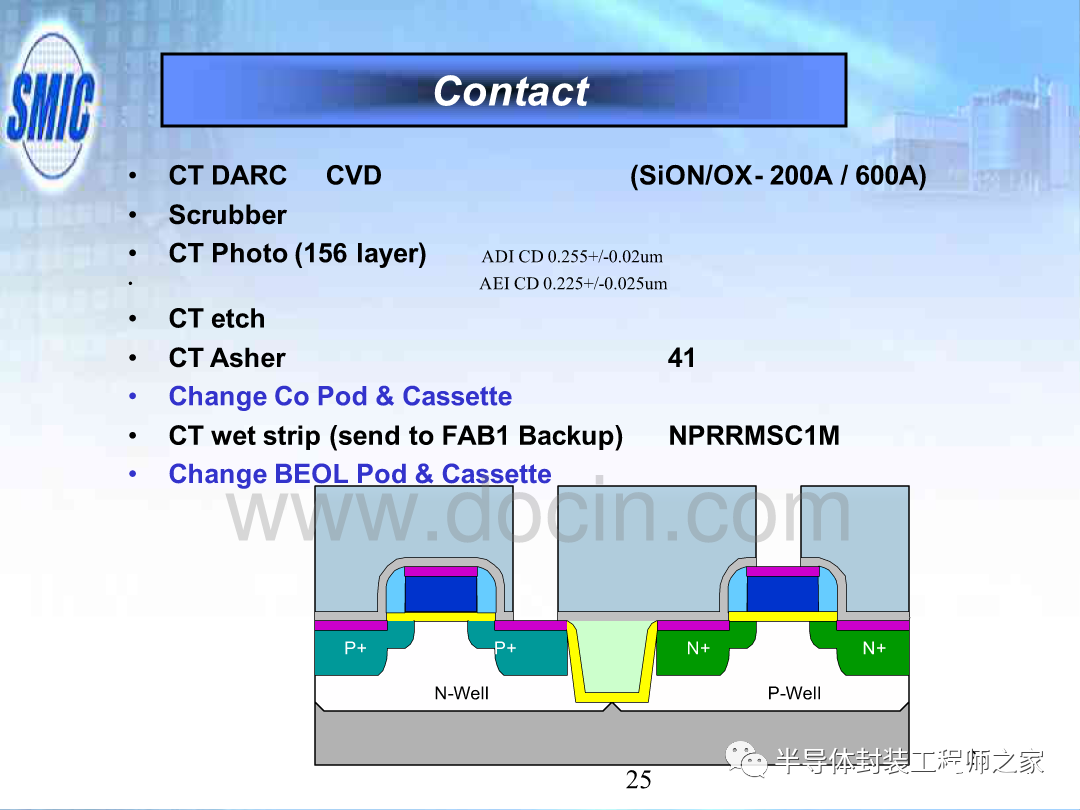

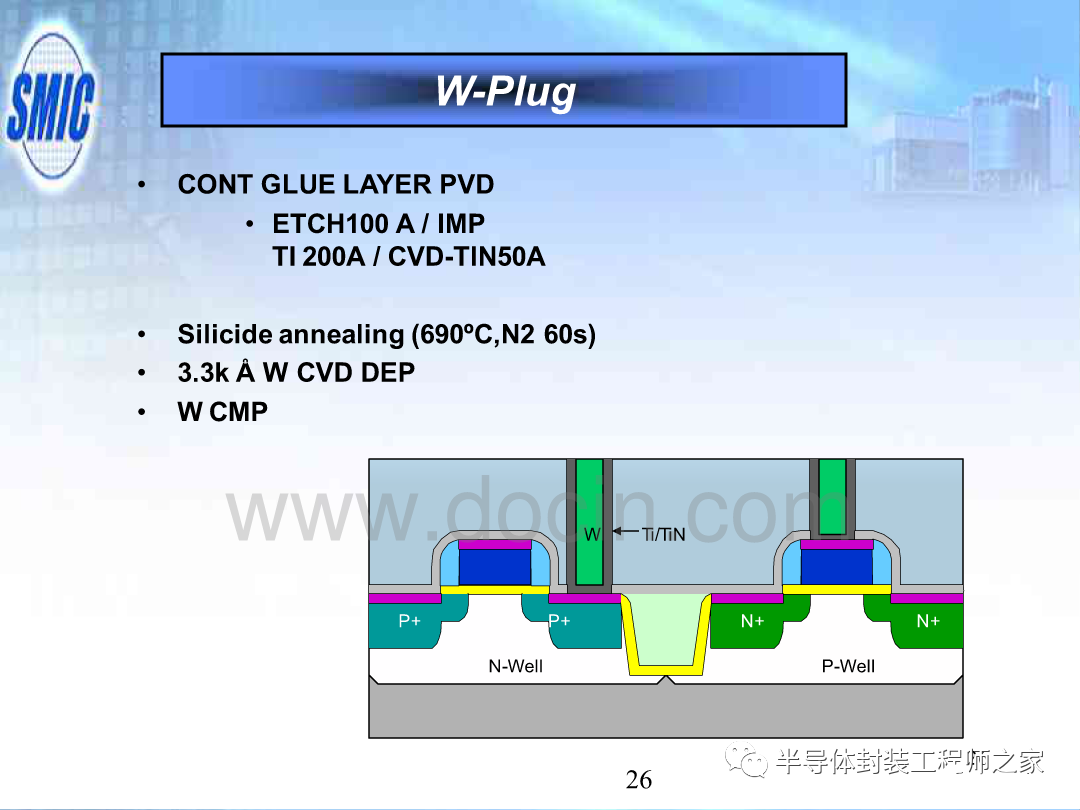

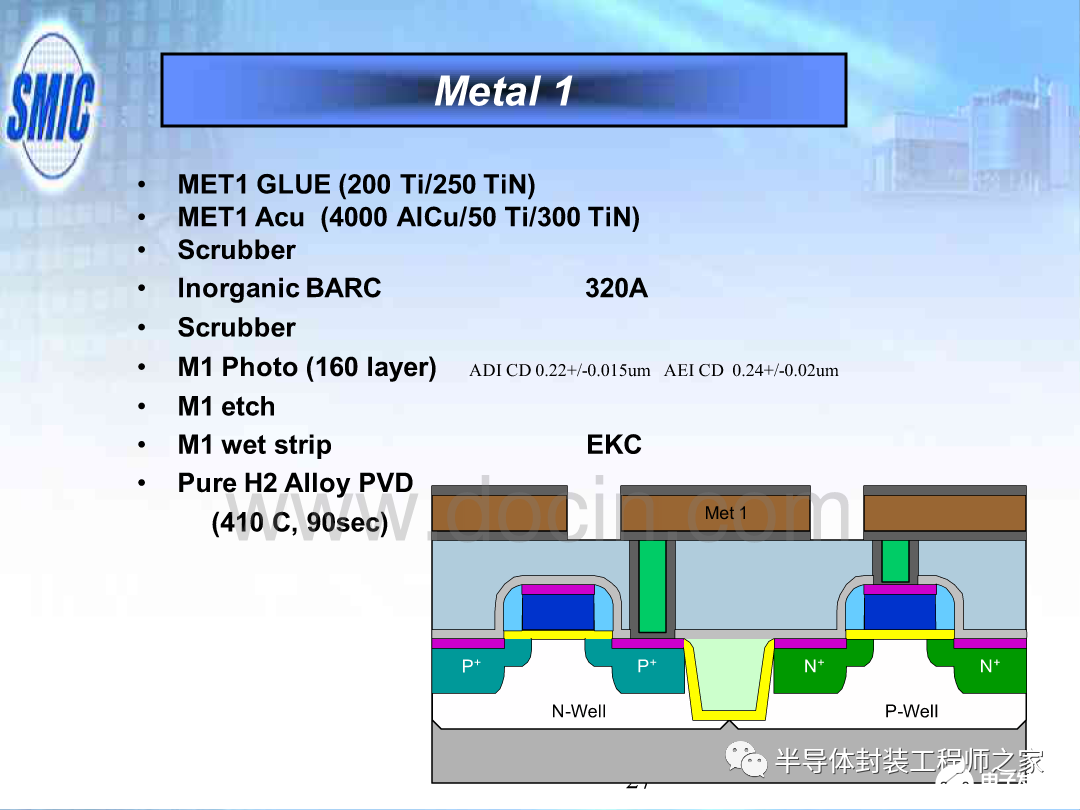

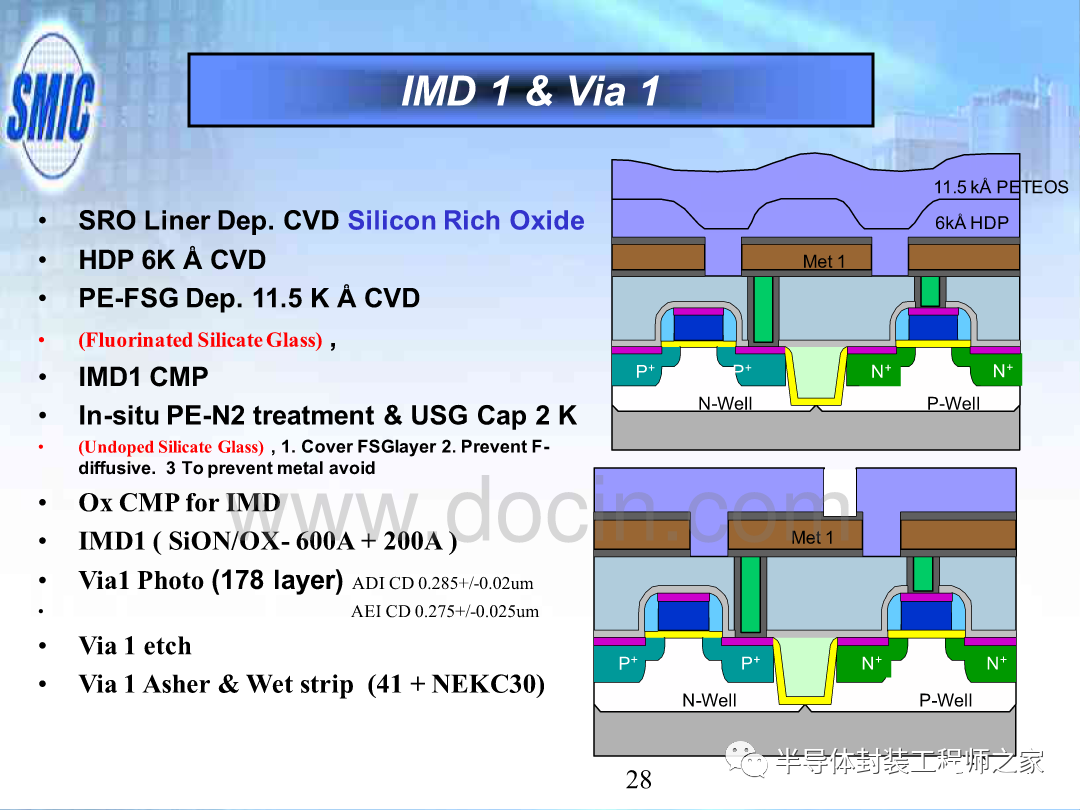

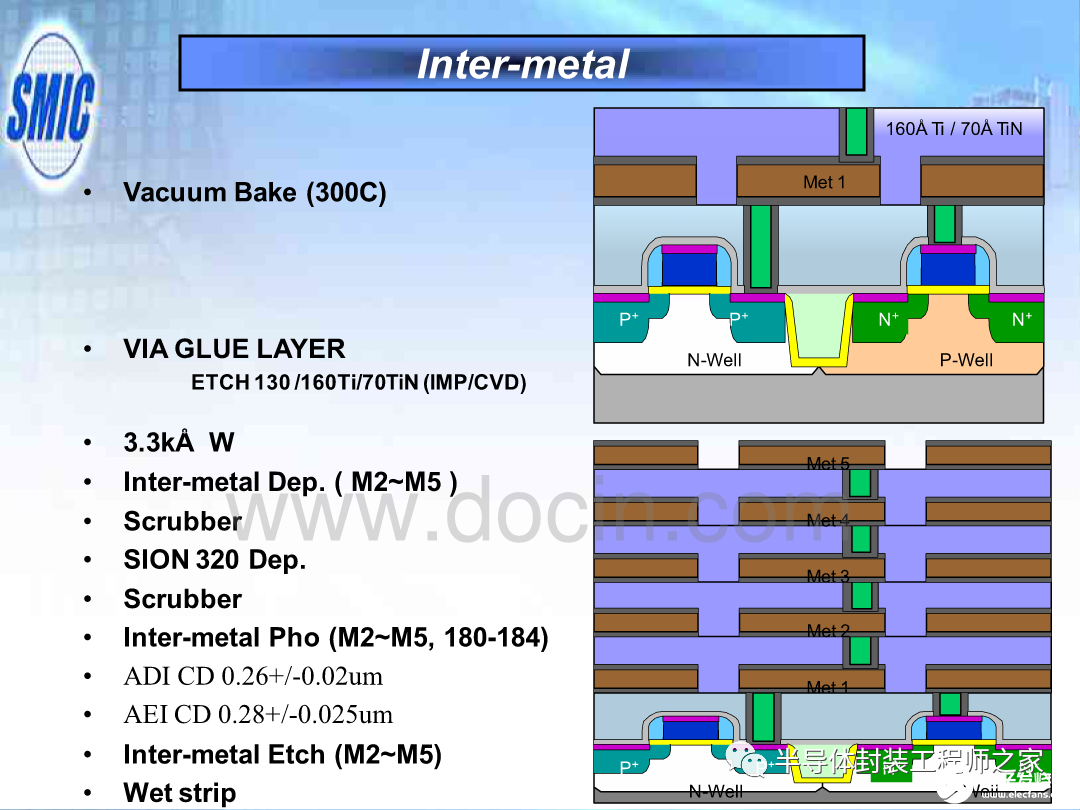

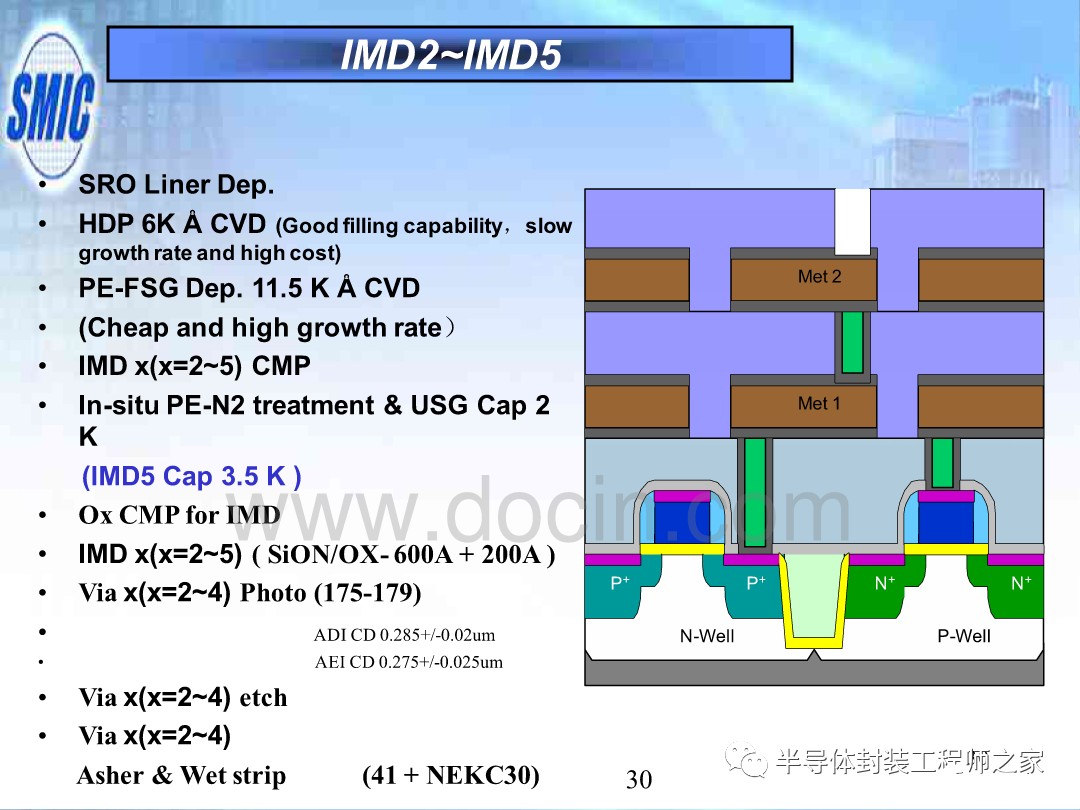

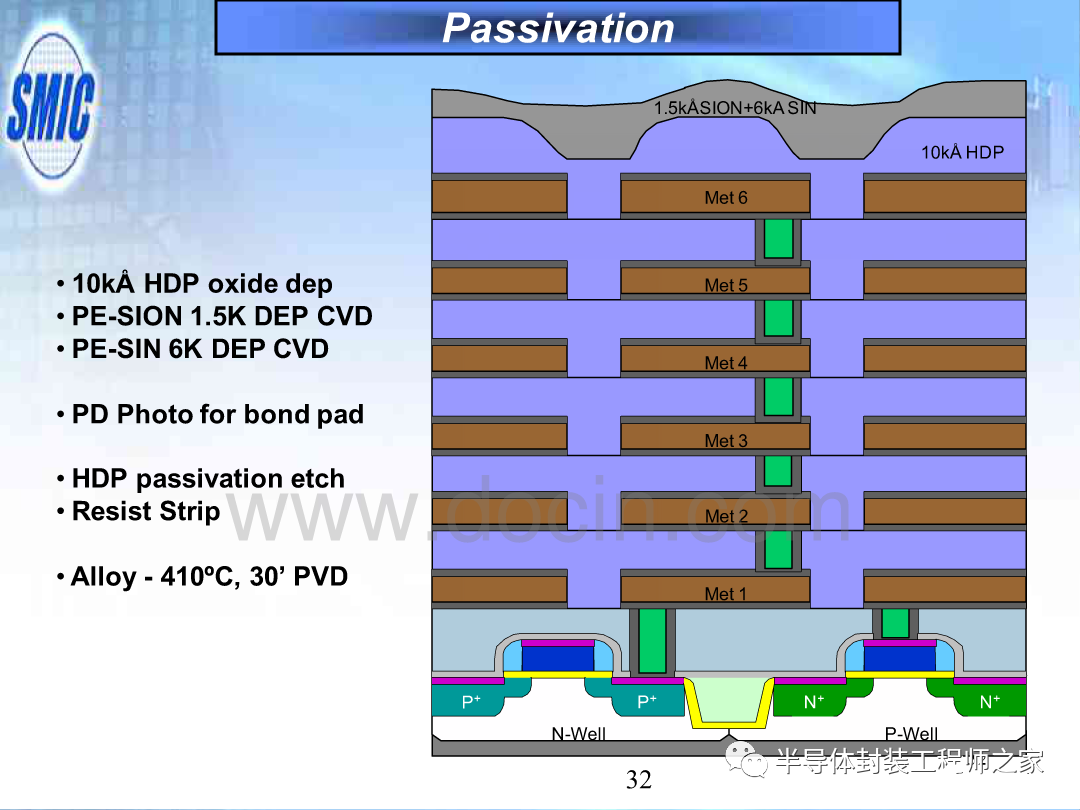

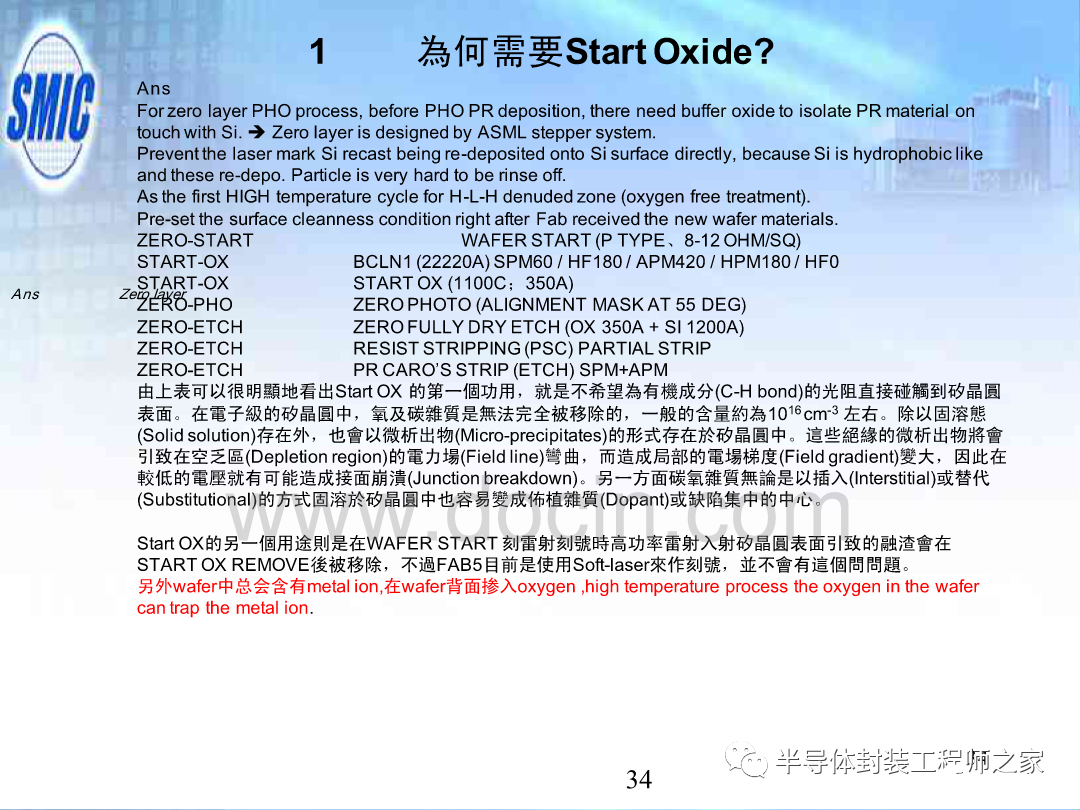

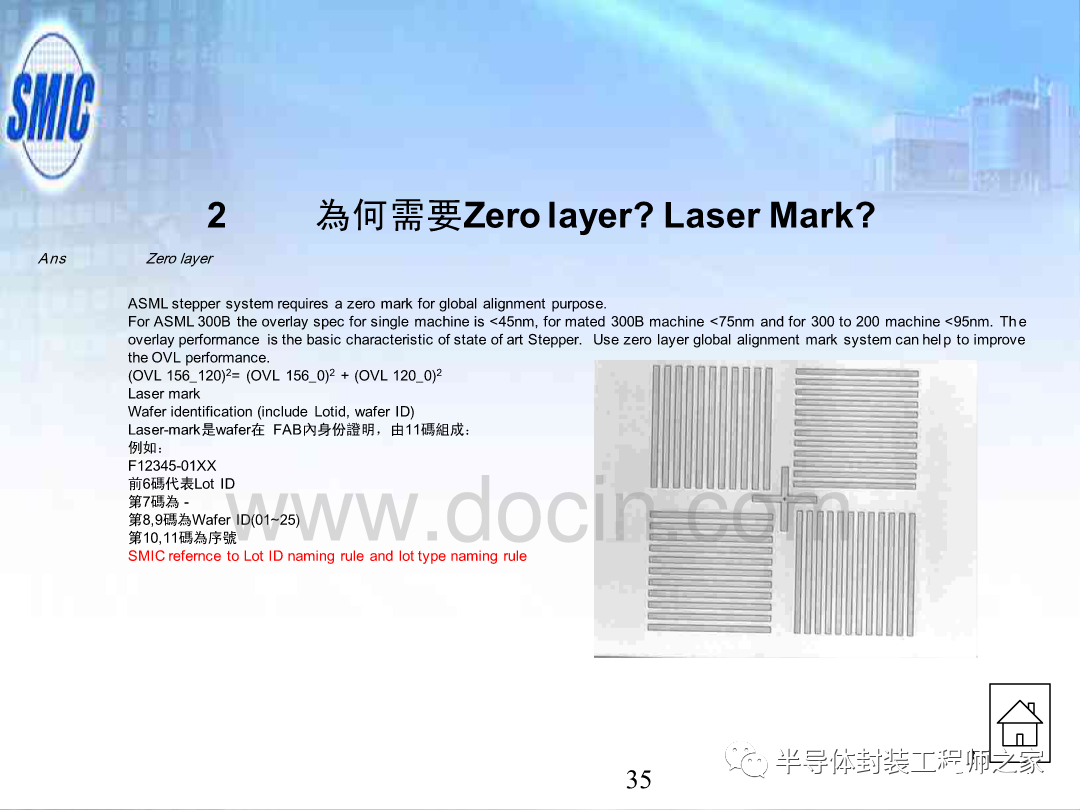

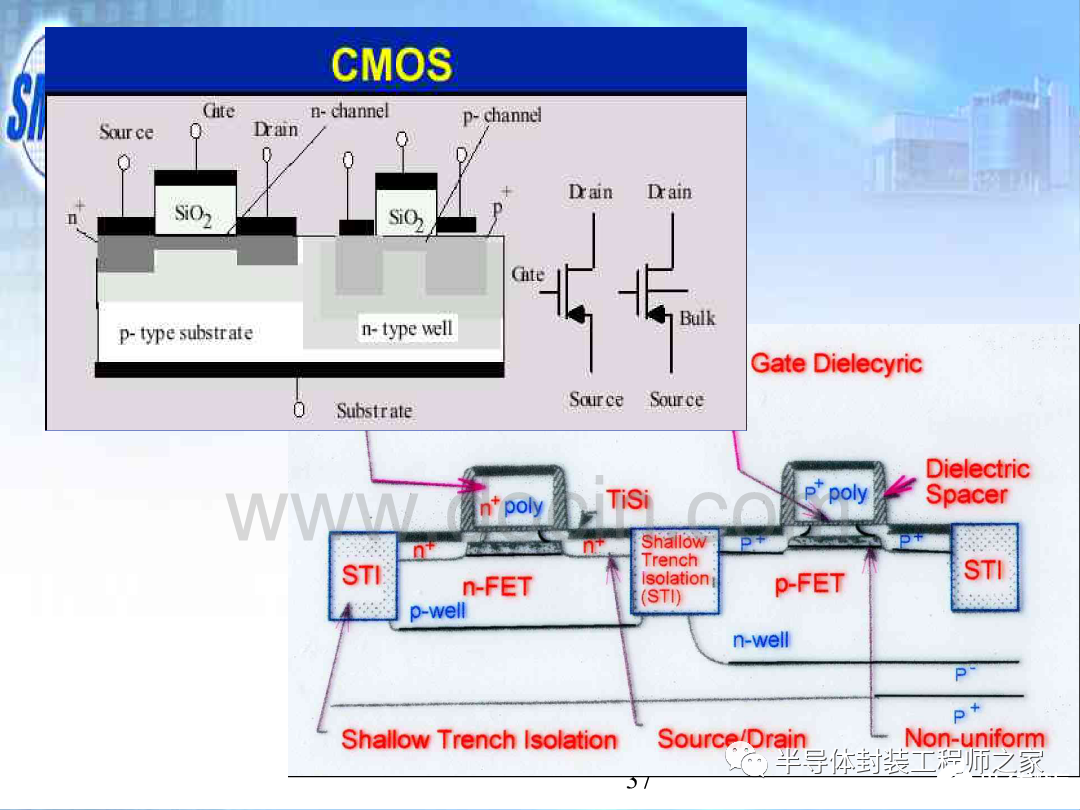

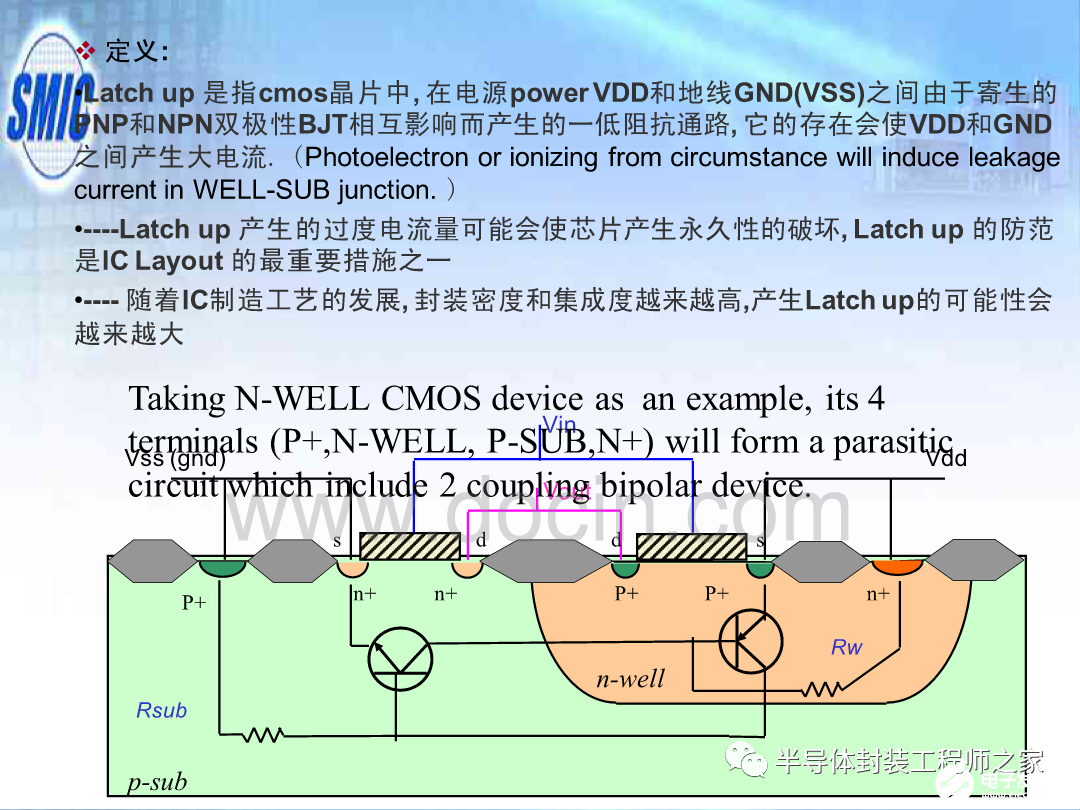

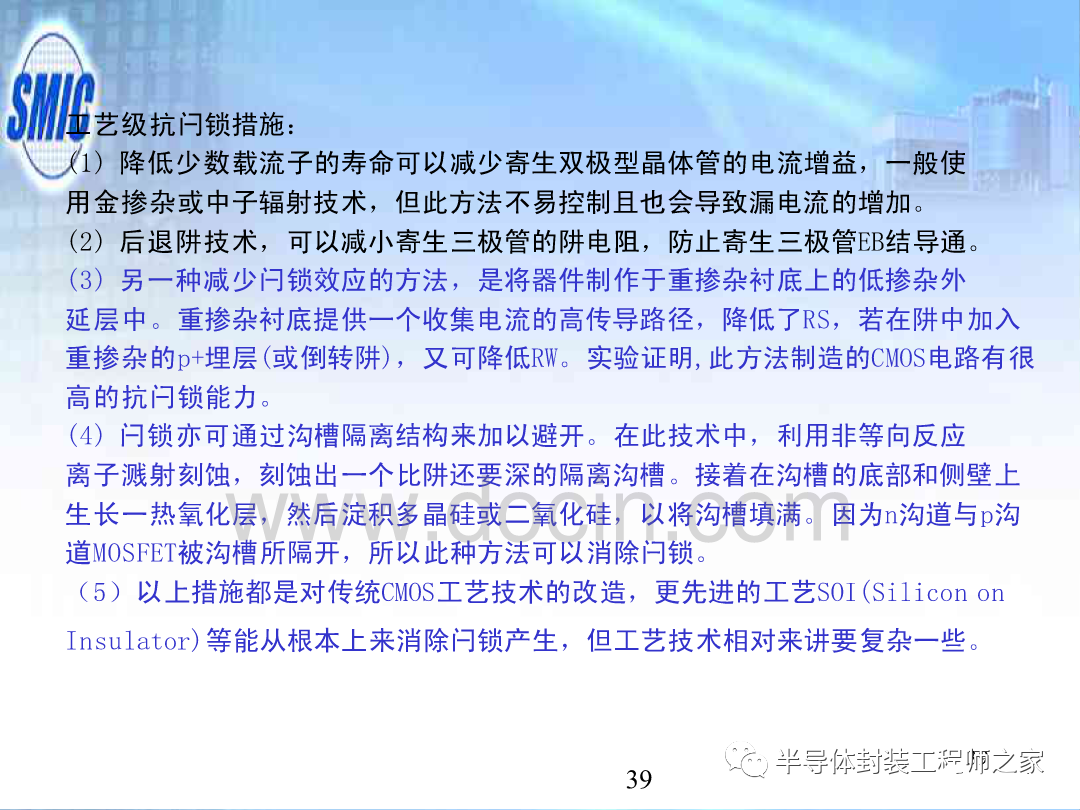

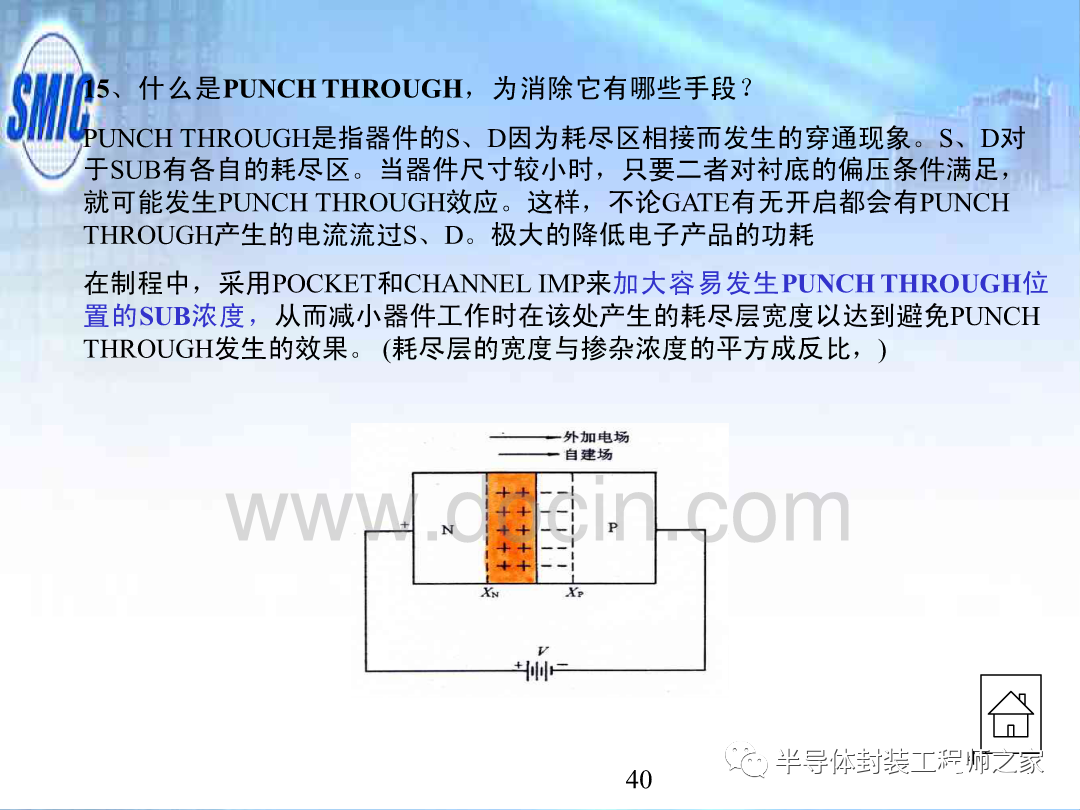

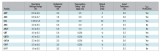

180纳米逻辑芯片制造流程演示幻灯片

180纳米逻辑芯片制造流程演示幻灯片

评论