使用橡皮擦清洁PCB板会不会导致ESD的产生?

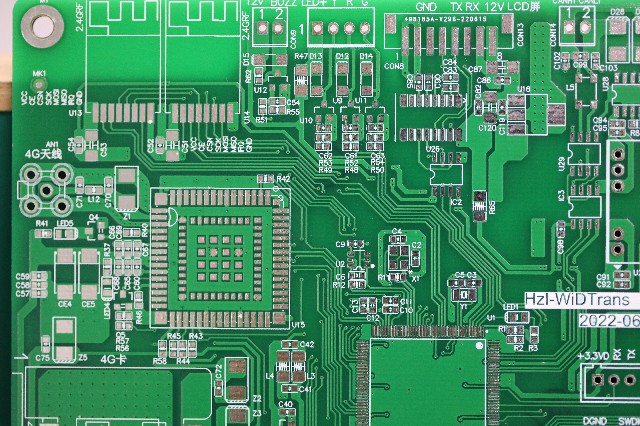

使用橡皮擦清洁PCB板是否会导致ESD(静电放电)的产生是一个备受关注的问题。静电放电可能会对电子设备和其内部电路造成损坏,并且对于依赖于高度准确电信号传输的设备来说,这可能会导致严重的问题。 在本文中,我们将探讨使用橡皮擦清洁PCB板是否会引起ESD的产生,以及如何进行正确的清洁来最大程度地减少ESD的风险。

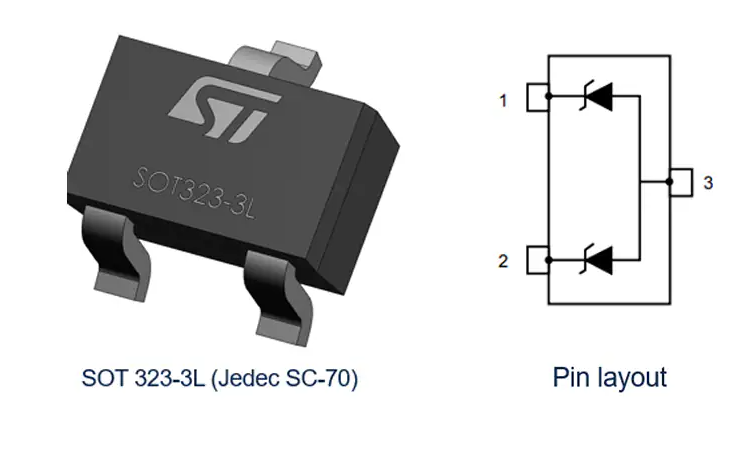

首先,让我们了解一下静电放电(ESD)是什么。静电放电是一种电荷在电介质中快速释放的现象,通常由于电荷的不平衡或电流的突然中断而导致。这种现象会在干燥环境下更为常见,因为干燥的空气会导致静电的积累。当静电放电发生时,会产生高能量的电磁波,并可能会对电路中的晶体管、集成电路和其他电子元件造成损害。

橡皮擦通常被认为是一种能够有效去除 PCB 板表面污垢的工具。然而,橡皮擦是一种致力于帮助去除污渍的材料,这增加了ESD风险因为它会带来静电。事实上,许多橡皮擦表面都具有导电性,这可能会导致静电的积累并在使用过程中造成放电。

清洁 PCB 板时产生的ESD的风险主要是由于两个因素引起的:橡皮擦的材料及其使用产生的运动摩擦。即使使用不导电的橡皮擦,当我们在清洁过程中产生摩擦时,也会产生静电。这是因为橡皮与 PCB 板之间的摩擦会产生电子的移动,从而导致电子结构的紊乱。这种紊乱可以导致静电的积累,并且在某个时刻释放出来。

要减少橡皮擦清洁 PCB 板时ESD的产生风险,我们可以采取一些预防措施。首先,可以选择使用抗静电橡皮擦。这些橡皮擦通常带有抗静电涂层,可以有效地减少静电的积累。其次,我们可以尝试使用导电擦拭材料,例如特殊的擦拭布或纤维材料。这些材料可以在摩擦运动中更好地导电,从而减少ESD的风险。

此外,还可以采取其他预防措施来控制ESD的发生。首先,我们可以确保在清洁过程中尽量保持相对湿度的稳定。较高的湿度可以有效地减少静电的产生,并且减弱已经生成的静电的能量。其次,可以在清洁前接地,以消散可能的静电。

另外,可以使用ESD抗静电工具和设备来处理 PCB 板。这些工具和设备包括抗静电手套、工作台和地板。它们的目的是有效地控制和消散静电,在 PCB 板周围创造一个静电安全的环境。

简而言之,使用橡皮擦清洁PCB板有可能会增加ESD的产生风险。橡皮擦的材料和使用中的运动摩擦都可能导致静电的积累。为了最大程度地减少ESD的风险,我们可以选择抗静电橡皮擦或其他导电擦拭材料,并采取其他的预防措施来控制ESD的产生。总之,正确的清洁方法和措施可以帮助我们在清洁PCB板的过程中最大程度地减少ESD的风险。

-

ESD

+关注

关注

50文章

2424浏览量

180413 -

PCB板

+关注

关注

27文章

1503浏览量

55540 -

静电放电

+关注

关注

4文章

312浏览量

46085

发布评论请先 登录

PCBA加工中产生不良的原因有哪些?

风华功率电感出现异响,可能是哪些原因导致的?

含酒精擦镜纸会损伤镜头镀膜吗

SAW 滤波器 PCB Layout 与 ESD 小技巧总结

ESDA5WY车规级单向ESD保护器件技术解析与应用指南

浪涌多次作用后,TVS参数会不会漂移?

三防漆与散热的关系:涂层会不会影响设备散热?

高速AC耦合电容挨得很近,PCB串扰会不会很大……

PCB 裸板烘干除潮要求及形变(平面度)如何控制?

PCB分板应力测试方法和步骤

如何布线才能降低MDDESD风险?PCB布局的抗干扰设计技巧

使用橡皮擦清洁PCB板会不会导致ESD的产生?

使用橡皮擦清洁PCB板会不会导致ESD的产生?

评论