IC的片内和片间非均匀性是什么?有什么作用呢?

IC的片内和片间非均匀性是指在IC设计和制造的过程中,芯片内部或芯片之间出现的性能或结构的不均匀分布现象。这种非均匀性可以在多个层面上存在,例如晶体管尺寸的变化、材料特性的差异、电阻和电容的变异等。

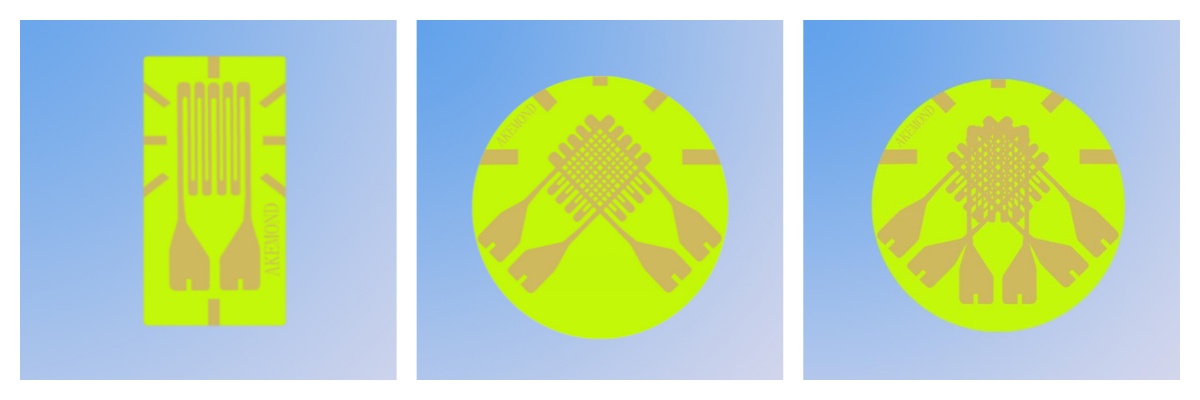

片内非均匀性主要指芯片本身的不均匀分布。在集成电路中,晶体管是起到放大、开关和放电等功能的关键元件。然而,在芯片制造的过程中,晶体管的尺寸可能会被加工误差、光刻过程的影响或制造设备的变化等因素所影响,导致晶体管之间的尺寸不一致。这种不一致会导致晶体管的电流特性、功耗和速度等性能参数存在差异,在严重情况下,可能导致芯片无法正常工作。因此,对于要求高精度和高可靠性的应用,如高性能处理器或图形芯片,需要更加精确的尺寸控制来减小片内非均匀性。

片间非均匀性则是指在集成电路制造的过程中,不同芯片之间出现的非均匀性。在大规模集成电路中,由于制造过程中光刻、化学腐蚀等工艺的限制,导致不同芯片之间的几何尺寸和电学特性存在差异。例如,当芯片之间存在电阻和电容的不一致时,将导致信号传输的失真和延迟,进而影响整个电路的性能。此外,不同芯片之间的物理尺寸变化也可能导致一些制造和封装的误差,例如封装引脚的对位问题,这也会对整个芯片的功能和性能产生不利影响。

非均匀性在集成电路设计和制造过程中起着重要作用。首先,片内非均匀性和片间非均匀性的存在影响了芯片的性能和可靠性。例如,不同的晶体管尺寸和材料特性可能会导致不同的电流驱动能力和速度,进而影响芯片的工作频率和功耗。而片间非均匀性则可能导致信号传输的延迟和失真,进而限制了芯片的工作速度和可靠性。

其次,非均匀性对芯片的测试和可测试性也有一定的影响。在芯片测试过程中,需要对芯片内部的功能单元进行测试,以确保其正常工作。然而,如果芯片内部存在片内非均匀性,不同功能单元之间的性能差异可能导致测试结果的不准确或不一致。同样地,如果芯片之间存在片间非均匀性,可能需要更复杂的测试方案和策略来保证整个IC的质量。

最后,非均匀性也会对集成电路工艺和制造过程的控制产生挑战。在电路设计中,需要考虑到片内非均匀性和片间非均匀性对电路性能和功能的影响,并且采取相应的措施来弥补或校准这些非均匀性。在制造过程中,需要通过优化工艺参数和加强监测控制来减小非均匀性的影响。

综上所述,芯片的片内和片间非均匀性在IC设计和制造过程中起着重要的作用。了解和解决这些非均匀性是确保高性能、高可靠性和高质量的集成电路的关键步骤。通过采用精确的尺寸控制、工艺优化以及测试策略的改进,可以减小非均匀性带来的负面影响,提高芯片的性能和可靠性。

-

集成电路

+关注

关注

5465文章

12695浏览量

375847 -

IC设计

+关注

关注

38文章

1406浏览量

108438 -

晶体管

+关注

关注

78文章

10443浏览量

148696

发布评论请先 登录

FRED应用:波片模拟

[VirtualLab] 光波导系统的均匀性探测器

基于4片DSP6678+FPGA KU115 的VPX高速信号处理平台

Cw32l010 SPI软件片选有多余脉冲怎么解决?

PI加热片知识FAQ

【新启航】碳化硅外延片 TTV 厚度与生长工艺参数的关联性研究

IC的片内和片间非均匀性是什么?有什么作用呢?

IC的片内和片间非均匀性是什么?有什么作用呢?

评论