时钟对芯片功能准确性、性能高低和功耗高低有着至关重要的影响。芯片的时钟来源一般有三种:

第一,通过外部引脚直接输入时钟信号,常用于接口芯片、传感器芯片,SOC系统中少见;

第三,内部时钟发生器+内部PLL +内部分频器产生时钟,常见于对安全、功耗有特殊要求的芯片;

第四,外部晶振+内部时钟震荡器+内部PLL +内部分频器产生时钟,性能高一点的MCU基本都采用这种方案。

以第四时钟方案为例,其采用外部晶振是因为外部晶振精度高,采用内部时钟振荡器是利用其安全、灵活、低功耗的优势,配置PLL可将外部晶振和内部振荡器的时钟倍频,再通过分频器分频供给到各个模块。且为了节省功耗该SOC系统往往工作频率可变,性能要求高时使用高频率、任务简单时使用低频率,不工作的时候可关掉时钟。这就是广泛应用的多时钟模式系统,实现该系统需要采用时钟切换、clock gating甚至power gating技术。

本文首先探讨时钟切换的实现,对于clock gating和power gating问题后续探讨。

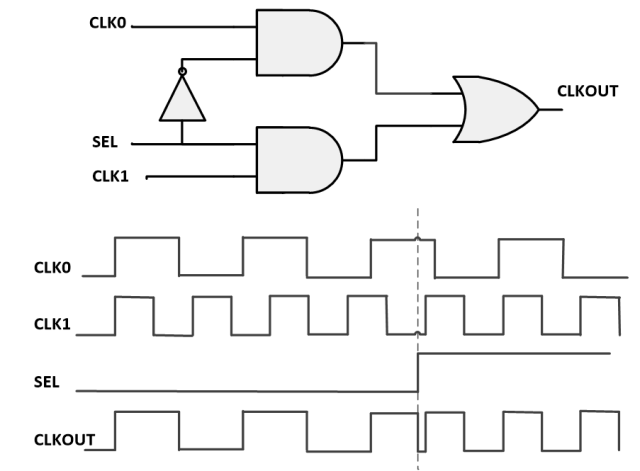

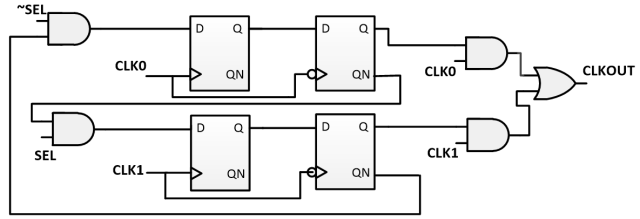

图1

首先讨论两个时钟间的切换问题,这两个时钟可能是具有倍频关系的同步时钟,也能是不相关的异步时钟。很容易想到采用二选一选择器就可以实现这一功能,不幸的是无论这两个时钟关系如何,都可能在时钟线上引入毛刺,如图1所示。

二选一选择器采用与或门的形式实现,SEL是选择信号,选择CLK0或CLK1到输出端口CLKOUT,也就是说CLKOUT是CLK0和CLK1拼接的结果。

图1中,SEL信号由低到高变化,CLK0为高电平、CLK1为低电平,此时CLKOUT就会出现向下的毛刺;如果此时CLK0的频率高于CLK1,那么CLKOUT的毛刺就是向上的脉冲。既然毛刺的出现是选择信号SEL变化时,两个输入时钟CLK0和CLK1高低交错,高低电平拼接造成的。

那么,如果让选择信号在两个时钟的下降沿处分别将时钟截断,再拼接成输出时钟,是不是就可以避免毛刺出现了呢?为此,我们在选择路径中插入下降沿触发器对SELECT信号进行下降沿采样,如图2(a)所示。

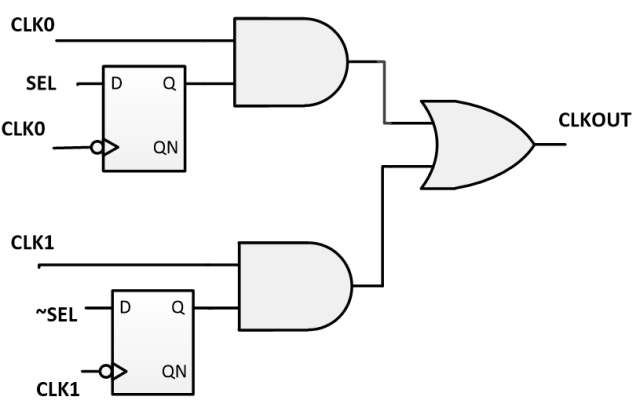

图 2(a)

图 2(b)

但这样仍存在问题,存在着CLK0没有被SELECT关断,CLK1已经开始输出的情况,这仍有可能产生输出毛刺,如图2(b)所示。

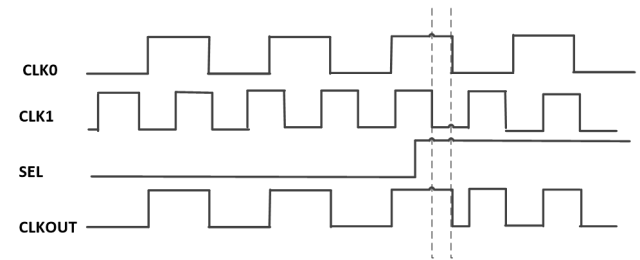

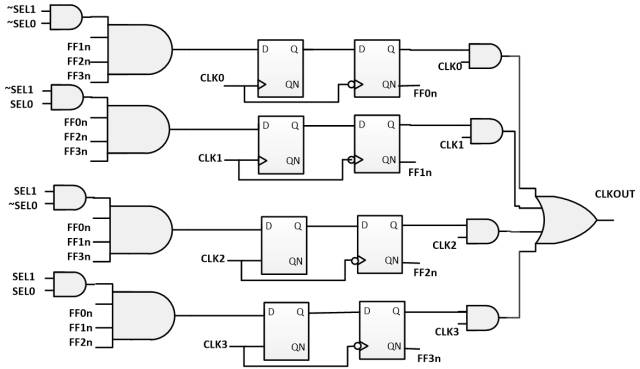

为了保证一个时钟选择信号关断后另一个时钟再输出,再在触发器前插入与门,连接成交叉反馈结构,如图3(a)所示,这就是经典的时钟转换电路。但这还是不够,如果CLK1和CLK0是异步的,那还需要对其进行同步,采用传统同步方式,插入上升沿触发器即可,如图3(b)所示。

图 3(a)

图 3(b)

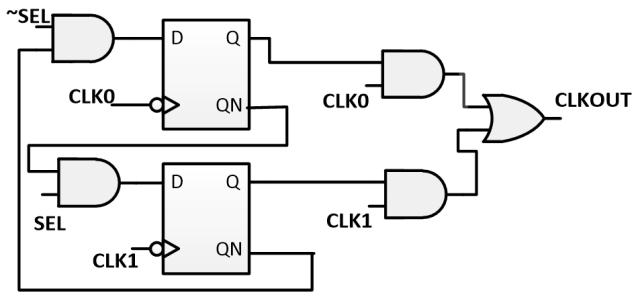

到这里我们已经掌握了实现两个时钟切换的电路设计的基本思路,那如果有三个甚至更多时钟相切换又该怎么办?沿袭以上设计思路,将该电路结构进行扩展,每一路双锁存输出都相互交叉反馈即可,图4以四个时钟切换为例,给出了电路结构图。

图 4

以上就完成了时钟切换基础设计,总结一下大家需要知道,多时钟系统已经广泛应用,在进行时钟转换设计时, 1、单纯采用MUX对时钟做选择是不行的; 2、图3所示的时钟切换电路能够以较小的消耗而消除时钟切换时的毛刺; 3、该时钟切换电路结构可扩展,可按照这样的设计思路设计多选一时钟切换电路; 4、如果是异步时钟还要插入双锁存结构消除亚稳态。

审核编辑:刘清

-

分频器

+关注

关注

43文章

536浏览量

52259 -

时钟发生器

+关注

关注

1文章

268浏览量

69885 -

时钟芯片

+关注

关注

2文章

283浏览量

41905

原文标题:你不可不知的——时钟切换电路

文章出处:【微信号:芯司机,微信公众号:芯司机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电能质量在线监测装置的备用链路切换需要手动干预吗?

电能质量在线监测装置自诊断功能的硬件层实时监测的冗余切换是如何实现的?

HT 流畅过渡动画 × 场景切换实现方案

瑞萨RA系列FSP库开发实战指南(29)CGC(时钟生成电路)时钟控制

ACS1000中压变频器是如何实现同步切换控制的?

电容在时钟电路中的应用有哪些

时钟电路的组成与设计要点介绍

时钟电路与晶振电路两者的区别有哪些

HMC7044外参考时钟切换失败的原因?

AN-1420:利用数字锁相环(DPLL)实现相位增建和无中断切换

探讨模拟电路为什么需要隔离电源

探讨时钟切换电路的实现

探讨时钟切换电路的实现

评论