对于信号而言,phase shift是一个相对值,而time delay是绝对值。有时候我们关心time delay,那么如何由phase得到延迟时间呢?

假设信号经过一阶低通滤波器(-3dB带宽为f0),那在所有频率点,信号的delay是怎样的?

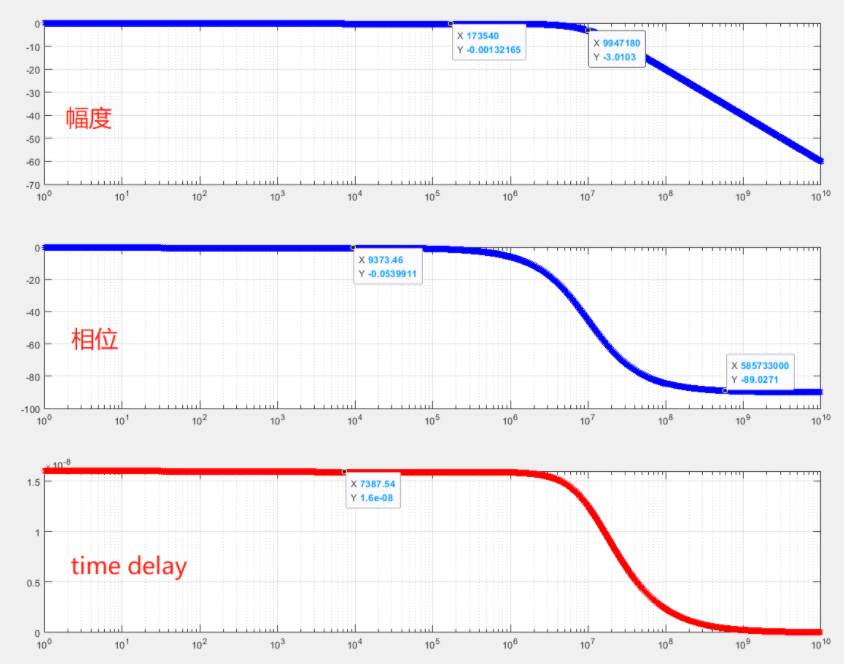

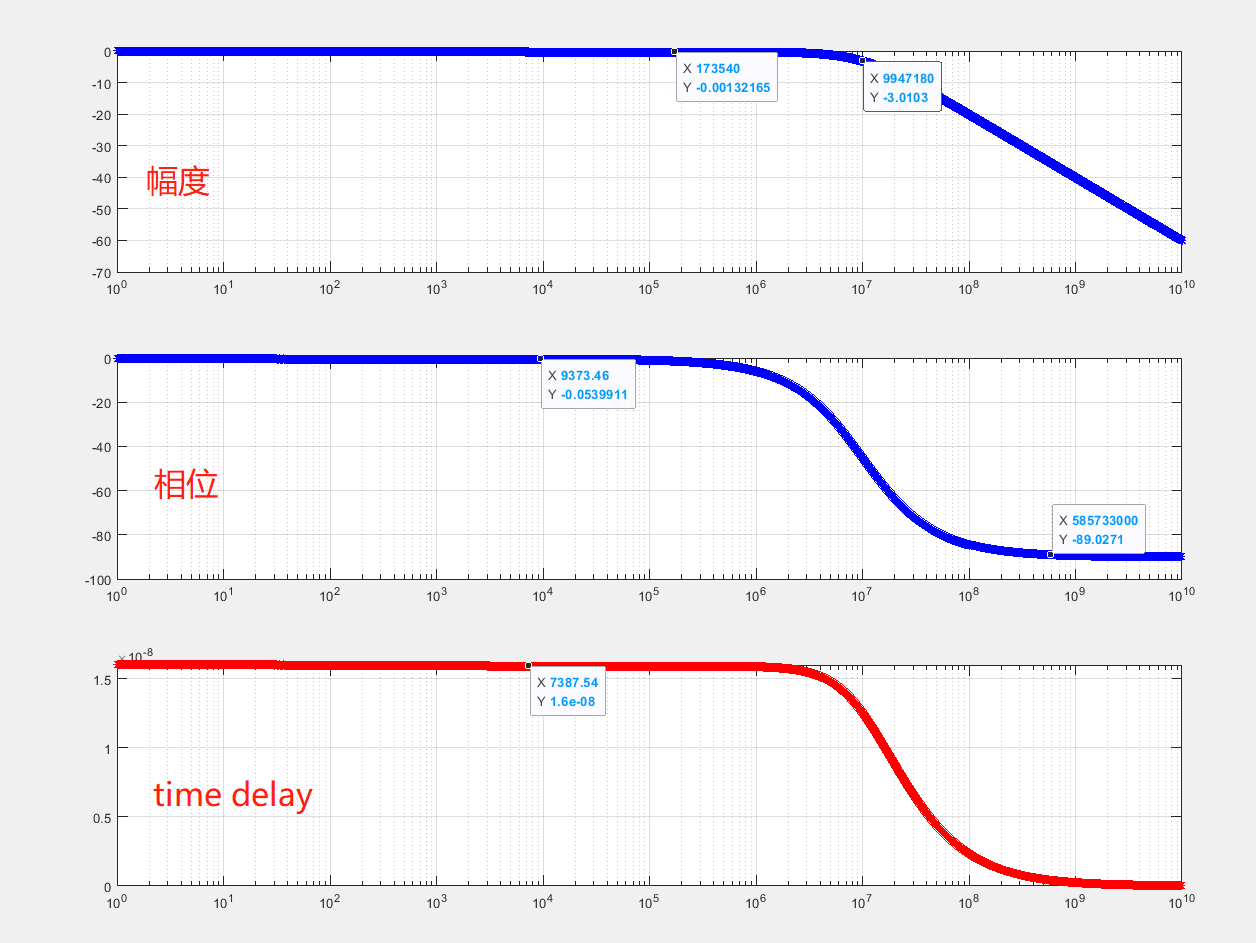

tao=16ns时,我用matlab plot了一下幅度、相位和time delay,其中time delay=phase/w (其中w为角频率,phase量纲为rad/s)

可以看出低频的time delay=tao,高频信号没有delay。

在数学上time delay=arctan(f/f0)/(2*pi*f)

当f/f0为无穷小时,上式近似为1/(2*pi*f0)=tao ==》原来tao的物理意义在这里,意味着小于f0的频率基本都delay tao。

当f远大于f0时,time delay=0,可以理解为相位偏差90度但由于周期无穷小,所以delay为0;

中间阶段就按照arctan(f/f0)/(2*pi*f)的公式来,time delay和频率是一个非线性的关系。

**************************************************************

我因此继续延伸一个话题:一个闭环运放,当gbw不变,而phase margion变化时,在gbw处的环内信号(也可以理解为干扰) delay time一样吗?如果环内信号的delay time特别关键,那么可以认为即使gbw相同,当phase margion不同时,在gbw处的干扰信号的抵消速度不一样。

再进一步,如果是一个dc-dc或pll,带内双极点,一个零点,那么即使gbw不同,在零极点位置相同(dc增益不同)时,环路的响应速度(高频处的相位)是一样的(但抵消的幅度不一样,这么分析好像实际意义不大,但把环路反馈拆分为速度(时间)和幅度,有利于更细致的分析环路响应问题和做改进)。

再往前,环路问题拆分为幅度和速度(时间,也可以认为是频率)后,在sdm adc中,如果要优化int1对idac的瞬态响应,由于idac方波中包含了各种频率分量,为了使方波中各次谐波都能有响应,此时opamp的gbw要足够大。

而当设计一个滤波器,想要在某个频段有很好的线性度时,可以不用做很高的gbw,而利用一些复极点把关心的频段做一个peak即可。

以上的分析说明,明确对速度(频率)和幅度的要求后,改进方法会很有针对性。

审核编辑:黄飞

-

滤波器

+关注

关注

162文章

8351浏览量

184754 -

低通滤波器

+关注

关注

15文章

528浏览量

48828 -

谐波

+关注

关注

7文章

924浏览量

43817 -

信号

+关注

关注

11文章

2902浏览量

79666

发布评论请先 登录

调用Time_Auto_Decrement()函数来是LED_Delay_Time变量的值递减,为什么值却不变?

pcm1796数据中的delay time和pcm1748数据手册中的group delay是同一个意思吗?

DLP4500如何自动产生graycode和phase shift pattern?

在FPGA内手动做Delay

testbench时钟信号

Design considerations for three-phase power factor correction

Phase Noise Analysis in CMOS L

UCC28950,pdf(Green Phase-Shift

数字控制移相-Digitally Control Phase

数字控制移相-Digitally Control Phase

Propagation Delay Measurements

Accounting for delay from multiple sources in delta-sigma ADCs

浅谈信号delay time和phase shift

浅谈信号delay time和phase shift

评论