最近项目中,FPGA通过多个RGMII接口与其他设备通信,在通信的过程中,有一个RGMII接口对端设备始终无法驱动,最后通过共享一个PHY,时分复用的形式来“解决”该问题

案例背景

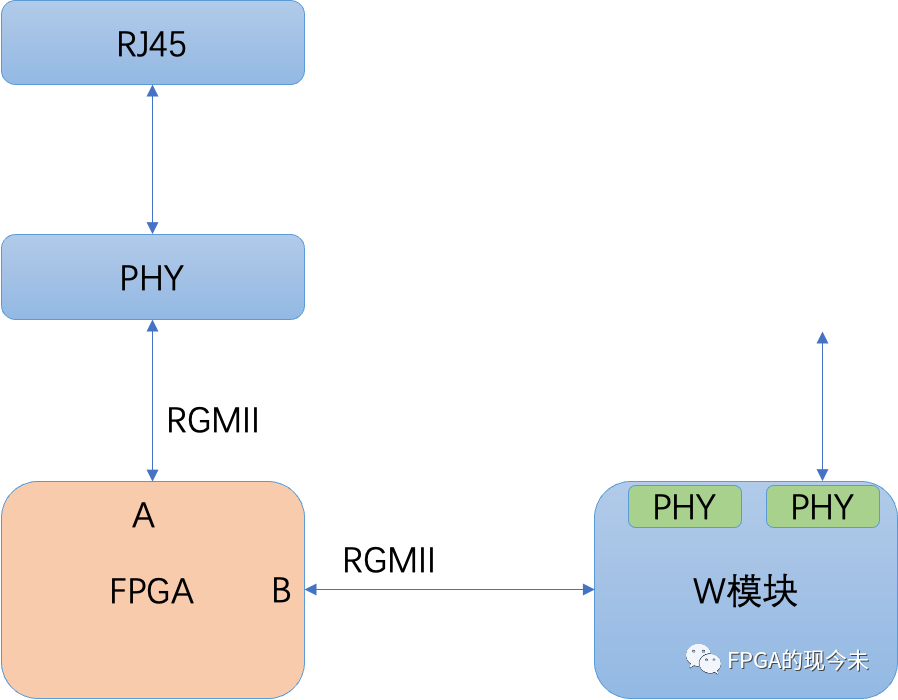

FPGA一共有2个RGMII接口,其中A接口外接一个PHY后通过RJ45连接网线,B接口通过RGMII接口以MAC对MAC的形式直接和W模块相连,如下图所示:

正常的业务场景下,FPGA有可能通过A接口用网线和外部连接的设备通信,也可能直接和W模块通信。

问题

由于W模块的问题,始终无法驱动RGMII接口,后来和供应商,以及W模块上芯片的原厂交流,都无法知道如何驱动该RGMII接口(***任道重远啊),FPGA和W模块的通路彻底断开。

分析及解决措施

(1)由于FPGA和W模块之间的性能需要500Mbps+,所以无法通过飞线产生一个通用IO口来解决该问题;

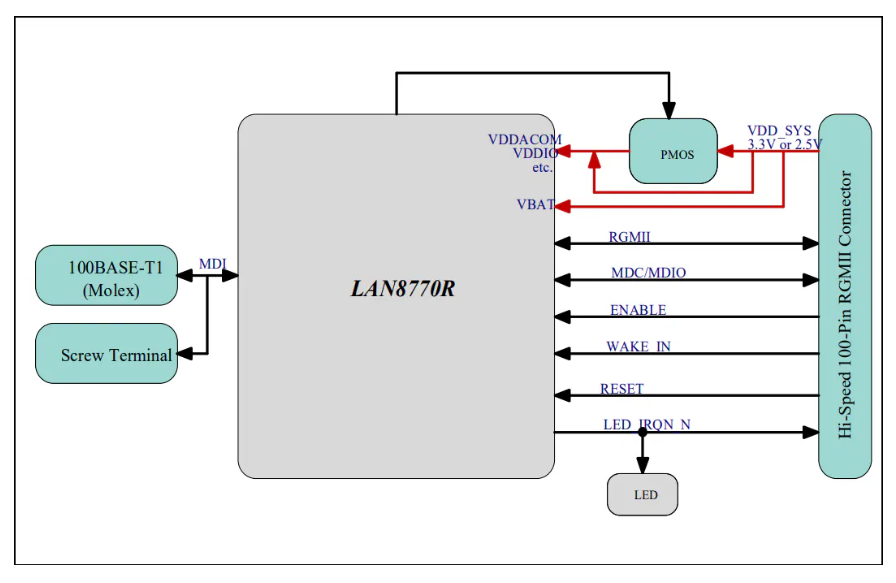

(2)W模块供应商其实也没有对RGMII接口做过充分测试,推荐我们使用的是该模块内置的PHY接口和外界通信;

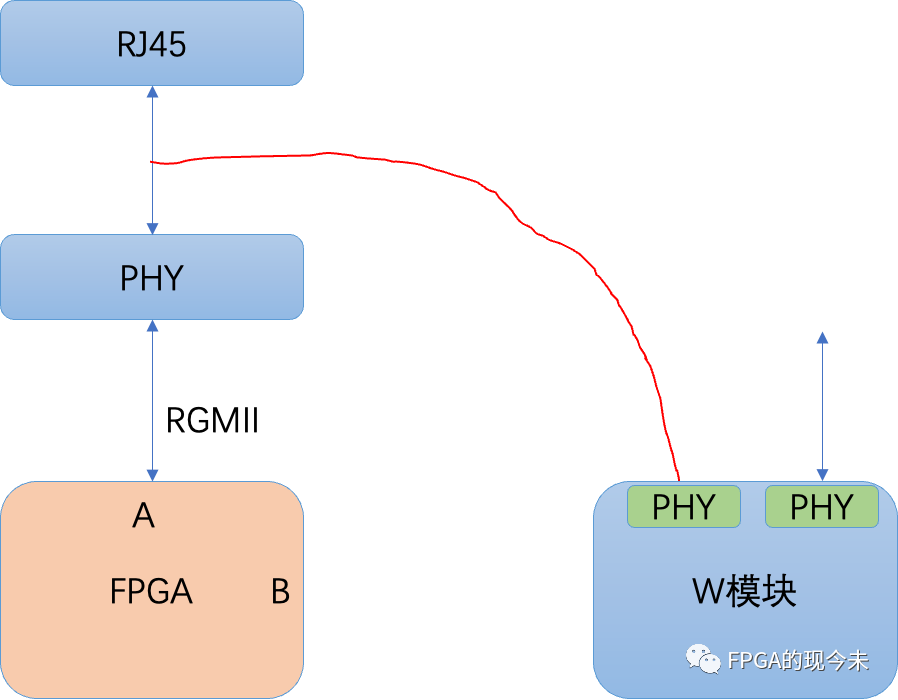

(3)FPGA的AB接口的业务本来可以不同时存在,那是否可以时分复用FPGA外接的PHY了,即FPGA通过PHY和RJ45通信,也可以和W模块通信呢?于是构想了如下的方案:

利用W模块内置的PHY,通过飞线的方式,连在PHY和RJ45之间,如图中红色线条所示。当RJ45插上网线时,FPGA和RJ45通信,否则FPGA就和W模块通信。但是这个方案有一个问题,当插上网线的时候,外部设备和W模块都通过FPGA的同一个PHY和FPGA通信,这必要会有冲突,那现在的问题就是这2种模式如何最小代价的切换。

(4)由FPGA控制W模块的上电来切换,当FPGA和RJ45通信的时候,通过配置FPGA寄存器的方式,将W模块下电,当FPGA要和W模块通信的时候,拔掉网线,同时通过配置FPGA寄存器的方式将W模块上电。

测试结果

这种方案行不行,上板测试是最好的检验方法。

(1)将W模块下电,插上网线,外部设备通过网线给FPGA发包,FPGA在内部MAC做环回,通过测试;

(2)将W模块上电,拔掉网线,通过W模块发包,FPGA在内部MAC做环回,通过测试;

(3)将W模块上电,且插上网线,我们通过W模块和外部设备发现,和FPGA的链路不稳定,一会能link up,一会又link down,即有冲突,和我们前期预想的一致。当拔掉网线,或者W模块下电后,对端都能和FPGA正常通信。

总结

当一个PHY同时和2个PHY对接的时候,只要我们做好2个PHY的切换,是可以实现“时分复用”的,但是不到万不得已,还是别这么干吧。

-

FPGA

+关注

关注

1664文章

22503浏览量

639274 -

接口

+关注

关注

33文章

9601浏览量

157628 -

通信

+关注

关注

18文章

6450浏览量

140269 -

PHY

+关注

关注

2文章

341浏览量

54327 -

RGMII

+关注

关注

0文章

31浏览量

12758

发布评论请先 登录

Wi-Fi FEM研发,开启第二个十年

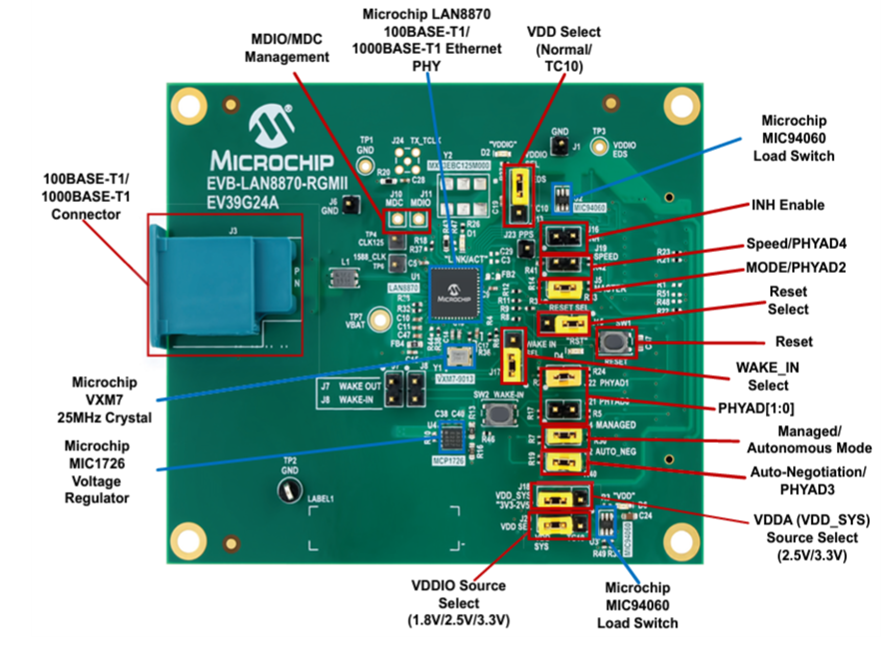

EVB-LAN8770-RGMII评估板技术解析与应用指南

EVB-LAN8870-RGMII评估板技术解析与应用指南

两个模拟SPI,只有第二个正常,为什么?

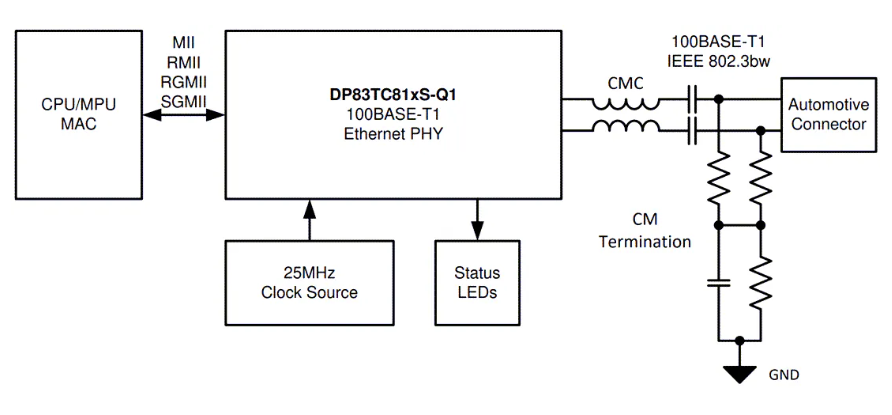

基于DP83TC812-Q1的汽车以太网PHY技术解析

DIY 流体模拟吊坠(二):第二个、第三个、更多的吊坠......

RGMII接口案例:二个设备共享一个PHY

RGMII接口案例:二个设备共享一个PHY

评论