异构集成主要指将多个不同工艺节点单独制造的芯片封装到一个封装内部,以增强功能性和提高性能。异构计算是指将CPU、GPU、FPGA、DSP等不同架构的运算单元整合到一起进行并行计算。

1)异 构集 成

异构集成(Heterogeneous Integration)

异构集成通常和单片集成电路(monolithic)相对应,我们常见的芯片都是单片集成电路,它们属于同构集成(homogeneous Integration),意味着在同一种材料上制作出所有元件。这曾经是杰克•基尔比(Jack Kilby)的伟大梦想,并最终成为现实,进而推动了信息技术的巨大进步,对人类文明的进步也产生重大影响。

异构集成和同构集成二者并不相互排斥,所有异构集成的单元都是同构集成。

异构集成(Heterogeneous Integration)准确来讲,全称为异构异质集成,异构集成可看作是其汉语的简称,这里,我们将其分为异构(HeteroStructure)集成和异质(HeteroMaterial)集成两大类。

HeteroStructureIntegration

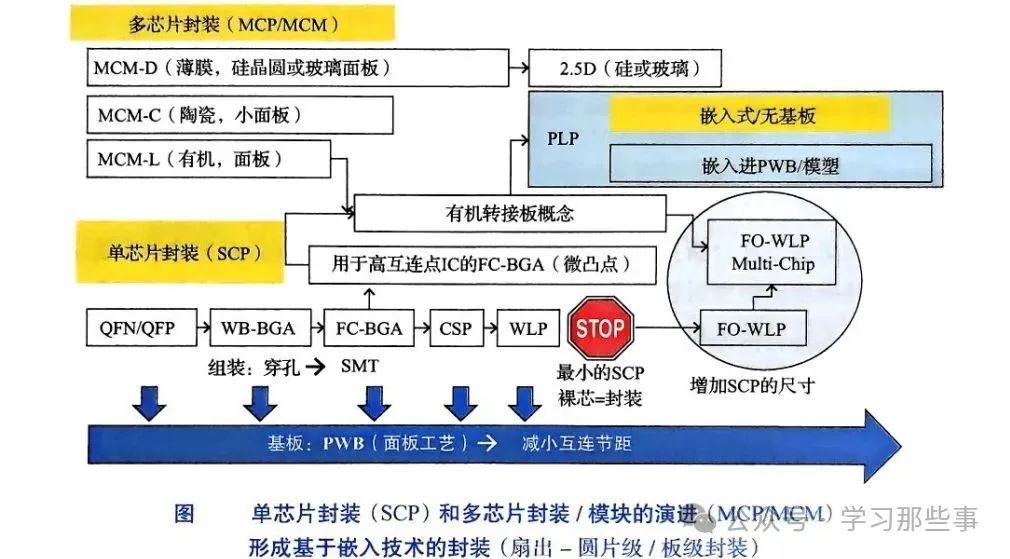

HeteroStructure Integration(异构集成)主要指将多个不同工艺节点单独制造的芯片封装到一个封装内部,以增强功能性和提高性能,可以对采用不同工艺、不同功能、不同制造商制造的组件进行封装。例如将不同厂商的10nm、28nm、45nm的小芯片通过异构集成技术封装在一起。

这里主要以硅材质的芯片为主,工程师可以像搭积木一样,在芯片库里将不同工艺节点的Chiplet小芯片通过异构集成技术组装在一起。

HeteroMaterial Integration

HeteroMaterial Integration(异质集成)是指将不同材料的半导体器件集成到一个封装内,可产生尺寸小、经济性好、灵活性高、系统性能更佳的产品。

如将Si、GaN、SiC、InP生产加工的芯片通过异质集成技术封装到一起,形成不同材料的半导体在同一款封装内协同工作的场景。

过去,出于功耗、性能、成本等因素的考虑,集成首先在单片上实施,例如SoC。近些年,由于摩尔定律日益趋缓,单片集成的发展受到了一些影响。得益于先进封装与芯片堆叠技术的创新,设计人员可以将系统集成至单个封装内形成SiP,这就推进了异构异质集成的发展。

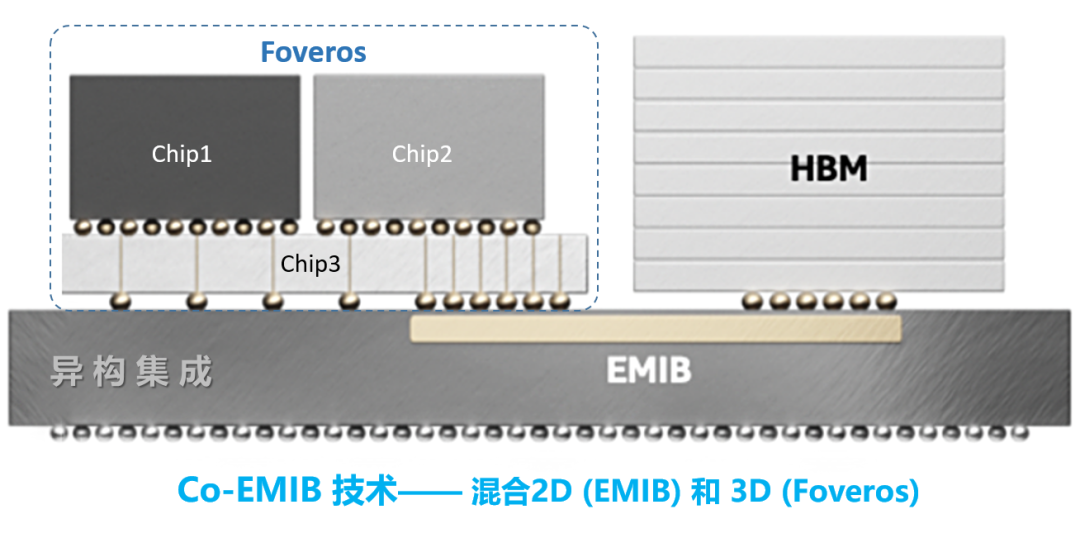

下图所示 Intel 的Co-EMIB技术就属于典型的异构集成技术。

今天,Heterogeneous Integration 异构异质集成主要是指封装层面(Package Level)的集成,其概念出现的历史并不长,是在近十年间随着先进封装技术的兴起而日益受到业界的重视,并逐渐发展为电子系统集成中最受关注的环节。

2)异 构计 算

异构计算(Heterogeneous Computing)

异构计算是指将CPU、GPU、FPGA、DSP等不同架构的运算单元整合到一起进行并行计算。

例如,CPU擅长管理和调度,比如读取数据,管理文件,人机交互等;GPU管理弱,运算强,更适合整块数据进行流处理的算法;FPGA实时性高,能管理能运算,但是开发周期长,复杂算法开发难度大;DSP适合特定算法的计算等。

当人工智能等海量计算诉求到来之后,GPU、FPGA、DSP去配合CPU进行计算的使命就自然而然的产生了,这就是异构计算。

异构计算技术从上世纪80年代中期产生,由于能有效获取高计算能力、可扩展性好、资源利用率高、发展潜力大,已成为并行计算领域中的研究热点。

近年来,人工智能持续爆发,对算力提出了更高的要求。异构计算作为大计算时代的解决方案,打破传统通用计算的限制,融合不同指令集和体系架构的计算单元,完美支持大计算场景。

异构计算的实现架构通常是CPU+ GPU/FPGA/DSP,主要由CPU完成不可加速部分的计算以及整个系统的控制调度,由GPU/FPGA/DSP完成特定的任务和加速。

异构计算是一种特殊形式的并行和分布式计算,区别于CPU计算的通用架构,整合多种计算架构如CPU、GPU、FPGA、DSP、ASIC等,可简单理解为:专人干专事,人多力量大。

3)算 力 算力(Computing Power)

算力,顾名思义就是计算能力。 算力原本是比特币处理能力的度量单位,即为CPU计算哈希函数输出的速度。现在已经成为一个描述计算能力的通用名词。

算力存在于各种硬件设备中,没有算力就没有软硬件的正常应用。高配置的电脑算力更高,可以运行复杂大型的软件,低配置的电脑算力不够,适合运行一般的办公软件。 算力受处理器的运行速度、存储、网络等因素的影响,而算力的核心在芯片。

算力为大数据和人工智能的发展提供基础保障,算力是人工智能发展的动力和引擎。

算力、大数据、人工智能,三者已经有机结合成了一个智能化的整体。目前,算力的发展迫在眉睫,否则会束缚人工智能的发展。

4)异构集成、异构计算、算力的关系

The relationship between them

关于异构集成、异构计算、算力三者之间的关系,我想了想,画了下面一张图,大致可以来描述三者之间的关系。

异构集成主要在封装层面,通过先进封装技术将不同工艺节点、不同材质的芯片集成在一起,异构计算通过整合不同架构的运算单元来进行并行计算,二者的目的都是为了提升算力。

异构计算充分利用各种计算资源的并行和分布计算技术,能够将不同制程和架构、不同指令集、不同功能的硬件进行组合,已经成为解决算力瓶颈的重要方式。

而要实现异构计算,异构集成和先进封装技术在其中扮演了关键的角色。异构集成与先进封装技术的进步使在单个封装内构建复杂系统成为了可能,能够快速达到异构计算系统内的芯片所需要的功耗、体积、性能的要求,是目前技术能够实现的最佳解决方案。

异构集成和异构计算追求的目标是使计算任务的执行具有最短时间,也就是拥有最强的算力。

5)异 构 时 代

异构时代(Heterogeneous Era)

异构技术逐渐成为主流的时代,被业界称为异构时代,这里的异构既包括异构计算也包括异构集成。

异构计算概念兴起于上世纪80年代,其热起来也是近十年间的事情,异构集成概念出现的时间不到十年,是随着先进封装技术的兴起而逐渐为业界所认可。

异构计算和异构集成两者的目的都为了提升算力。当今这个时代,异构逐渐成为一个热门词汇,因此被称为异构时代。

异构集成、异构计算都因为时代而生,这个时代,就是异构时代。

总 结

这篇文章主要搞清楚了以下几个问题:

1)异构集成全称为异构异质集成,主要是指封装层面的集成,其概念是在近十年间随着先进封装技术的兴起而日益受到业界的重视。

2)异构计算是指将CPU、GPU、FPGA、DSP等不同架构的运算单元整合到一起进行并行计算,以提高算力。

3)算力就是计算、数据处理的能力。

4)异构集成、异构计算其主要目的都是为了提升系统的算力。

5)异构集成、异构计算都因为时代而生,这个时代,就是异构时代。

审核编辑:刘清

-

SiC

+关注

关注

32文章

3865浏览量

70129 -

芯片封装

+关注

关注

14文章

623浏览量

32397 -

GaN

+关注

关注

21文章

2385浏览量

84488 -

异构计算

+关注

关注

2文章

112浏览量

17241 -

异构集成

+关注

关注

0文章

42浏览量

2356

原文标题:异构集成 与 异构计算

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于openEuler平台的CPU、GPU与FPGA异构加速实战

疆鸿智能EtherCAT转DeviceNet网关:制药产线异构集成的关键枢纽

多Chiplet异构集成的先进互连技术

西门子Innovator3D IC异构集成平台解决方案

全方位解析:什么是异构开发板?为什么选GM-3568JHF?

Chiplet与异构集成的先进基板技术

【2025九峰山论坛】破局摩尔定律:异质异构集成如何撬动新赛道?

【TEC100TAI-KIT】青翼凌云科技基于JFMQL100TAI的全国产化智能异构计算平台

商汤大装置发布基于DeepLink的异构混合调度方案

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

基于板级封装的异构集成详解

异构计算解决方案(兼容不同硬件架构)

润和软件发布StackRUNS异构分布式推理框架

如何释放异构计算的潜能?Imagination与Baya Systems的系统架构实践启示

什么是异构集成?什么是异构计算?异构集成、异构计算的关系?

什么是异构集成?什么是异构计算?异构集成、异构计算的关系?

评论