随着计算机技术的发展,单核处理器已经难以满足高性能计算的需求,众核处理器成为了一种有效的解决方案。众核处理器是指在一个芯片上集成多个处理器核心,通过并行计算提高性能和能效,众核处理器可以分为同构和异构两种类型,同构众核处理器是指所有的核心具有相同的结构和功能,异构众核处理器是指不同的核心具有不同的结构和功能,例如CPU和GPU的组合。异构众核系统是指由一个或多个异构众核处理器构成的系统,它可以利用不同类型的核心的特点,实现更高的性能和能效。

异构众核系统在高性能计算领域有着广泛的应用场景,例如科学计算、机器学习、图像处理、数据挖掘等,其优势在于可根据不同的计算任务,选择合适的核心类型,实现任务的并行化和加速。例如,CPU核心适合处理复杂的控制逻辑和数据依赖,GPU核心适合处理大规模的数据并行和浮点运算。异构众核系统的挑战在于它需要解决不同类型的核心之间的协同问题,例如任务划分、调度、映射、负载均衡、同步、通信等。这些问题涉及到异构众核系统的设计方法和关键技术,是当前研究的热点和难点。

1、异构众核系统的体系架构

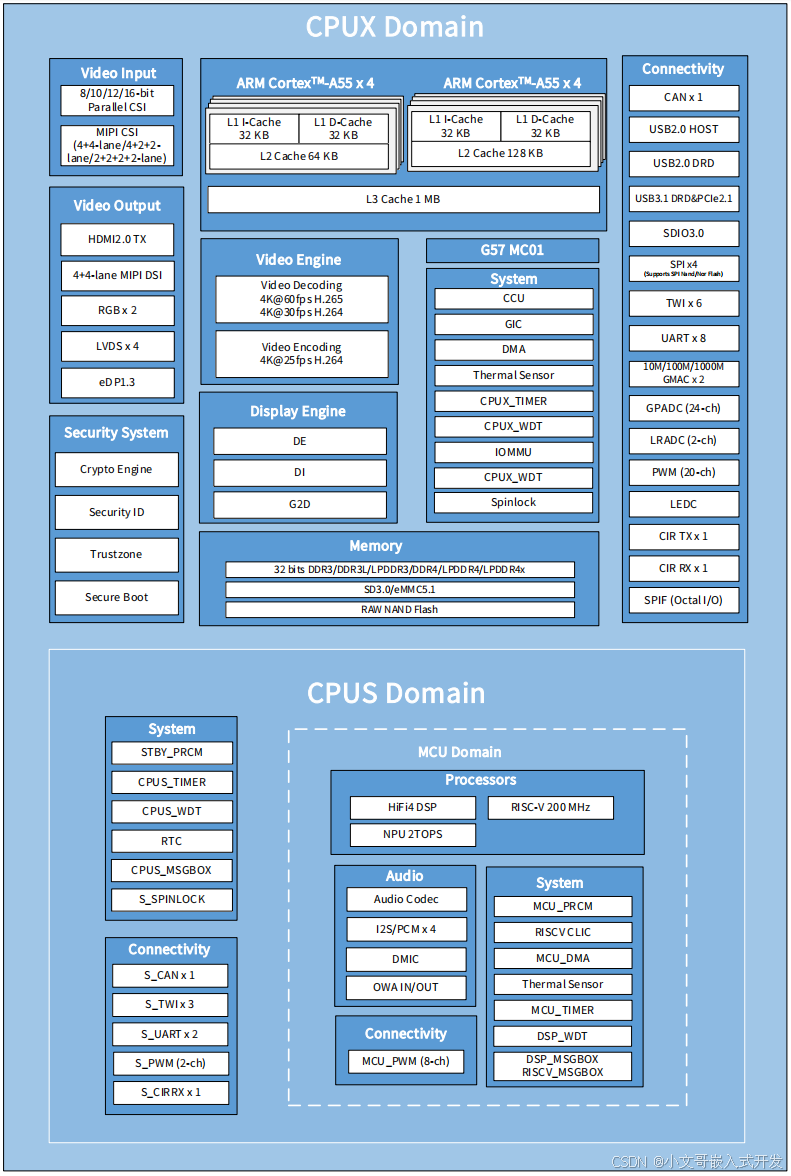

异构众核系统的体系架构可以分为两个层次,即芯片层次和系统层次。芯片层次是指一个异构众核处理器的内部结构,系统层次是指由多个异构众核处理器构成的系统的结构,异构众核系统的体系架构包括以下几个部分:

CPU核心:传统的中央处理器,它具有复杂的指令集和流水线,可以执行各种类型的指令,包括算术、逻辑、控制、分支、内存访问等。CPU核心通常具有较高的时钟频率和较大的缓存,可以实现较高的单线程性能,通常负责执行操作系统和应用程序的主要逻辑,以及管理和调度其他类型的核心。

GPU核心:指图形处理器,GPU核心它具有简单的指令集和流水线,主要执行浮点运算和数据并行指令。GPU核心通常具有较低的时钟频率和较小的缓存,但是具有较多的核心数和较高的内存带宽,可以实现较高的并行性能。负责执行应用程序的计算密集型部分,例如矩阵运算、向量运算、图像处理等。

其他类型的核心:除了CPU核心和GPU核心之外,异构众核处理器还可以集成其他类型的核心,例如数字信号处理器(DSP)、神经网络处理器(NPU)、加速器(ACC)等。这些核心通常针对某些特定的应用领域或功能进行优化,例如音频处理、视频处理、机器学习、加密解密等,通常具有专用的指令集和硬件结构,可以实现较高的性能和能效。

存储系统:存储系统是指异构众核处理器的内部存储结构,包括寄存器、缓存、共享内存、局部内存、全局内存等。存储系统的设计需要考虑不同类型的核心的存储需求和访问特点,以及不同层次的存储之间的一致性和同步问题。存储系统的性能和能效对异构众核处理器的整体性能和能效有着重要的影响。

通讯系统:通讯系统是指异构众核处理器的内部通讯结构,包括总线、网络、交换机、路由器等。通讯系统的设计需要考虑不同类型的核心之间的通讯需求和模式,以及不同类型的核心和外部设备之间的通讯接口和协议。通讯系统的性能和能效对异构众核处理器的整体性能和能效也有着重要的影响。

2、异构众核系统的优势和挑战

① 在高性能计算领域有着显著的优势性能提升:异构众核系统可以利用不同类型的核心的特点,实现任务的并行化和加速。例如,GPU核心可以执行大规模的数据并行和浮点运算,提高计算密集型任务的性能;DSP核心可以执行高效的信号处理,提高信号处理类任务的性能;NPU核心可以执行高速的神经网络运算,提高机器学习类任务的性能。异构众核系统可以根据不同的计算任务,选择合适的核心类型,实现任务的最优匹配,提高系统的整体性能。能效提升:异构众核系统可以利用不同类型的核心的特点,实现任务的节能和降耗。例如,GPU核心可以在较低的时钟频率下执行大量的并行运算,降低功耗和散热;DSP核心可以在较小的面积和功耗下执行高效的信号处理,节省资源和能源;NPU核心可以在较低的精度和复杂度下执行高速的神经网络运算,减少开销和延迟。异构众核系统可以根据不同的计算任务,选择合适的核心类型,实现任务的最优配置,提高系统的整体能效。

灵活性提升:异构众核系统可以利用不同类型的核心的特点,实现任务的多样化和适应性。例如,GPU核心可以支持多种编程模型和优化技术,适应不同的应用需求和特性;DSP核心可以支持多种信号处理算法和功能,适应不同的信号源和目标;NPU核心可以支持多种神经网络模型和框架,适应不同的机器学习任务和场景。异构众核系统可以根据不同的计算任务,选择合适的核心类型,实现任务的最优适配,提高系统的整体灵活性。

② 在高性能计算领域也面临着一些挑战:

编程难度:异构众核系统的编程需要考虑不同类型的核心的特点和限制,以及不同类型的核心之间的协同和协调问题。例如,GPU核心的编程需要考虑数据并行度、内存访问模式、同步机制等;DSP核心的编程需要考虑信号处理算法、数据格式、精度等;NPU核心的编程需要考虑神经网络模型、框架、参数等。异构众核系统的编程还需要考虑任务的划分、调度、映射、负载均衡、同步、通信等问题,这些问题增加了异构众核系统的编程难度和复杂度,需要开发者具备较高的专业知识和技能。兼容性问题:异构众核系统的兼容性需要考虑不同类型的核心的兼容性,以及不同类型的核心和外部设备的兼容性。例如,GPU核心的兼容性需要考虑不同厂商和型号的GPU之间的兼容性,以及GPU和CPU之间的兼容性;DSP核心的兼容性需要考虑不同厂商和型号的DSP之间的兼容性,以及DSP和其他类型的核心之间的兼容性;NPU核心的兼容性需要考虑不同厂商和型号的NPU之间的兼容性,以及NPU和其他类型的核心之间的兼容性。异构众核系统的兼容性还需要考虑不同类型的核心和主存储器、输入输出设备之间的兼容性,这些问题增加了异构众核系统的兼容性问题和风险,需要开发者和用户进行充分的测试和验证。可靠性问题:异构众核系统的可靠性需要考虑不同类型的核心的可靠性,以及不同类型的核心之间的可靠性。例如,GPU核心的可靠性需要考虑GPU的故障、错误、异常等情况,以及GPU和CPU之间的错误检测和恢复机制;DSP核心的可靠性需要考虑DSP的故障、错误、异常等情况,以及DSP和其他类型的核心之间的错误检测和恢复机制;NPU核心的可靠性需要考虑NPU的故障、错误、异常等情况,以及NPU和其他类型的核心之间的错误检测和恢复机制。异构众核系统的可靠性还需要考虑不同类型的核心之间的容错和备份机制,这些问题增加了异构众核系统的可靠性问题和成本,需要开发者和用户进行充分的保障和维护。

3、研究现状和未来展望

异构众核系统高性能计算架构是一个前沿的研究领域,目前已经取得了一些重要的进展和成果,但是还存在一些问题和挑战,需要进一步的研究和探索。

异构众核系统高性能计算架构的研究主要集中在以下几个方面:

异构众核处理器的设计和实现:这方面的研究主要关注如何设计和实现具有不同类型的核心的异构众核处理器,以提高其性能和能效。例如,介绍了一种基于FPGA的异构众核处理器的设计和实现,该处理器包括四个CPU核心和四个GPU核心,可以实现高性能计算的加速和节能。

异构众核系统的编程模型和优化技术:这方面的研究主要关注如何开发和优化适合异构众核系统的编程模型和优化技术,以提高其编程效率和性能。例如,介绍了一种基于OpenCL的异构众核系统的编程模型和优化技术,该模型和技术可以实现异构众核系统的任务划分、调度、映射、同步和通信的自动化和优化。

- 异构众核系统的应用案例和评估方法:这方面的研究主要关注如何开发和评估适合异构众核系统的高性能计算应用案例,以展示其性能和能效的提升。例如,介绍了一种基于异构众核系统的气候模拟的应用案例和评估方法,该案例和方法可以展示异构众核系统在气候模拟中的运行时间的缩短约30倍和能耗的降低约15倍。

异构众核系统高性能计算架构的研究将面临以下几个方面的挑战和机遇:

- 异构众核处理器的多样化和复杂化:随着计算技术的发展,异构众核处理器将会集成更多的不同类型的核心,例如量子处理器、光子处理器、生物处理器等,这将使异构众核处理器的结构和功能更加多样化和复杂化,也将带来更高的性能和能效的潜力。这将需要研究更加通用和灵活的异构众核处理器的设计和实现方法,以适应不同类型的核心的特点和需求。

- 异构众核系统的规模化和分布化:随着计算需求的增长,异构众核系统将会构成更大的规模和更广的分布,例如云计算、边缘计算、物联网等,这将使异构众核系统的结构和功能更加规模化和分布化,也将带来更高的性能和能效的挑战。这将需要研究更加高效和可靠的异构众核系统的编程模型和优化技术,以适应不同规模和分布的系统的特点和需求。

- 异构众核系统的智能化和自适应化:随着计算环境的变化,异构众核系统将会面临更多的不确定性和动态性,例如任务的变化、系统的变化、用户的变化等,这将使异构众核系统的结构和功能更加智能化和自适应化,也将带来更高的性能和能效的机会。这将需要研究更加智能和自适应的异构众核系统的运行时系统和中间件,以适应不同环境的变化和需求。

- 异构众核系统的应用化和评估化:随着计算应用的发展,异构众核系统将会涉及更多的高性能计算应用领域和场景,例如人工智能、大数据、虚拟现实等,这将使异构众核系统的结构和功能更加应用化和评估化,也将带来更高的性能和能效的展示和验证。这将需要研究更加丰富和实用的异构众核系统的应用案例和评估方法,以展示不同应用领域和场景的性能和能效的提升。

异构众核系统高性能计算架构是一个前沿的研究领域,具有重要的理论意义和实际价值,值得进一步的研究和探索。

来源:汇天科技

-

处理器

+关注

关注

68文章

20148浏览量

247106 -

异构

+关注

关注

0文章

45浏览量

13490 -

智能计算架构

+关注

关注

0文章

1浏览量

167

发布评论请先 登录

基于DSP与FPGA异构架构的高性能伺服控制系统设计

MYD-LD25X Cortex-M33实时核开发实战解析

探索CPU架构的奥秘,揭秘高性能计算的隐形引擎

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 异构架构下的智能边缘计算标杆

知合计算:RISC-V架构创新,阿基米德系列剑指高性能计算

异构计算解决方案(兼容不同硬件架构)

如何释放异构计算的潜能?Imagination与Baya Systems的系统架构实践启示

紫光展锐4G旗舰性能之王智能穿戴平台W527登场 一大核三小核异构处理器架构

能效提升3倍!异构计算架构让AI跑得更快更省电

AI SoC#全志T527八核工业级高性能人工智能芯片解读

异构众核系统高性能计算架构

异构众核系统高性能计算架构

评论