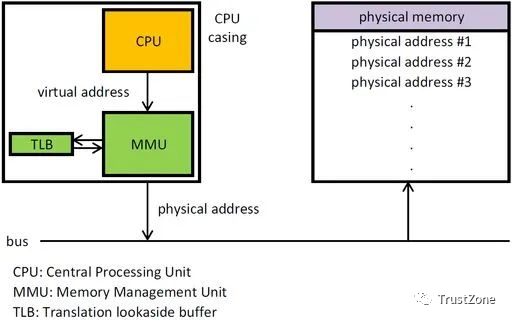

TLB 是 translation lookaside buffer 的简称。首先,我们知道 MMU 的作用是把虚拟地址转换成物理地址。

虚拟地址和物理地址的映射关系存储在页表中,而现在页表又是分级的。

64 位系统一般都是 3~5 级。

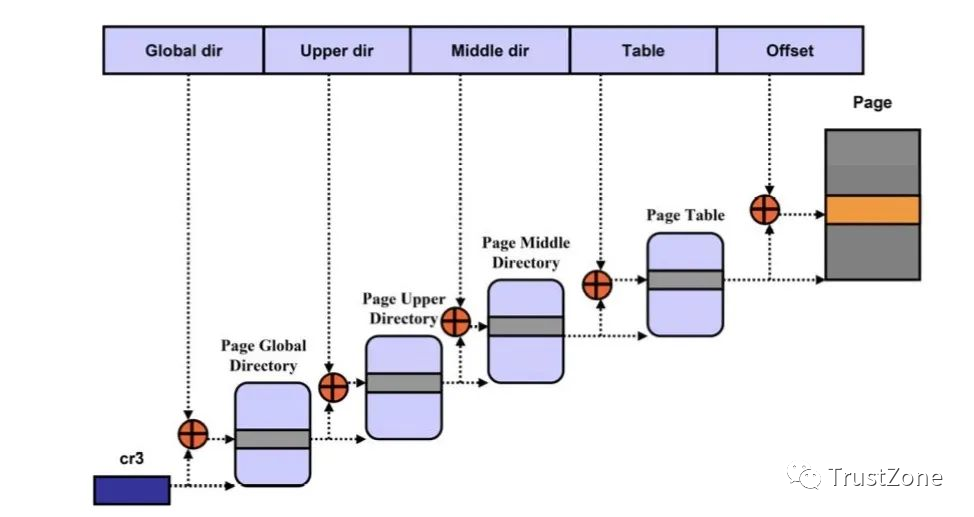

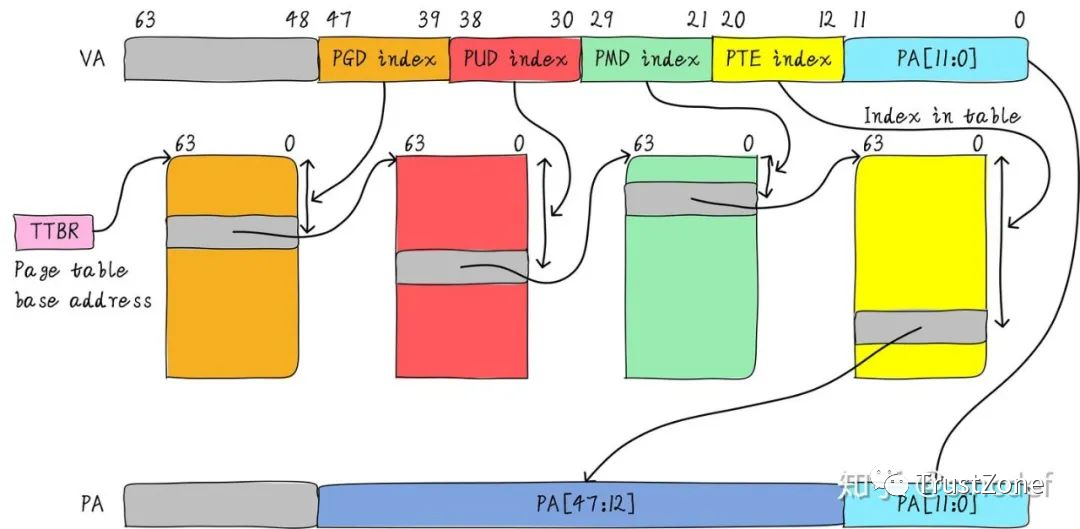

常见的配置是 4 级页表,就以 4 级页表为例说明。

分别是 PGD、PUD、PMD、PTE 四级页表。

在硬件上会有一个叫做页表基地址寄存器,它存储 PGD 页表的首地址。

MMU 就是根据页表基地址寄存器从 PGD 页表一路查到 PTE,最终找到物理地址(PTE页表中存储物理地址)。

这就像在地图上显示你的家在哪一样,我为了找到你家的地址,先确定你是中国,再确定你是某个省,继续往下某个市,最后找到你家是一样的原理。一级一级找下去。(这个比喻真的不错)

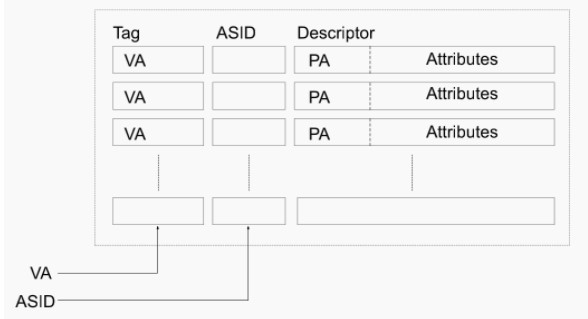

这个过程你也看到了,非常繁琐。如果第一次查到你家的具体位置,我如果记下来你的姓名和你家的地址。下次查找时,是不是只需要跟我说你的姓名是什么,我就直接能够告诉你地址,而不需要一级一级查找。

四级页表查找过程需要四次内存访问。延时可想而知,非常影响性能。页表查找过程的示例如下图所示。以后有机会详细展开,这里了解下即可。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

31文章

5619浏览量

130395 -

内存

+关注

关注

9文章

3234浏览量

76503 -

硬件

+关注

关注

12文章

3629浏览量

69165 -

MMU

+关注

关注

0文章

92浏览量

19288

发布评论请先 登录

相关推荐

热点推荐

详解TLB的作用及工作原理

了TLB,TLB是Translation Lookaside Buffer的简称,可翻译为“地址转换后援缓冲器”,也可简称为“快表”。简单地说,TLB就是页表的Cache,其中存储了当前最可能被访问

发表于 05-12 14:41

•5590次阅读

请问AM335 u-boot 中的MMU,gd->arch.tlb_addr是在哪里初始化的?

本帖最后由 一只耳朵怪 于 2018-6-20 15:46 编辑

在board_init_f 函数中,只有定义了CONFIG_SYS_DCACHE_OFF,才会对 tlb_addr 初始化

发表于 06-20 02:06

labview2015调用tlb库错误信息:LabVIEW: 输入为空引用句柄或之前已删除的引用句柄。

一个设备的控制API给的是*.tlb,使用工具注册后以ActiveX的方式加载到labview中,运行报错如下。不知为何报错?请有经验的大牛们指导一二。谢谢测试程序(2015)+API的tlb库和注册工具见附件

发表于 07-12 14:25

FIDEMAILATION中的TLB异常

我从SMTP.C文件中找到了FIDEMAILATION中的TLB异常。这似乎只有当我在优化级别1并运行没有断点的例程时才发生。如果我跨过它,一切似乎都起作用了。我在和谐1.04,XC 1.34

发表于 09-18 13:22

以Freescale的E500内核为例简单介绍TLB Entry基本组成结构

称之为页表(Page Table)。最容易的想到的是使用主存储器存放这个映射关系表,但是没有程序能够忍受在使用虚拟地址访问一段物理空间时,首先需要从主存储器的页表中获得物理地址。使用TLB

发表于 09-07 14:38

看一条关于TLB维护的指令

今天来看一条关于TLB维护的指令,无效操作指令TLBI。TLBI指令用于TLB无效操。TLBI指令的编码格式如下:TLBI的语法格式如下:TLBI <tlbi_op>

发表于 02-16 13:59

P2020 TLB0/TLB1失效的原因?怎么解决?

P2020初始化时,需要通过MMUCSR0(MMU Control and Status Register 0)使TLB0和TLB1失效,我的问题是TLB0/TLB1失效:如果

发表于 03-21 07:57

嵌入式处理器的TLB电路设计

摘要:为了提高基于虚拟存储技术的嵌入式处理器的性能,本文提出了一种用于高效加速地址转换的TLB电路结构该电路采用64-entries的全关联结构,硬件支持基于段及不同大小页的转

发表于 05-12 10:01

•18次下载

CPU场景下的TLB相关细节

一、前言 进程切换是一个复杂的过程,本文不准备详细描述整个进程切换的方方面面,而是关注进程切换中一个小小的知识点:TLB的处理。为了能够讲清楚这个问题,我们在第二章描述在单CPU场景下一些和TLB

Versal ACAP、APU - DSB 指令后可能会发生推测性 TLB 填充

和 ISB 的组合可防止随后的猜测。但是,对于在 DSB SYS + ISB 之后执行页面转换的单次加载、存储或其他内存操作,可推测在 DSB SYS + ISB 完成之前的初始查找中是否发生了 TLB 错误,并填充新的 TLB 条目。

发表于 08-05 17:27

•767次阅读

TLB成功开发出CXL内存模块PCB,并向三星和SK海力士提供首批样品

近日,韩国上市PCB制造商TLB (KOSDAQ:356860)成功开发出CXL内存模块PCB,并已独家向三星电子和SK海力士提供了6款以上的首批样品。

为什么要有TLB

为什么要有TLB

评论