什么是走线的拓扑架构?怎样调整走线的拓扑架构来提高信号的完整性?

走线的拓扑架构是指电子设备内部的信号线路布局方式。它对信号传输的完整性和稳定性有着重要影响。正确的走线拓扑架构可以降低信号传输中的噪声和干扰,提高信号的完整性和可靠性。在设计和调整走线拓扑架构时,需要考虑信号线路的长度、走向、分布以及与其他线路之间的距离等因素。下面将详细介绍走线的拓扑架构及其调整方法。

1. 单线拓扑架构:

单线拓扑架构是最基本的走线方式,信号线一条一条地布置在电路板上。这种方式简单直观,但容易受到干扰和串扰。当信号线较长或走向接近其他高频线路时,会受到电磁辐射和干扰。为了改善信号的完整性,可以采用以下方法:

- 使用屏蔽线材:屏蔽线材可以有效地减少外界干扰对信号的影响。

- 增加地线:增加地线可以提高信号的接地质量,减少干扰和串扰。

- 增加信号线的距离:增加信号线与其他线路的距离,减少干扰。

2. 点对点拓扑架构:

点对点拓扑架构是在单线拓扑架构的基础上进行改进,在信号源与接收器之间建立直接连接。这种方式可以减少信号线的长度,降低传输时的延迟和干扰。对于高频信号或要求较高的应用,采用点对点拓扑架构可以提高信号完整性。在设计和调整时,需要注意以下几点:

- 优化信号线长度:尽量缩短信号线的长度,减少传输延迟和干扰。

- 选择合适的线材:选用低衰减、低干扰的线材可以提高信号的传输质量。

- 避免信号线的交叉:尽量避免信号线之间的交叉,减少串扰。

3. 总线拓扑架构:

总线拓扑架构是将多个设备连接到共享总线上,信号通过总线进行传输。这种方式适用于多设备之间频繁通信的场景,如计算机内部的数据传输。在设计和调整总线拓扑架构时,需要注意以下几点:

- 优化总线长度:尽量缩短总线的长度,减少信号传输时的延迟和干扰。

- 控制总线上的设备数量:过多的设备连接到同一总线上会增加总线负载,影响信号完整性。适当控制设备数量可以提高信号传输质量。

- 使用合适的总线协议:选择合适的总线协议可以提供更好的信号完整性和稳定性。

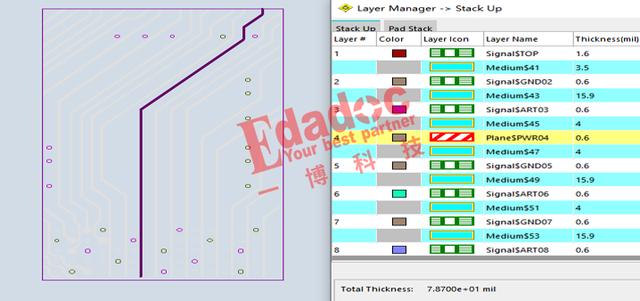

4. 平面拓扑架构:

平面拓扑架构是将信号线按照平面布置在电路板上。这种方式可以减少信号线的长度,降低信号传输时的延迟和干扰。在设计和调整平面拓扑架构时,需要注意以下几点:

- 优化信号线布局:合理布置信号线的走向,避免信号线之间的交叉和靠近其他高频线路。

- 使用屏蔽层:在电路板的外层增加屏蔽层,可以有效地减少外界干扰对信号的影响。

- 分割电源和地线:将电源和地线分割为多个区域,减少信号线与电源地线之间的干扰。

总之,走线的拓扑架构对信号完整性和稳定性有着重要影响。通过优化信号线的布局方式、长度和距离,选择合适的线材和协议,可以提高信号的完整性。在设计和调整走线拓扑架构时,需要考虑具体应用场景和需求,并结合实际情况进行合理的布局和调整。

-

信号完整性

+关注

关注

68文章

1500浏览量

98265 -

信号线

+关注

关注

2文章

189浏览量

22286

发布评论请先 登录

PCB板双面布局的DDR表底走线居然不一样

到底DDR走线能不能参考电源层啊?

PCB如何调整拓扑结构,以此提高信号完整性?

AD7792电流源输出在走线时,如果走线过长,且走线很细10mil,会导致电流源大小衰减吗?

知识分享-传输线的返回电流(信号完整性揭秘)

了解信号完整性的基本原理

什么是走线的拓扑架构?怎样调整走线的拓扑架构来提高信号的完整性?

什么是走线的拓扑架构?怎样调整走线的拓扑架构来提高信号的完整性?

评论