上期我们介绍了什么是寄生电感,以及寄生电感对输入端的影响,本期,我们来聊一下寄生电感对Buck电路中开关管的影响。

寄生电感对开关管的影响

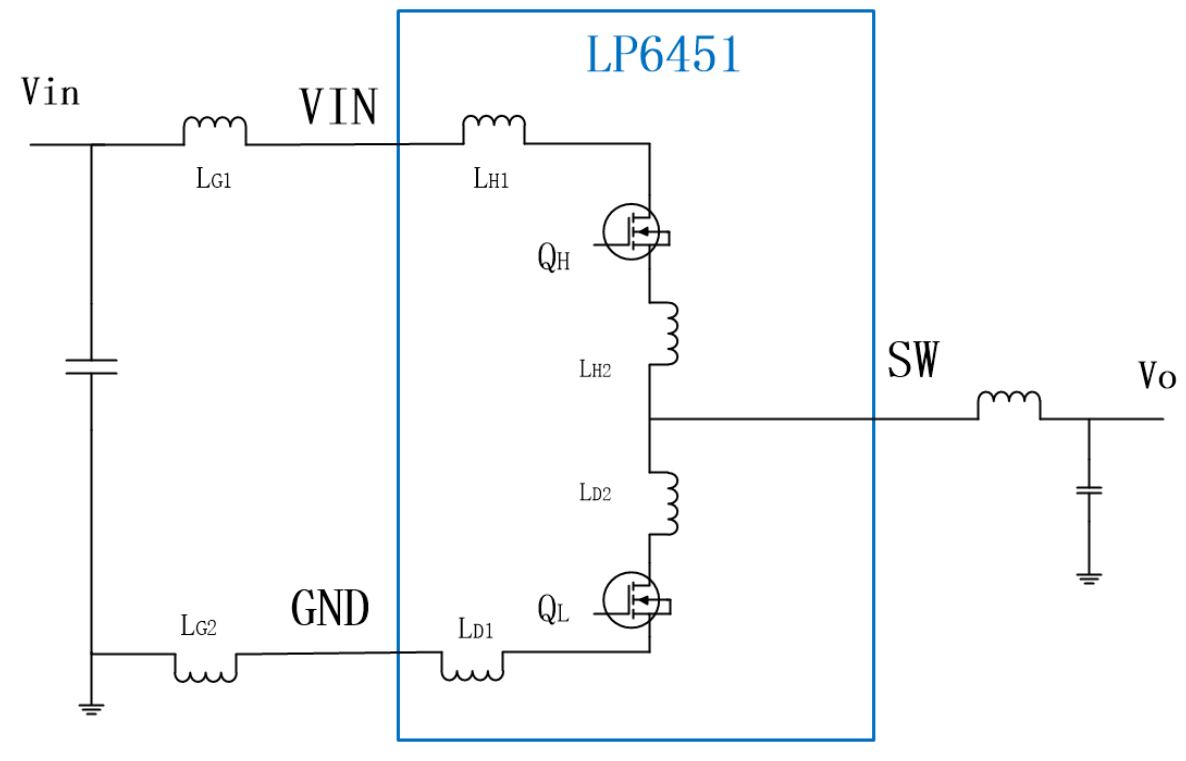

LP6451内部集成了两个MOS管,构成同步Buck电路中所必须的上管和下管,同样由于PCB上的走线,Die与芯片引脚之间Bonding线都会带来寄生电感,我们在分析LP6451的MOS管应力时,就需要把这些寄生电感都考虑进来,而图1就是LP6451功率部分的实际等效电路图。

图1:LP6451实际应用等效图

其中,QH和QL分别为LP6451内部集成的Buck电路的上管和下管,而LG1和LG2为输入电容到芯片VIN和GND引脚之间的PCB走线所带来的寄生电感,LH1和LD1为LP6451的Bonding线带来的寄生电感,LH2和LD2则分别为上下管到引脚SW的寄生电感。在上下管开关切换的过程中,这些寄生电感所产生的感应电压都会对LP6451内部的MOS管带来额外的电压应力。

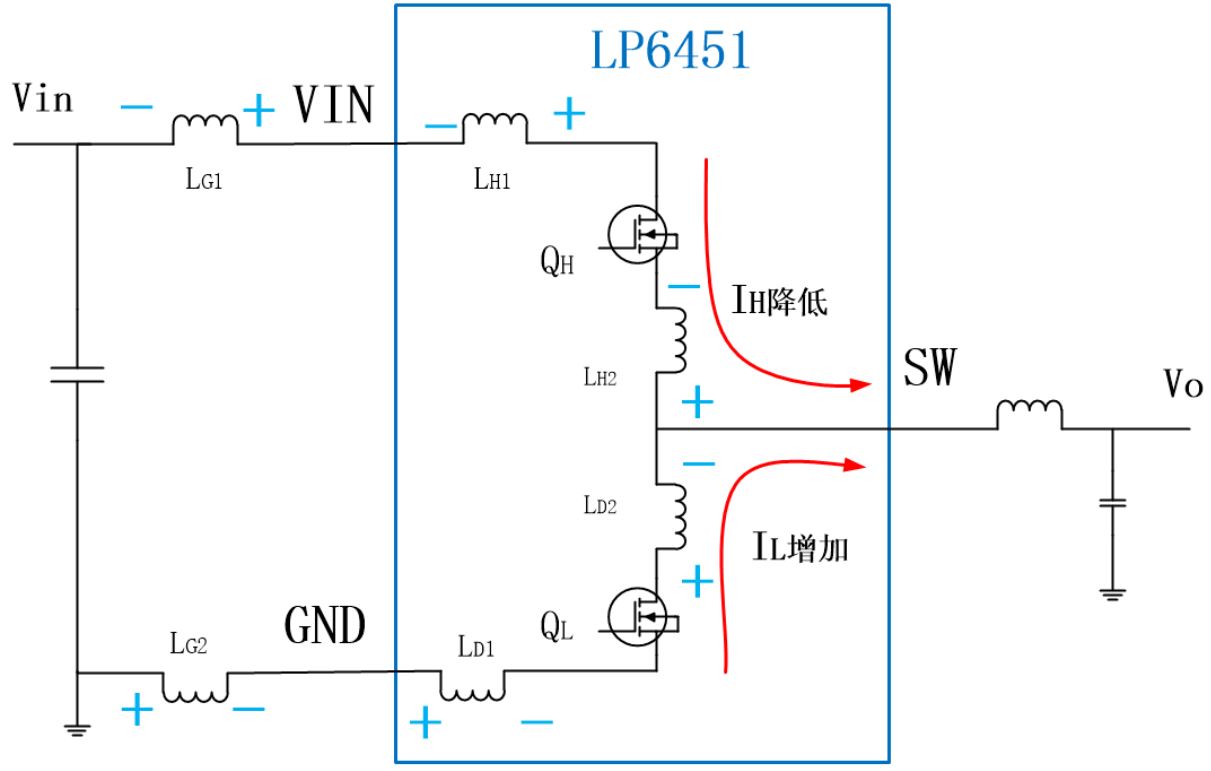

比如,当上管QH开始关断,下管QL开始导通时,流经上管QH的电流IH逐渐减少,流经下管QL的电流IL逐渐增加,此时,在寄生电感LG2和LD1上会产生左高右低的感应电压,寄生电感LD2上会产生下高上低的感应电压,如图7所示。此时,我们使用示波器探头去测量LP6451的引脚SW的波形,探头正端接LP6451的引脚SW,地线接输入电容的地线,就会发现SW的最低电压会比正常LD2体二极管导通时的电压-0.7V还要更低。如果将输入电容更加远离LP6451,那么寄生电感LG2则会变得更大,产生的感应电压也就越大,此时测试SW引脚的负压值就会越大。如图2所示,实测SW的电压最低可以达到-4V左右。

图2:下管开通时刻的感应电压

同样,当上管电流减小时,会使得寄生电感LG1和LH1产生左低右高的感应电压,LH2产生上低下高的感应电压,这些感应电压连同输入电压Vin会共同加在上管QH的漏极和源极之间,使得上管QH实际承受的电压要大于Buck电路的输入电压。如果这些寄生电感比较大的话,上管QH就会存在击穿的风险。

下期我们将介绍寄生电感与哪些因素有关,以及我们该如何降低寄生电感对电路的影响。

文章来源:微源半导体

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54379浏览量

468994 -

pcb

+关注

关注

4415文章

23955浏览量

426011 -

MOS管

+关注

关注

111文章

2811浏览量

77780 -

寄生电感

+关注

关注

1文章

171浏览量

15098

发布评论请先 登录

嵌入式磁集成:SST固态变压器PEBB内部80%寄生电感消除与电磁辐射抑制

突破SiC模块短路保护响应极限:基于源极寄生电感的 200ns 超快故障感知算法

突破 200ns 响应:利用SiC模块源极寄生电感的超快短路故障感知算法

碳化硅(SiC)MOSFET驱动回路寄生电感的量化评估与关断过冲抑制技术综合研究

SiC MOSFET驱动电路的寄生电感抑制技巧

基于SiC MOSFET和低寄生电感 PCB 层叠母排的 50kHz变频器设计

PCB设计知识又增加了:听都没听过的电容,滤波性能竟然这么好?

寄生电感致电流采样失真:关键问题与解决办法

破局SiC高频寄生电感难题,派恩杰推出嵌入式封装方案

派恩杰PCB嵌入式功率模块的性能优势

一文带你了解线路寄生电感对开关器件的影响及解决方案

电源功率器件篇:线路寄生电感对开关器件的影响

叠层母排在IGBT变流器中的应用(1)

寄生电感的影响

寄生电感的影响

评论