用 HLS 实现 UART

介绍

UART 是一种旧的串行通信机制,但仍在很多平台中使用。它在 HDL 语言中的实现并不棘手,可以被视为本科生的作业。在这里,我将通过这个例子来展示在 HLS 中实现它是多么容易和有趣。

因此,从概念上讲,这是一个微不足道的项目;然而,它对于对 HLS 感兴趣的人来说是有启发性的。

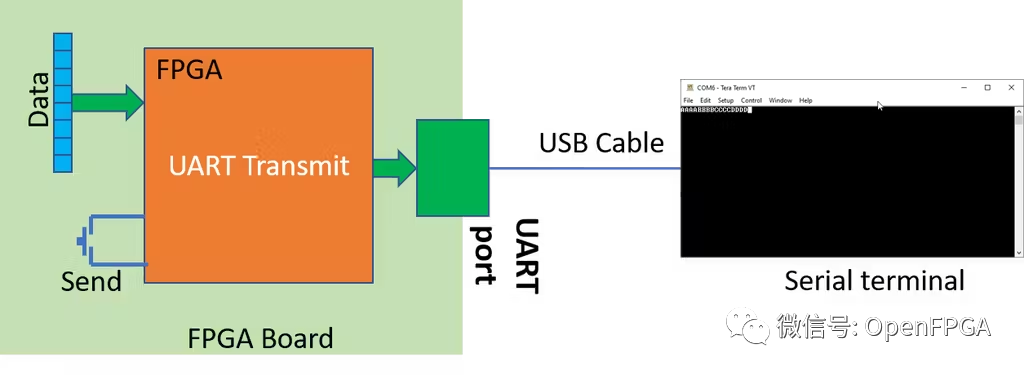

现在项目定义: 下图显示了项目的简单结构。

我们在 FPGA 中的设计UART发送,每当按下按钮时就会将其发送到计算机上的串口调试助手。

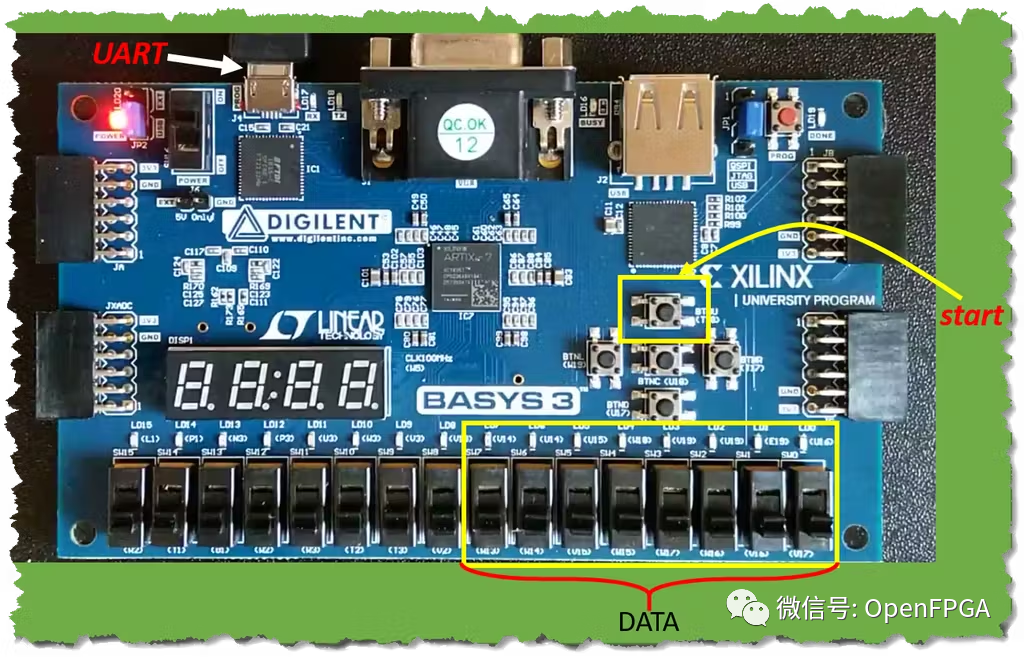

FPGA 板上的八个滑动开关用于输入数据字节(例如字母或符号的 ASCII 代码)。此外,UP 按钮用作发送控制键。

设计很简单,程序本身能接受开发板上拨码开关的数据,然后添加一个“0”起始位和一个“1”停止位,最后以9600 bit/s的波特率发送出去。

首先需要根据开发板上的时钟(本例是100MHz),进行分频,生成串口发送所需的时钟。

booldelay(longlongintn){

staticbooldummy=0;

for(longlongintj=0;j< n; j++) {

#pragma HLS pipeline

dummy = !dummy;

}

return dummy;

}

void uart_baudrate_clock(bool &baudrate_clk) {

static bool s = 0;

s=!s;

baudrate_clk = s;

delay(5208);

}

生成速率时钟后,简单的状态机可以将数据发送出去。

voiduart_data_transfer(bool&uart_tx,ap_uint<8>data,boolbaud_rate_clock,boolstart){ staticboolsend_bit=1; staticboolstart_state=0; staticbooltransfer=0; staticunsignedintcount=0; staticintstate=0; ap_uint<10>d=((bool)0b1,(ap_int<8>)data,(bool)0b0); if(start==1&&start_state==0){ transfer=1; start_state=1; count=0; } if(start==0&&start_state==1){ start_state=0; } if(baud_rate_clock==1&&state==0&&transfer==1){ send_bit=d[count++]; if(count==10){ transfer=0; } state=1; } if(baud_rate_clock==0&&state==1){ state=0; } uart_tx=send_bit; }

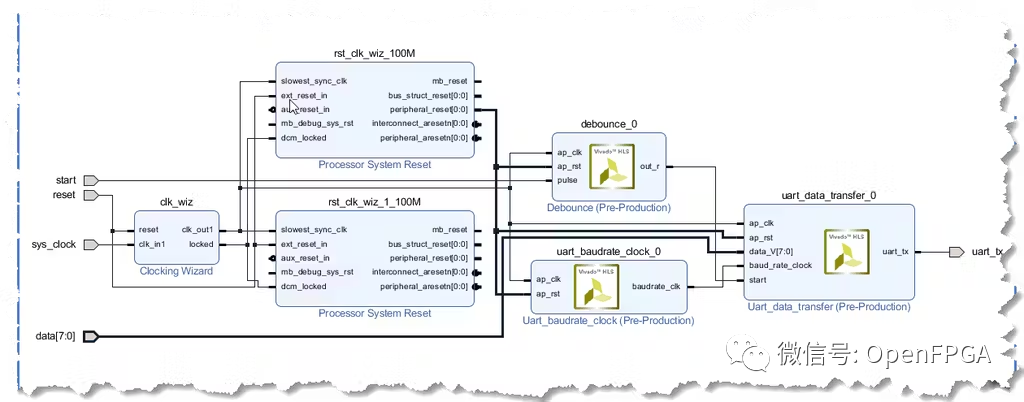

将这些代码综合到 RTL 模块后,我们可以创建 Vivado 项目并生成 FPGA 比特流,并验证。

总结

很简单的一个实例,大家可以自行和HDL实现的方式进行对比。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22503浏览量

639290 -

计算机

+关注

关注

19文章

7841浏览量

93464 -

uart

+关注

关注

22文章

1320浏览量

106977 -

串行通信

+关注

关注

4文章

609浏览量

37228 -

HLS

+关注

关注

1文章

135浏览量

25981

发布评论请先 登录

相关推荐

热点推荐

如何使用AMD Vitis HLS创建HLS IP

本文逐步演示了如何使用 AMD Vitis HLS 来创建一个 HLS IP,通过 AXI4 接口从存储器读取数据、执行简单的数学运算,然后将数据写回存储器。接着会在 AMD Vivado Design Suite 设计中使用此 HLS

探索Vivado HLS设计流,Vivado HLS高层次综合设计

设计来满足各种约束 用不用的指令来探索多个HLS解决方案 2.实验内容 实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench

如何用HLS实现UART呢?

UART 是一种旧的串行通信机制,但仍在很多平台中使用。它在 HDL 语言中的实现并不棘手,可以被视为本科生的作业。在这里,我将通过这个例子来展示在 HLS 中实现它是多么容易和有趣。

新手求助,HLS实现opencv算法加速的IP在vivado的使用

我照着xapp1167文档,用HLS实现fast_corners的opencv算法,并生成IP。然后想把这个算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,这个demo里

发表于 01-16 09:22

Vivado HLS实现OpenCV图像处理的设计流程与分析

《》数据类型,这种类型用于模型化视频像素流处理,实质等同于hls::steam《》流的类型,而不是OpenCV中在外部memory中存储的matrix矩阵类型。因此,在HLS实现OpenCV的设计中

发表于 07-08 08:30

Vivado HLS设计流的相关资料分享

多个HLS解决方案2.实验内容实验中文件中包含一个矩阵乘法器的实现,实现两个矩阵inA和inB相乘得出结果,并且提供了一个包含了计算结果的testbench文件来与所得结果进行对比验证。...

发表于 11-11 07:09

用Vivado-HLS实现低latency 除法器

1 Vivado HLS简介 2创建一个Vivado-HLS工程 2.1打开Vivado HLS GUI 2.2创建新工程 在 Welcome Page, 选择Create New Project

发表于 12-04 10:07

•0次下载

TI配置Hercules ARM安全MCU SCI和LIN 模块如何用于UART通信

TI配置Hercules ARM安全MCU SCI和LIN 模块如何用于UART通信

发表于 05-28 08:33

•10次下载

XIlinx利用HLS进行加速设计进度

RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构。Xilinx官方文档表示利用HLS进行设计可以大大加速设计进度:

使用HLS封装的缩放IP来实现视频图像缩放功能

这里向大家介绍使用HLS封装的缩放IP来实现视频图像缩放功能。将HLS封装的缩放IP加入到OV5640图像传输系统,验证图像放大和缩小功能。

FPGA——HLS简介

是Vitis HLS。在Vivado 2020版本中替代原先的Vivado HLS, 功能略有差异。 HLS 的机理 简单地讲,HLS采样类似C语言来设计FPGA 逻辑。但是要

HLS协议实现

HLS,Http Live Streaming 是由Apple公司定义的用于实时流传输的协议,HLS基于HTTP协议实现,传输内容包括两部分,一是M3U8描述文件,二是TS媒体文件。

调用HLS的FFT库实现N点FFT

在HLS中用C语言实现8192点FFT,经过测试,实验结果正确,但是时序约束不到100M的时钟,应该是设计上的延时之类的比较大,暂时放弃这个方案,调用HLS中自带的FFT库(hls:f

如何用HLS实现UART

如何用HLS实现UART

评论