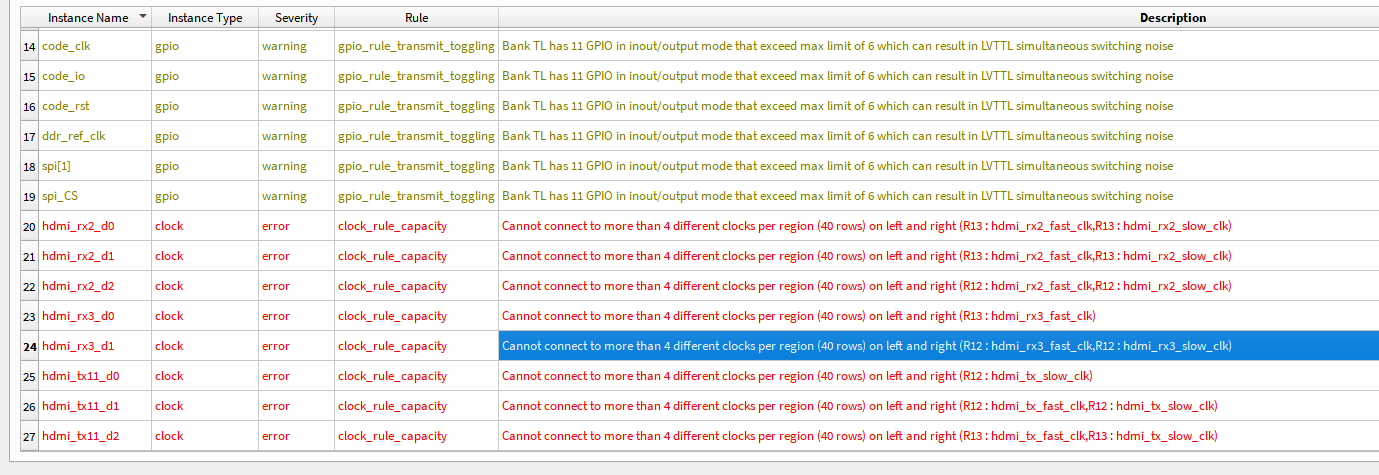

报错:cannot connect to more than 4 different clocks per region on left and right

今天在Ti180分配LVDS的时候出现了这个错误。原因是在pinout文件中对应的Clock Region中,不能超过4个时钟去驱动。

也就是GPIOR_PN_42,41,40三组差分对,不能由两组LVDS来驱动,因为每组LVDS时钟有lvds_fast_clk和lvds_slow_clk两个,两组就会有4个时钟在Region clock R13区域。

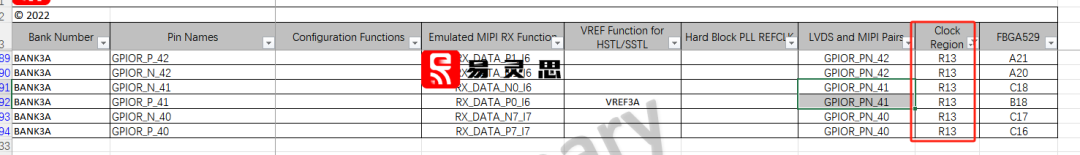

| Emulated MIPI RX Function | LVDS and MIPI Pairs | Clock Region |

| RX_DATA_P1_I6 | GPIOR_PN_42 | R13 |

| RX_DATA_N1_I6 | GPIOR_PN_42 | R13 |

| RX_DATA_N0_I6 | GPIOR_PN_41 | R13 |

| RX_DATA_P0_I6 | GPIOR_PN_41 | R13 |

| RX_DATA_N7_I7 | GPIOR_PN_40 | R13 |

| RX_DATA_P7_I7 | GPIOR_PN_40 | R13 |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟

+关注

关注

11文章

1999浏览量

135230 -

lvds

+关注

关注

2文章

1242浏览量

70220 -

易灵思

+关注

关注

6文章

66浏览量

5587

发布评论请先 登录

相关推荐

热点推荐

赛灵思FPGA电源解决方案全解析

赛灵思FPGA电源解决方案全解析 在当今的电子设计领域,现场可编程门阵列(FPGA)凭借其出色的设计灵活性和较低的工程成本,在众多应用和终端市场中占据了重要地位。然而,FPGA的电源设计和管理却是一

在Gnome桌面环境下启动cutefish终端等应用会报错如何解决?

环境(Wayland)下启动cutefish终端等应用会报错

user@starfive:~/cutefish$ cutefish-terminalQSocketNotifier: Can only

发表于 02-27 07:26

易灵思助力2025年全国大学生嵌入式芯片与系统设计竞赛圆满落幕

2025年11月30日,第八届全国大学生嵌入式芯片与系统设计竞赛——FPGA创新设计赛道全国总决赛在南京圆满落下帷幕。在这场代表国内FPGA领域最高水平的大学生赛事中,易灵思(深圳)科技有限公司作为

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

随着 RISC -V处理器在 FPGA 领域的广泛应用,易灵思 FPGA 的 Sapphire RISC-V 内核凭借软硬核的灵活支持,为开发者提供多样选择。本文深入探讨 Sapphire SoC 中 RISC - V 平台级

易灵思助力上海集成电路紧缺人才培训项目顺利结课

的核心企业,易灵思深度参与本次培训,从技术理论到实战操作全程赋能,与学员们共同探索FPGA的创新应用与未来潜力。

易灵思2025 FPGA技术研讨会成都站圆满收官

金秋九月,芯聚蓉城。9月16日下午,易灵思(Elitestek)在成都希顿酒店成功举办了以“蓉芯聚力·易启未来”为主题的技术研讨会。本次盛会吸引了成都及周边地区众多行业工程师、技术爱好

易灵思与思特威第二届机器视觉方案大会圆满收官

近日,由易灵思与思特威联合举办的第二届机器视觉方案大会在深圳福田会展中心成功举行。本次大会以技术驱动与应用落地为核心,汇聚了行业专家、合作伙伴与资深工程师,共同探讨了机器视觉领域的前沿

易灵思与南京大学集成电路学院暑期课程圆满结课

近日,由国产FPGA领军企业易灵思与南京大学集成电路学院联合举办的“深度学习与硬件加速”暑期课程圆满结课。本次课程为期5天(7月7日至7月11日),面向大三本科生,旨在通过理论与实践结合的方式,帮助学生掌握FPGA硬件加速与Ti

HarmonyOS AI辅助编程工具(CodeGenie)报错分析

当DevEco Studio构建ArkTS工程出现失败时,CodeGenie能够对错误进行智能分析,提供错误原因及修复方案,帮助开发者快速解决编译构建问题。

1.如需开启编译报错智能分析和自动修复

发表于 07-11 17:48

esp32cam

这是在使用esp32cam摄像头代码时,报错,具体为啥啊?thread \'main\' panicked at \'assertion failed: `(left != right)`

l

发表于 06-15 13:20

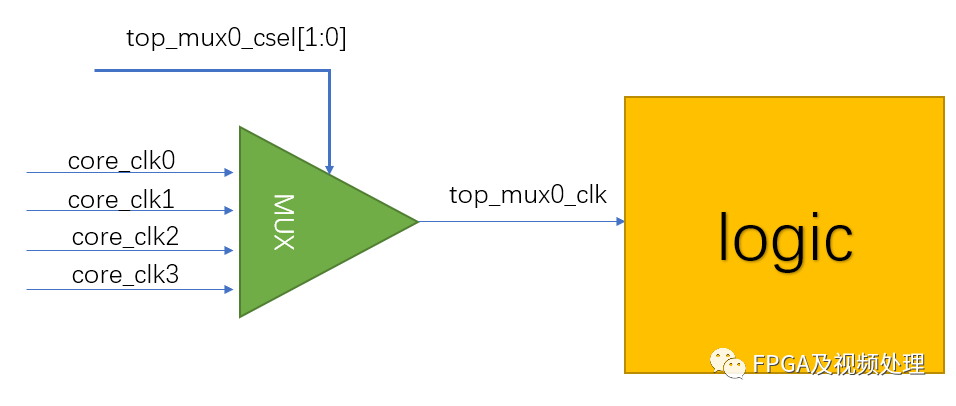

易灵思钛金系列时钟选择功能-2 以Ti60F225为例来介绍如何实现下面的4选择1时钟选择功能

在trion要实现一个4选1时钟复用或许比较麻烦。但是在钛鑫上已经给出了解决方案。这里以Ti60F225为例来介绍如何实现下面的4选择1时钟选择功能。 在FPGA的top,bottom,rig

易灵思Ti180报错分析cannot connect to more than 4 different clocks per region on left and right

易灵思Ti180报错分析cannot connect to more than 4 different clocks per region on left and right

评论