芯片近些年来一直是风口,几乎所有有实力的上市公司都要蹭下这个热度:自研芯片。这也诞生了很多工作岗位,相对于硬件工程师,软件开发工程师能做的事情有限,但是也是非常重要的,而且跟着风口喝口汤也是可以的。整体来说:需求、架构、验证是需要软件参与的,本文结合自己的部分经验,从最基本的芯片设计流程进行介绍,其中会涉及一些可能你经常听到的卡脖子技术。

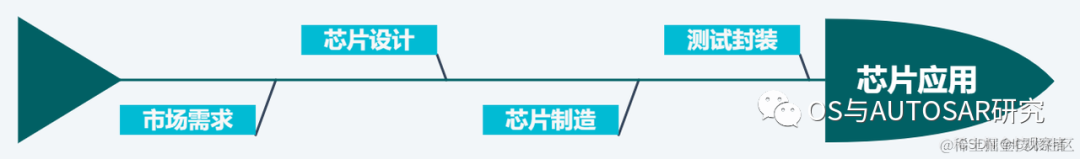

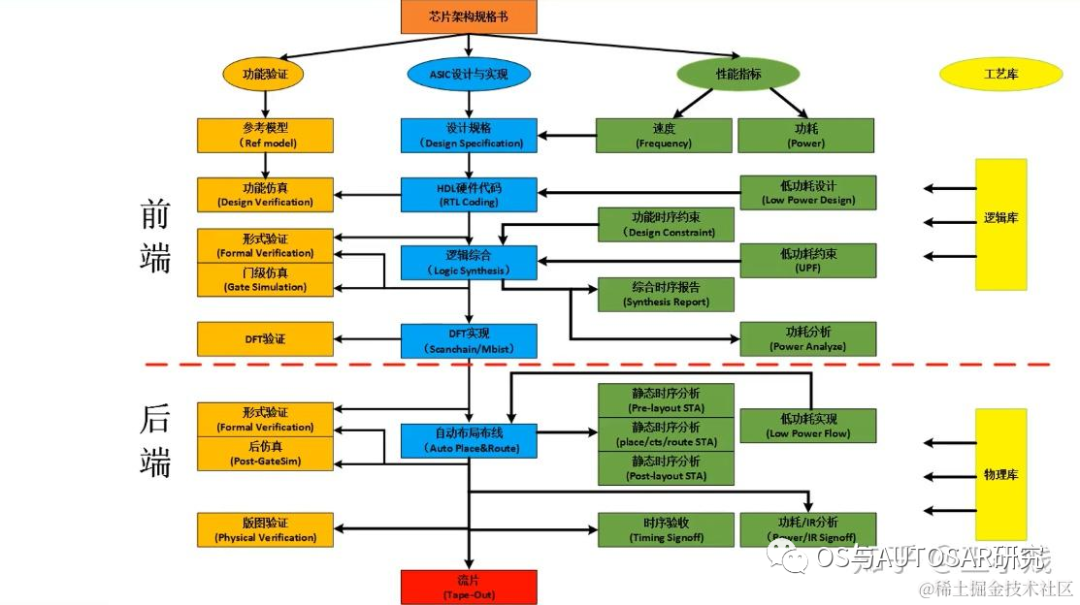

芯片设计的四个步骤,如上图,我们只关注需求和设计,制造和封装不是我们软件工程师能左右的。

1. 市场需求

要做一个芯片,首先得有需求,也就是应用场景,有市场去买单。当前科技时代,电子技术在各方面都有应用,可以说有电路板的地方就有芯片需求。例如手机、电脑、智能家具,我们的衣食住行用等方方面面。

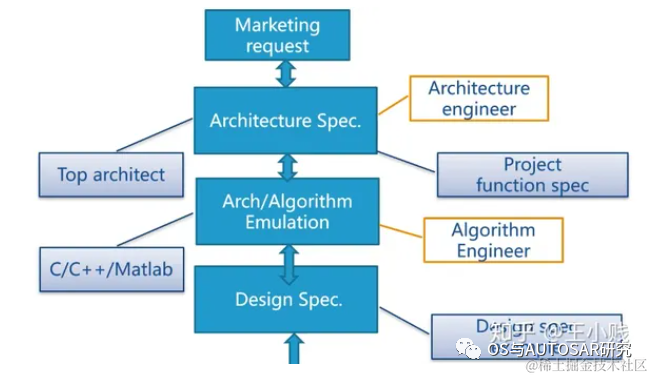

有了需求,就可以根据需求梳理出来我们硬件上需要那些模块功能和性能指标,以及软硬件上要用的技术。这些需要软硬件的架构师进行设计,最终形成Spec。 Spec会确定所有的功能和要求,之后才可以进行芯片设计。

软件在做架构设计的时候,有时候需要进行一些验证,看软件是否支持,可以使用qemu模拟运行的方式看应用能支持不。

软硬件在做架构设计的时候,可以使用很多IC厂商提供的IP集成工具来模拟SoC,就是用纯软件的方式把SoC上的各个IP都添加模拟出来,例如VDK(Virtualizer Development Kit)工具。

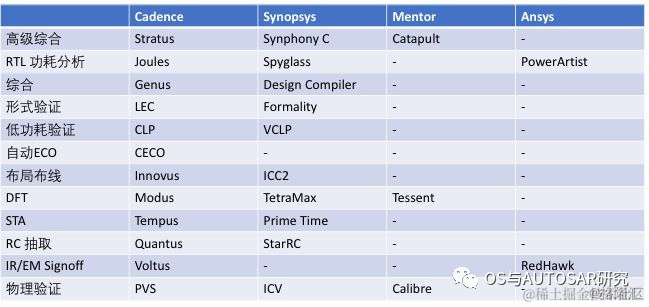

这里说的VDK工具,其实就是一种电子设计自动化EDA(Electronics Design Automation)工具,也就是我们俗称的EDA工具。这是我们卡脖子的技术之一,很复杂,而在芯片设计中非常的重要,贯穿设计、验证和制造,特别是验证可以大力减少出错成本和缩短研发周期。可谓“没有金刚钻,不揽瓷器活”。详细可以参考:浅谈EDA验证工具,芯片开发到底有多难?

VDK与qemu的区别就是qemu支持的芯片型号有限,自己添加很麻烦,要修改qemu的源码。而在VDK图形界面上点一点就可以添加一个IP,而且很多IP是不出名的,厂商私有的不会广泛支持,就需要自己加。所以IP厂商基本会有自己的集成验证工具供客户使用。

芯片开发的周期很漫长,在最开始需求阶段,一些应用上的软件也许就具备开发条件了,例如在qemu上进行app应用的开发,一些依赖于SoC上IP的应用,可以使用VDK做一些数据流的通路开发,并不支持具体的业务,这样后续拿到真正芯片后就可以省略很多一部分研发任务,并且可以提前验证软件技术方案的可行性。

如果软件技术方案不可行需要修改SoC硬件也可以及早的修改。因为芯片研发越到后期修改的成本越大,如果流片了还需要修改,那就快game over了,巨额资金打水漂。所以宁愿先投入研发人员去慢慢磨,也不愿意在硬件上去试错,人可没芯片生产值钱。

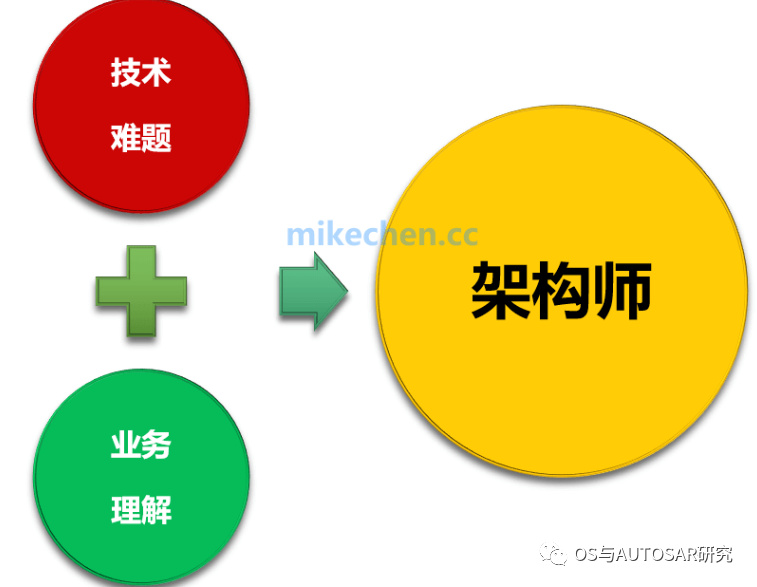

1.2 关于架构师

数字集成电路设计实现流程是个相当漫长的过程,拿手机基带芯片为例,对于3G, 4G, 5G, 工程师最初见到的是无数页的协议文档。

架构师要根据协议来确定:协议的哪些部分可以用软件实现,哪些部分需要用硬件实现;

算法工程师要深入研读协议的每一部分,并选定实现所用算法;

芯片设计工程师,需要将算法工程师选定的算法,描述成RTL;

芯片验证工程师,需要根据算法工程师选定的算法设计测试向量,对RTL 做功能、效能验证;

数字实现工程师,需要根据算法工程师和设计工程师设定的目标PPA 将RTL 揉搓成GDS;

芯片生产由于太过复杂,完全交由代工厂完成,封装亦是;

对于测试,大部分公司都是租借第三方测试基台由自己的测试工程师完成,只有少部分土豪公司才会有自己的测试基台。

架构师是芯片灵魂的缔造者,是食物链的最顶端,是牛逼闪闪的存在。

2. 芯片设计概述

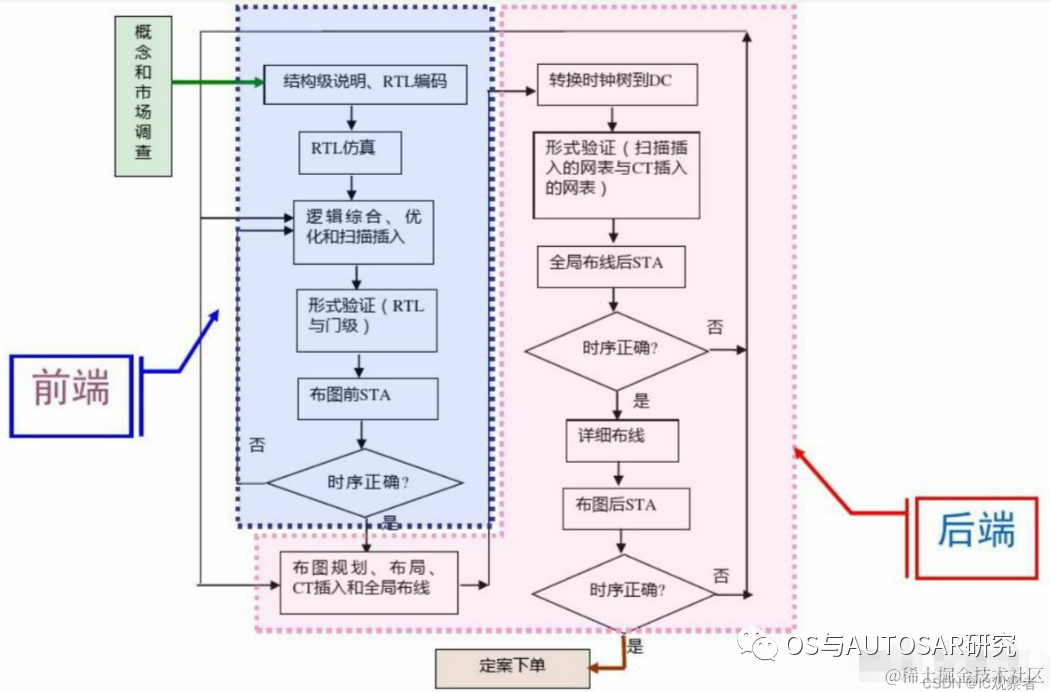

芯片设计分为两部分,前端(逻辑设计)和后端(物理设计)。

这其中很多流程看似高大上,但是有IP供应商提供的工具以后,其实就是界面上点点的事情。 芯片设计中涉及的工具繁多,基本都是老外的,这需要国内芯片公司的崛起,有自己的很多IP后才可以投入到这些工具的研发中去。

有一个说法就是老外掌握一项新技术,首先就是加密做界面化,不提供源码然后商业卖钱。而这个周期要延迟一两年到市场上,而中国则直接推给自己的客户,客户有能力抄的就抄跑了,大家都不太注重商业保密,可能技术比较low不用藏着掖着,大家都是抄的。。。这就是中国速度。

3. 芯片前端设计

RTL设计

验证

静态时序分析

覆盖率

ASIC逻辑综合

3.1 RTL设计

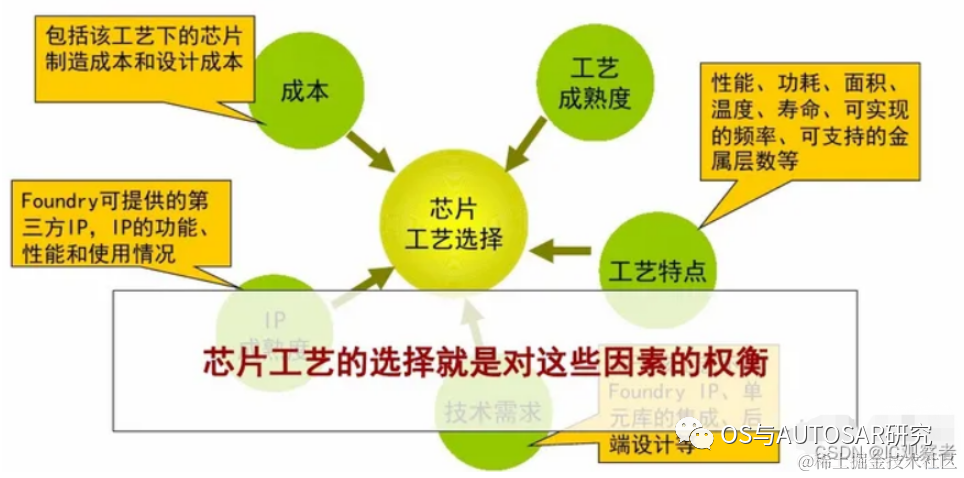

首先要确定芯片的工艺,如下图:

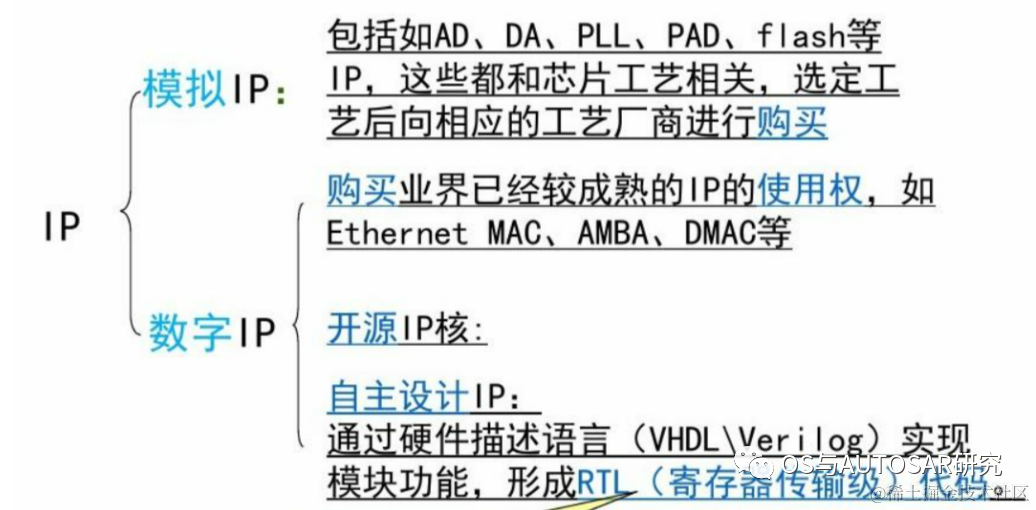

RTL(register transfer level) 设计:利用硬件描述语言,如VHDL,Verilog,System Verilog, 对电路以寄存器之间的传输为基础进行描述。 RTL使用代码编写,来实现功能模块,就是一个个IP。这些IP分为数字IP和模拟IP:

SOC芯片最终由SOC integration工程师把各个IP集成到一起。

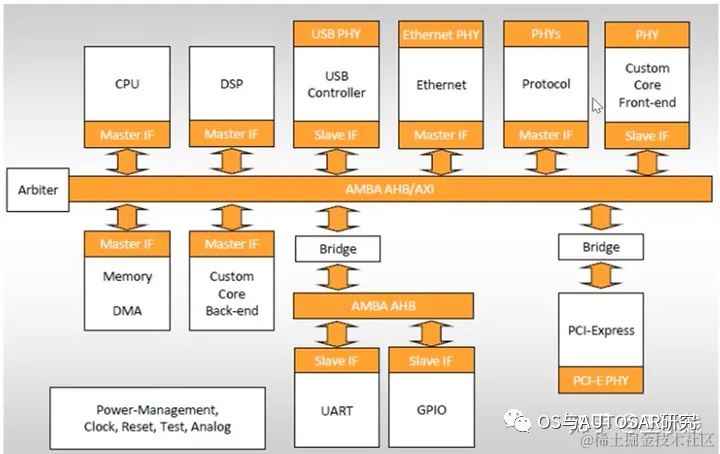

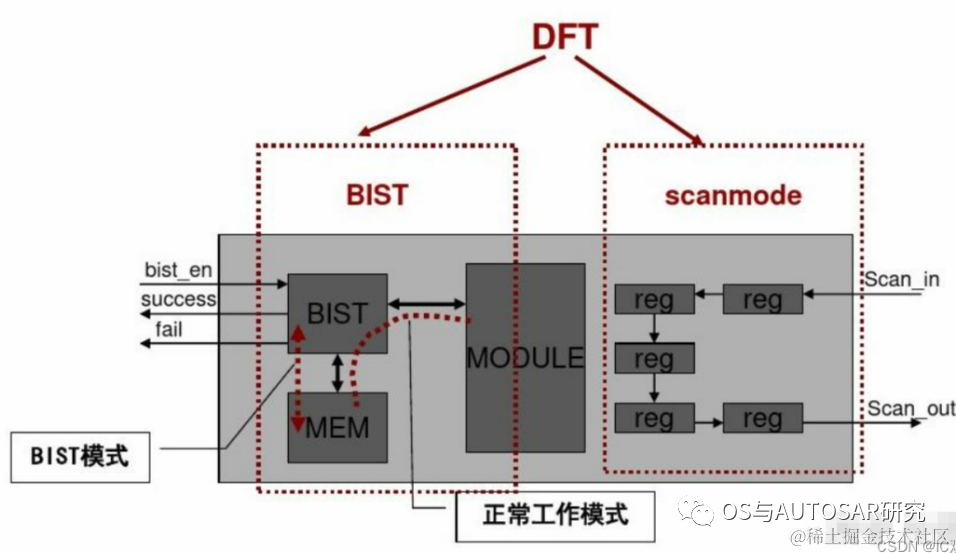

上图中我们可以看到一个典型的SoC有那些IP,例如CPU,DSP,USB外设,memory等。 对于RTL还需要进行支持BIST(自测试),设计的时候也需要做可测性设计DFT(Design For Test)

除了对功能测试,还需要对代码进行自动检查:通过lint, Spyglass等工具,针对电路进行设计规则检查,包括代码编写风格,DFT,命名规则和电路综合相关规则等检查。

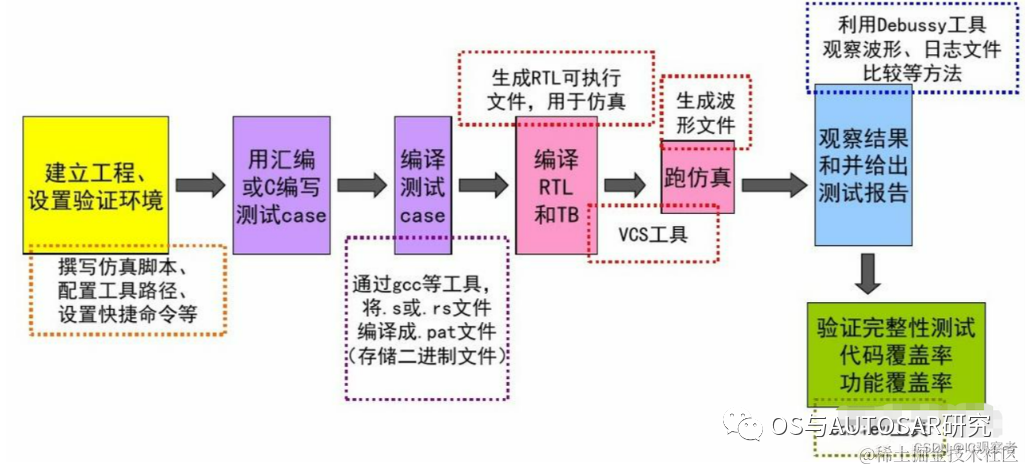

3.2 验证

验证是保证芯片功能正确性和完整性最重要的一环。验证的工作量也是占整个芯片开发周期的50%-70%,相应的,验证工程师与设计工程师的数量大概在2-3:1。从验证的层次可以分位:模块级验证,子系统级验证和系统级验证。从验证的途径可以分为:模拟(simulation),仿真和形式验证(formality check)。

这里又出现了芯片验证,这里软件开发人员又来活了,之前在qemu、VDK上模拟的程序现在可以在RTL上模拟了,这里是越来越贴近硬件了。在多平台验证虽然很繁琐,就像验证完一个玩具系统,然后继续下一个,好似没有用,但是每一次都是在进步。

这里需要注意的一点就是在各个验证平台下的代码复用问题,大的模块差异可以通过编译时区分,小的差异可以通过运行时读取标志寄存器来在代码里面走不同分支或加载不同的配置文件区分,这里需要把握一个度。 一点经验:多用配置文件例如xml、dts、config文件,不用宏,直接debug版本适应所有验证平台,编译时借助编译工具脚本自动区分。

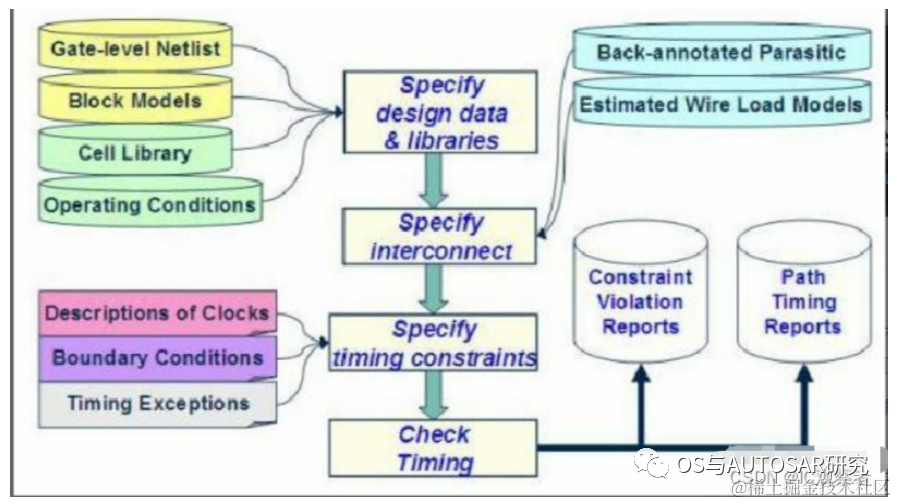

3.3 静态时序分析(STA)

静态时序分析是套用特定的时序模型(timing model),针对特定电路,分析其是否违反designer给定的时序限制(timing constraint)。

目前主流的STA工具是synopsys的Prime Time。

静态时序分析的作用:

确定芯片最高工作频率

通过时序分析可以控制工程的综合、映射、布局布线等环节,减少延迟,从而尽可能提高工作频率。

检查时序约束是否满足

可以通过时序分析来查看目标模块是否满足约束,如不满足,可以定位到不满足约束的部分,并给出具体原因,进一步修改程序直至满足要求。

分析时钟质量

时钟存在抖动、偏移、占空比失真等不可避免的缺陷。通过时序分析可以验证其对目标模块的影响。

3.4 覆盖率

覆盖率作为一种判断验证充分性的手段,已成为验证工作的主导。从目标上,可以把覆盖率分为两类:代码覆盖率 作用:检查代码是否冗余,设计要点是否遍历完全。检查对象:RTL代码 功能覆盖率 作用:检查功能是否遍历 检查对象:自定义的container 在设计完成时,要进行代码覆盖率充分性的sign-off, 对于覆盖率未达到100%的情况,要给出合理的解释,保证不影响芯片的工能。

3.5 ASIC综合

逻辑综合的结果就是把设计实现的RTL代码翻译成门级网表(netlist)的过程。

在做综合时要设定约束条件,如电路面积、时序要求等目标参数。

工具:synopsys的Design compiler, 综合后把网表交给后端。

至此我们前端的工作就结束啦!

4. 后端设计

1. 逻辑综合 2. 形式验证 3. 物理实现 4. 时钟树综合-CTS 5. 寄生参数提取 6. 版图物理验证

4.1 逻辑综合

同3.5中前端的逻辑综合

4.2 形式验证

1)验证芯片功能的一致性 2)不验证电路本身的正确性 3)每次电路改变后都需验证 形式验证的意义在于保障芯片设计的一致性,一般在逻辑综合,布局布线完成后必须做。工具:synopsys Formality

4.3 物理实现

物理实现可以分为三个部分:

布局规划 floor plan

布局 place

布线 route

物理实现可以分为三个部分:

布局规划 floor plan

布局 place

布线 route

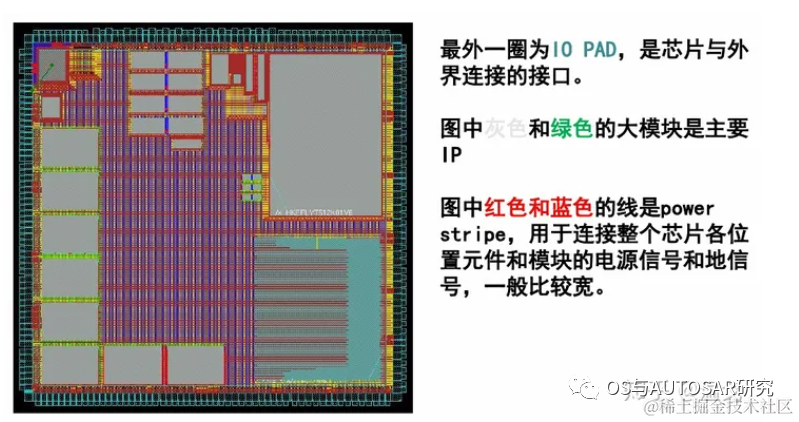

布图规划floor plan 布图规划是整个后端流程中作重要的一步,但也是弹性最大的一步。因为没有标准的最佳方案,但又有很多细节需要考量。 布局布线的目标:优化芯片的面积,时序收敛,稳定,方便走线。 工具:IC compiler,Encounter 布图规划完成效果图:

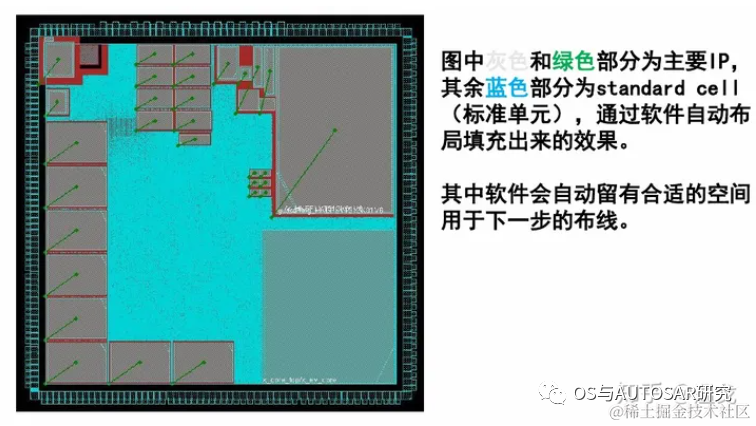

布局

布局即摆放标准单元,I/O pad,宏单元来实现个电路逻辑。 布局目标:利用率越高越好,总线长越短越好,时序越快越好。 但利用率越高,布线就越困难;总线长越长,时序就越慢。因此要做到以上三个参数的最佳平衡。 布局完成效果图:

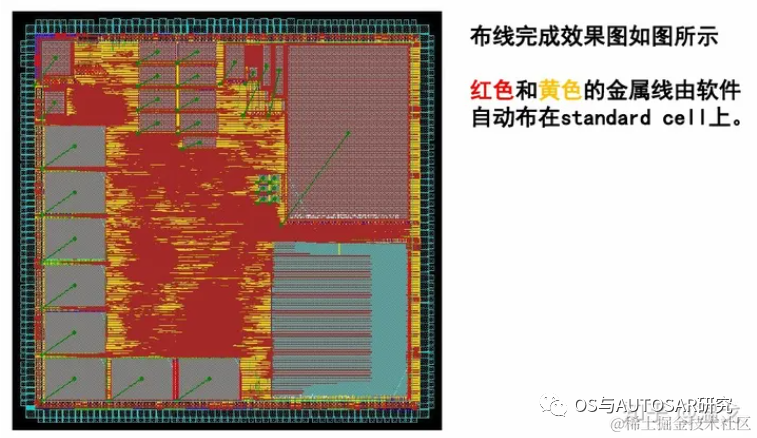

布线

布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束条件下,根据电路的连接关系,将各单元和I/O pad用互连线连接起来。

4.4 时钟树综合——CTS

Clock Tree Synthesis,时钟树综合,简单点说就是时钟的布线。 由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。

4.5 寄生参数提取

由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。 工具Synopsys的Star-RCXT

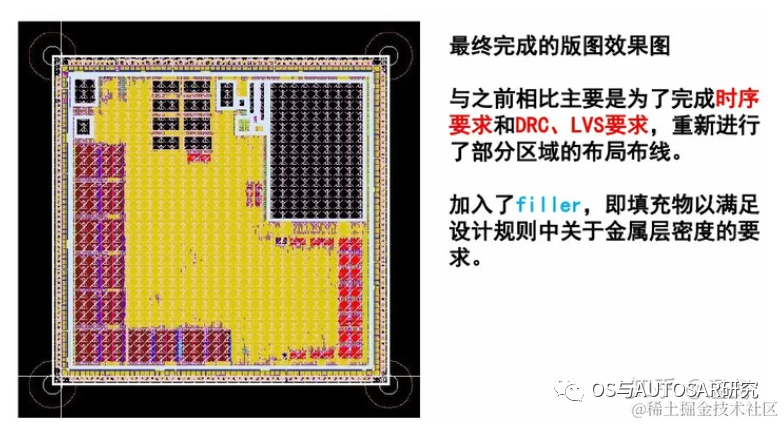

4.6版图物理验证

这一环节是对完成布线的物理版图进行功能和时序上的验证,大概包含以下方面: LVS(Layout Vs Schematic)验证:简单说,就是版图与逻辑综合后的门级电路图的对比验证; DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求; ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气规则违例; 实际的后端流程还包括电路功耗分析,以及随着制造工艺不断进步产生的DFM(可制造性设计)问题等。

物理版图以GDSII的文件格式交给芯片代工厂(称为Foundry)在晶圆硅片上做出实际的电路。

最后进行封装和测试,就得到了我们实际看见的芯片。

审核编辑:刘清

-

EDA工具

+关注

关注

5文章

276浏览量

34145 -

芯片设计

+关注

关注

15文章

1176浏览量

56789 -

SoC设计

+关注

关注

1文章

151浏览量

19617 -

SPEC

+关注

关注

0文章

34浏览量

16520 -

ASIC芯片

+关注

关注

2文章

96浏览量

24921

原文标题:芯片-设计流程入门

文章出处:【微信号:OS与AUTOSAR研究,微信公众号:OS与AUTOSAR研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片设计流程基础知识入门

芯片设计流程基础知识入门

评论