在高速ADC中增加SFDR的主要限制是什么?

高速ADC是现代电子器件中一个十分重要的组成部分, 通常在工业、汽车、航空以及军事等领域应用广泛。随着技术的发展,高速ADC的性能也不断得到了提高,但是同时也面临一些挑战。其中最有意义的是如何提高高速ADC的SFDR,这可以提高信号的精度和准确性。

SFDR即“串扰自由动态范围”,代表着ADC在高频输入信号下输出第一个谐波之后的最高谐波信号跟原信号的分离度。在实际应用中,信号动态范围比串扰自由动态范围更为常用,但是SFDR更能代表ADC的精度。因此,提高ADC的SFDR非常重要。

提高高速ADC的SFDR需要解决几个主要问题。首先是信号的抽样。ADC需要将连续的模拟信号转化为离散的数字信号。在抽样时需要注意信号频率尽量低于采样率的一半,以避免混淆和失真。如果频率超过了一半,就会产生混叠的现象,导致原始信号的失真。因此,要提高SFDR,就需要确保信号的抽样频率足够高,以避免混叠。

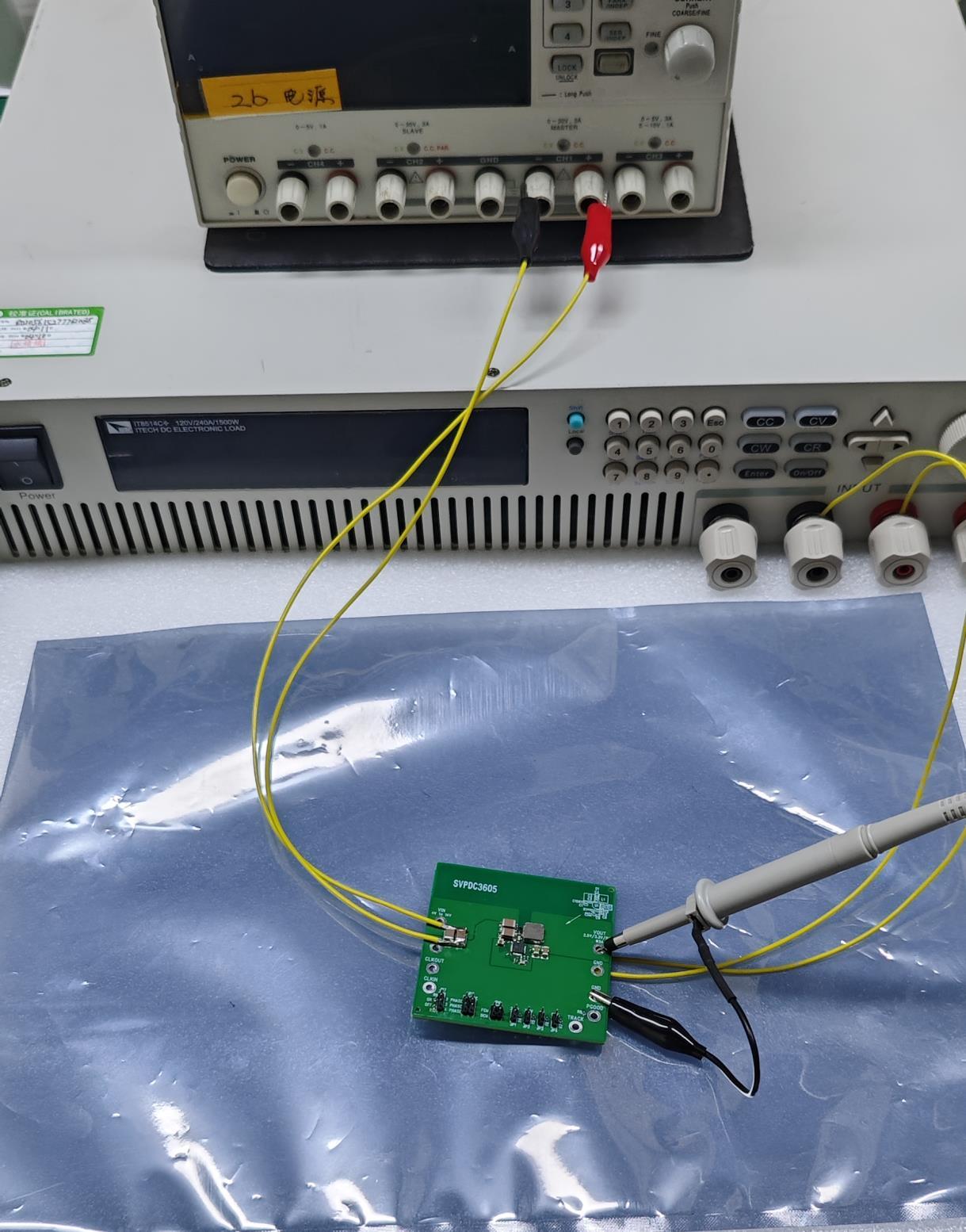

其次,要确保ADC的时钟和信号相互协调。ADC需要在准确的时钟信号下进行抽样和量化。如果时钟信号存在抖动或者失真,就可能会导致采样误差和失真。因此,在设计高速ADC时,需要考虑时钟信号的准确性和稳定性,以确保ADC的性能。

第三,ADC需要在合适的温度和工作电压下运转。温度和电压变化会对ADC的性能产生重要影响,影响因素包括输入噪声和抖动等因素。因此,为了提高ADC的SFDR,需要考虑ADC的工作环境。

最后,要考虑ADC的反馈机制。在ADC的设计过程中,反馈控制是十分重要的。反馈机制可以帮助防止信号过冲或者欠冲,从而提高ADC的稳定性。同时,反馈控制也可以调整ADC的抽样和量化速率,以满足不同的应用需求。

总之,在提高高速ADC的SFDR方面,需要注意信号抽样、时钟准确性、温度和工作电压变化、以及反馈机制等关键因素。只有同时兼顾这些方面,才能够在高速ADC设计中取得优异的性能。

-

adc

+关注

关注

100文章

7950浏览量

557010 -

谐波

+关注

关注

7文章

966浏览量

44689 -

SFDR

+关注

关注

0文章

56浏览量

13478

发布评论请先 登录

高速8位ADC:MX7575/MX7576的深度解析

12位高速IF采样ADC——AD9433的技术解析与应用指南

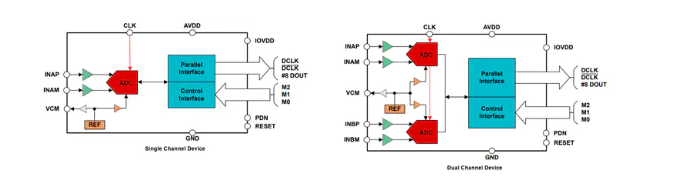

LTC2281:高性能10位双通道ADC在高速信号处理中的应用

12 位高速 ADC AD9432:性能剖析与应用指南

AD4087:高速低噪SAR ADC的卓越之选

高速低功耗ADC在流量计中的应用

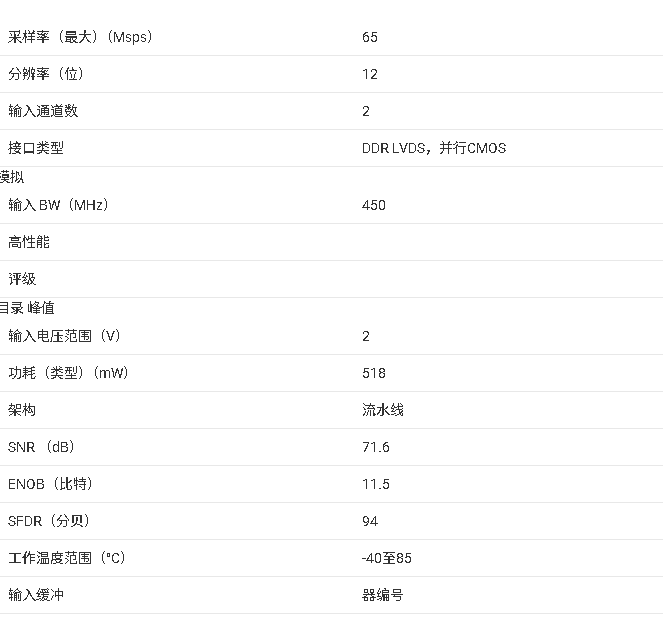

ADS62P2X 系列双通道12位ADC数据手册总结

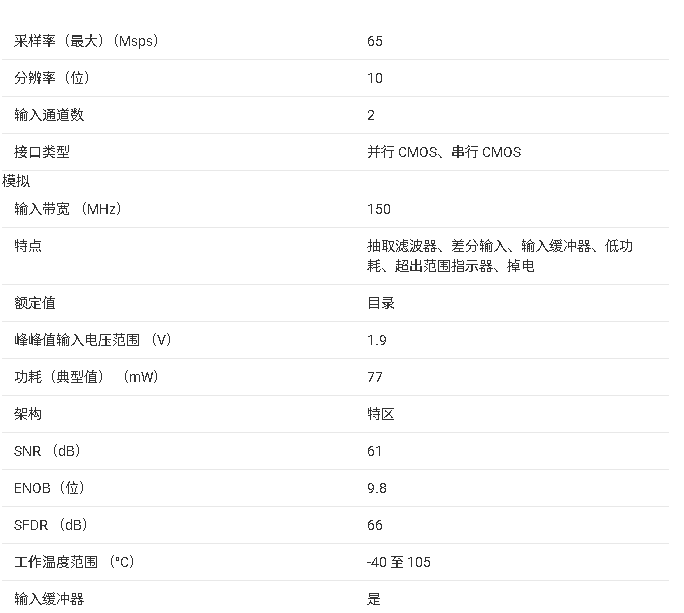

ADC3910D065 10 位高速低功耗 ADC 技术文档总结

Texas Instruments ADC3908Dx/ADC3908Sx 8位高速ADC数据手册

在高速ADC中增加SFDR的主要限制是什么?

在高速ADC中增加SFDR的主要限制是什么?

评论