PLL对射频输入信号有什么要求?

PLL(Phase Locked Loop)是一种电路,可将输入信号和参考信号的相位和频率保持一致,用于频率合成、时钟生成、调制解调、数字信号处理、无线通信等一些领域。PLL对射频输入信号有着一定的要求,以下是详细说明。

1. 频率范围要匹配

PLL的输入信号应该与其工作范围相符。通常,PLL电路的工作范围会在一定范围内变化,这意味着输入信号应该在PLL的频率带宽内。如果输入信号的频率超出了PLL的工作范围,那么它就不能被正确地处理。

2. 输入信号的幅度应合适

PLL对输入信号的幅度要求也非常严格,输入信号的幅度应该恰好在合适的范围内。如果幅度太小,那么信号会被淹没在PLL内部电路噪声中;如果幅度太大,那么可能会导致电路失效或者损坏。

3. 输入信号的稳定性

对于PLL电路而言,输入信号的稳定性也是一个非常重要的方面。由于PLL会将输入信号的相位和频率与参考信号保持一致,因此输入信号本身的稳定性相当于影响了PLL的工作。因此,输入信号应该尽可能地稳定,并且应该保持相对恒定的幅度和相位。

4. 输入信号的信噪比要求

在无线通信系统中,信噪比是一个非常重要的参考参数。对于PLL而言,输入信号的信噪比也是一个关键的方面。输入信号中的噪声会被PLL电路放大,因此输入信号的信噪比应该越高越好。

5. 输入信号的谐波要求

输入信号的谐波也是一个需要考虑的关键参数之一。当输入信号具有较强且随机的谐波时,PLL的边界环节可能会出现不稳定的情况,这会影响整个电路的工作。

6. 输入信号的相位噪声要求

对于一个高精度的PLL电路而言,输入信号的相位噪声也是一个重要的方面。相位噪声可以导致PLL的相位或频率不稳定,从而影响整个电路的性能。因此,输入信号的相位噪声要求较低。

总之,PLL对射频输入信号的要求是比较严格的,需要考虑到频率范围、幅度、稳定性、信噪比、谐波、相位噪声等多个方面。只有在这些方面都能够满足要求之后,PLL电路才能够正常工作。

-

调制解调器

+关注

关注

3文章

881浏览量

40582 -

pll

+关注

关注

6文章

976浏览量

137592 -

射频信号

+关注

关注

6文章

242浏览量

21814

发布评论请先 登录

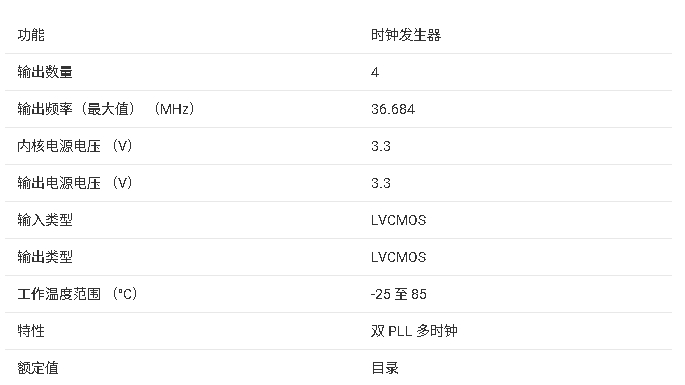

PLL1707/PLL1708 双PLL多时钟发生器技术文档总结

TLC2933A 高性能锁相环 (PLL) 芯片技术文档摘要

易灵思 FPGA TJ375的PLL的动态配置

PLL用法

是德示波器在射频信号调制分析中的应用

ups电源—UPS电源安装,输入电压有什么要求?

安泰:功率放大器的主要要求有哪些

PLL对射频输入信号有什么要求?

PLL对射频输入信号有什么要求?

评论