关于高速串行信号隔直电容的PCB设计注意点

在高速串行信号传输中,隔直电容是一种常见的解决信号干扰问题的方法。由于高速信号传输时会产生电磁干扰和相邻信号交叉干扰,隔直电容可以将交流信号通路隔离开来,从而达到保护信号完整性的目的。下面将详细介绍高速串行信号隔直电容的PCB设计注意事项。

1. 布局原则

在进行高速串行信号隔直电容的PCB布局时,需要遵循以下原则:

(1)将高速信号线和低速信号线分开布局,且尽可能避开高功率和高噪声的元器件,如DC/DC转换器、开关电源等。

(2)串行线两侧应尽量布满电源层或地层,防止层间耦合干扰。

(3)直线信号线应尽可能直线,减少拐弯和仿真。

(4)保持隔直电容尽量靠近发送器和接收器,线路长度尽可能短。

(5)隔直电容应固定于信号线的两端,不要让它们穿过板上的孔。

2. 隔直电容的选择

隔直电容是高速传输中必需的元器件,它们可以起到过滤掉直流分量的噪声或使信号通路中的电压保持稳定的作用。因此选择合适的隔直电容也非常重要。

(1)选用小尺寸电容器,以减小带宽影响。

(2)选用低ESR、低ESL、高Q值电容器,以减小损耗和降低谐振频率。

(3)选用高频响应快的电容器,以减小串扰。

(4)了解信号的特性和噪声源,选择合适的电容值和数量。

3. 隔直电容布局

在隔直电容的布局时,需要注意以下几点:

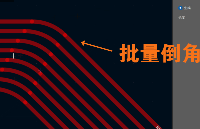

(1)隔直电容应该尽量布在信号线的两端,保持与信号线平行,避免出现拐弯后造成的系列电感或电容。

(2)为减小隔离电容和相邻电容的串扰,应保持一定距离,并保证相邻电容的参考地点一致。

(3)为避免镜像地线模式干扰,在单面布线时,两个隔直电容不应该放在同一条直线上。

4. 线宽和距离

对于高速串行信号线,线宽和距离对信号的传输质量和芯片的发热都有重要影响。以下是应注意的线宽和距离:

(1)为了减小串扰和衰减,线宽应根据高速信号的数据速率、驱动电流和板上的损耗,选择合适的线宽。对于高速信号,线宽应该越宽越好,以减小线路阻抗。

(2)高速平面内信号线之间的距离对于减小串扰和衰减很重要。在线路设计时应保证不同电路层之间都有合适的间隔。

5. 避免反射

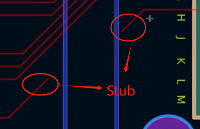

在信号线两端应该尽可能避免反射。因为反射信号会相加或相消,造成信号和噪声的干扰。反射信号的强度取决于信号线长度、速度以及阻抗匹配程度,因此,为减少信号反射,应注意以下几个方面:

(1)线路长度应控制在一定范围内。

(2)对于不同信号线,阻抗应匹配,避免出现阻抗不匹配的情况。

(3)针对高速信号,可以使用末端阻抗匹配电路和电源引出电阻来减少反射。

综上所述,高速串行信号隔直电容的PCB设计需要综合考虑信号线的布局、隔直电容的选择及布局、线宽和距离以及如何避免反射等因素。通过合理的PCB设计,可以保证高速串行信号传输中的稳定性和可靠性。

-

PCB设计

+关注

关注

396文章

4907浏览量

94009 -

电磁干扰

+关注

关注

36文章

2462浏览量

107591 -

隔直电容

+关注

关注

0文章

15浏览量

4729

发布评论请先 登录

【「高速数字设计(基础篇)」阅读体验】 + 书籍评测第一篇

PCB设计如何用电源去耦电容改善高速信号质量

PCB设计仿真,“缝合电容”我怎么可能不知道

开关电源的输入电容的PCB设计技巧

深度解析:PCB高速信号传输中的阻抗匹配与信号完整性

pcb设计时注意事项

PCB设计中的Stub天线对信号传输的影响

关于高速串行信号隔直电容的PCB设计注意点

关于高速串行信号隔直电容的PCB设计注意点

评论