点击蓝字关注我们

SiC MOSFET 具有独特的栅极驱动要求。一般来说,它在导通期间需要一个 20V、Vdd 栅极驱动来提供尽可能低的导通电阻。与对应的硅器件相比,它具有更低的跨导、更高的内部栅极电阻,且栅极导通阈值可低于 2 V。因此,在关断期间,栅极必须拉低至负电压(通常为 -5 V)。了解和优化栅极驱动电路对可靠性和整体开关性能具有非常大的影响。

本系列文章将重点介绍 SiC MOSFET 特有的器件特性,并介绍了栅极驱动优化设计的关键需求,以最大限度地提高 SiC 开关性能。另外还将讨论系统级考虑因素,例如启动、故障保护和稳态切换。本文为第一部分,将介绍SiC MOSFET 特有的器件特性。

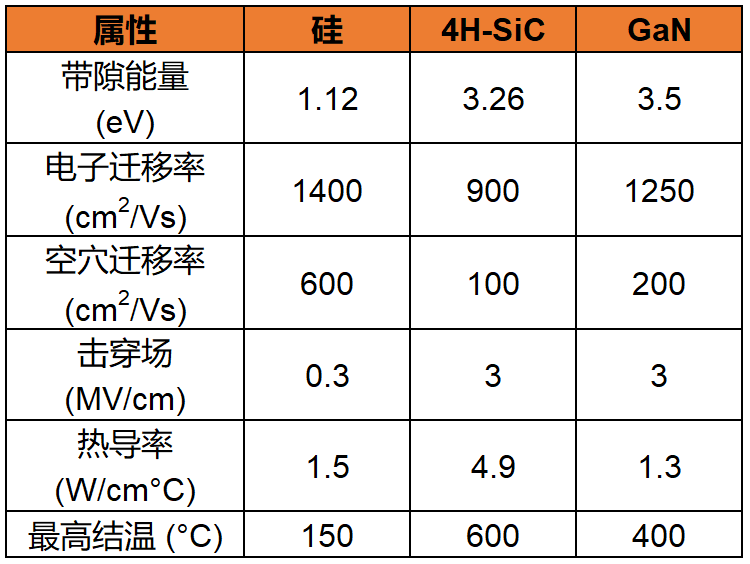

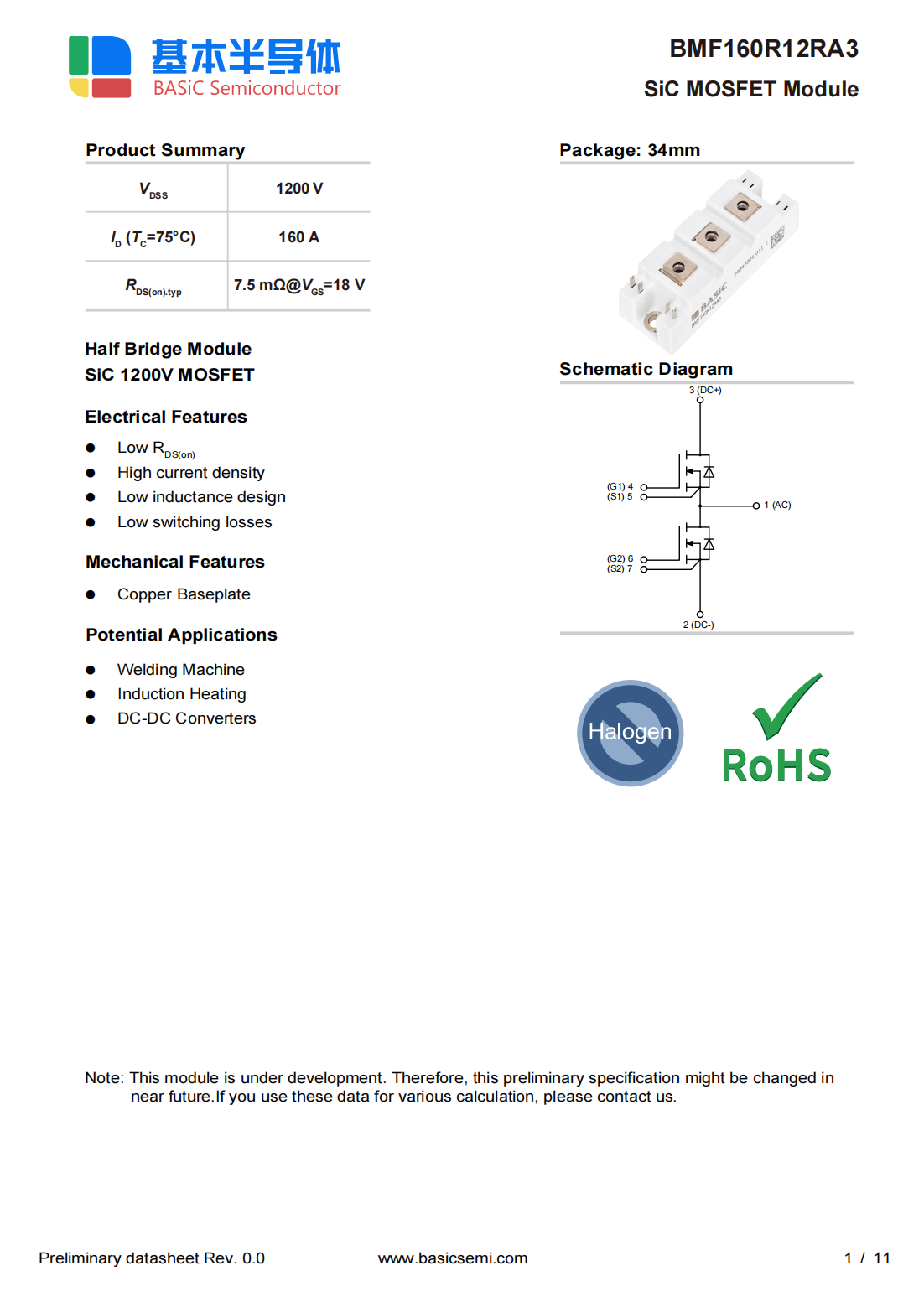

碳化硅 (SiC) 属于宽禁带 (WBG) 半导体材料系列,用于制造分立功率半导体。如表 1 所示,传统硅 (Si) MOSFET 的带隙能量为 1.12 eV,而 SiC MOSFET 的带隙能量则为 3.26 eV。

SiC 和氮化镓 (GaN) 具有更宽的带隙能量,意味着将电子从价带移动到导带需要大约 3 倍的能量,从而使材料的表现更像绝缘体而不像导体。这使得 WBG 半导体能够承受更高的击穿电压,其击穿场稳健性是硅的 10 倍。对于给定的额定电压,较高的击穿场可以减小器件的厚度,从而转化为较低的导通电阻和较高的电流能力。SiC 和 GaN 都具有与硅相同数量级的迁移率参数,这使得两种材料都非常适合高频开关应用。然而,与硅和 GaN 相比,SiC 最与众不同的参数是其热导率高出 3 倍以上。对于给定的功耗,较高的热导率将转化为较低的温升。商用 SiC MOSFET 的最高保证工作温度为 150°C < Tj < 200°C。相应地,SiC的结温最高可以达到 600℃ ,但其主要受键合和封装技术的限制。这使得 SiC 成为适用于高压、高速、高电流、高温、开关电源应用的优质 WBG 半导体材料。

表 1.半导体材料属性

SiC MOSFET 通常适用于电压范围 650 V < BVDSS <1.7 kV,主要集中在 1.2 kV 及以上。在 650 V 的较低范围内,传统的硅 MOSFET 和 GaN 优于 SiC。但是,考虑使用较低电压的 SiC MOSFET 的原因之一可能是利用其出色的热特性。

尽管 SiC MOSFET 的动态开关行为与标准硅 MOSFET 非常相似,但由于其器件特性,必须要考虑到其独特的栅极驱动要求。

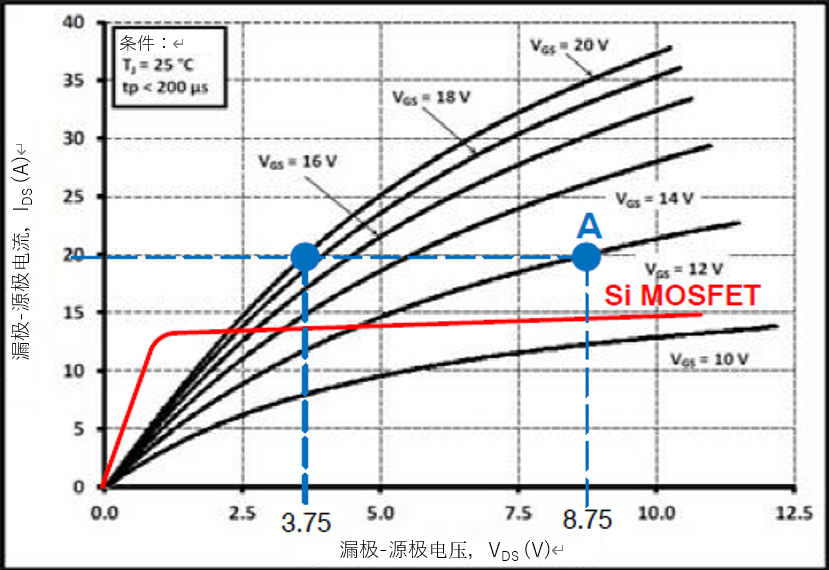

开关电源中使用的硅 MOSFET 在两种工作模式或区域之间尽可能快地开关。当栅极-源极电压 VGS 小于栅阈值电压 VTH 时,晶体管处于高阻状态,此时被称为截止区域。在截止期间,漏极-源极电阻 RDS 是高阻状态,漏极电流 ID = 0 A。饱和区发生在 MOSFET 完全增强时,即 VGS >> VTH,此时 RDS(on) 为最小值或接近最小值,ID 达到最大值,晶体管处于高导通状态。如图 1 中红色轨迹所示,线性(欧姆)区和饱和区之间的转换非常尖锐和明显,因此一旦 VGS > VTH,漏极电流就会通过相对较低的 RDS。跨导 gm 是漏极电流变化量与栅极电压变化量之比,它定义了 MOSFET 的输出-输入增益,也就是对于给定的 VGS,I-V 输出特性曲线的斜率。

图 1.SiC MOSFET 输出特性

硅 MOSFET 的 I-V 曲线在线性区(大 ΔID)的斜率很陡峭,而在饱和区时几乎是平的,因此在 VGS > VTH 时具有非常高的增益(高 gm)。对于给定的 VGS,ID 趋于平坦,这意味着硅 MOSFET 在饱和时表现得很像一个非理想的电流源。相反,在图 1 中显示的输出特性曲线可以看出,SiC MOSFET 在线性和饱和工作模式之间的转换并不剧烈。事实上,没有定义的“饱和区”,从这个角度看,SiC MOSFET 的行为更像可变电阻而不是非理想的电流源。SiC MOSFET 的 I-V 输出特性未表现出小 ΔVGS 时出现大 ΔID,因此,SiC MOSFET 被认为是低增益(低 gm)器件。

唯一弥补低增益并强制大幅改变 ID 的方法是施加非常大的 VGS,这对 RDS 有很大影响。为了进一步说明这一点,请考虑图 1 中标记为 A 和 B 的两个工作点。

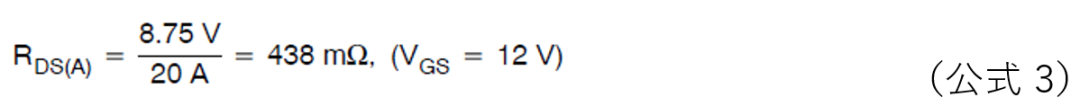

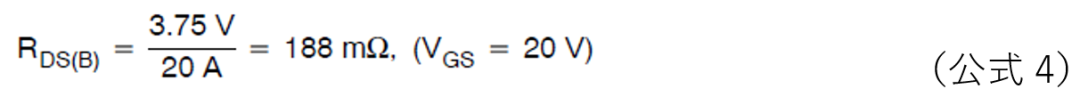

当 VGS = 12 V 时,固定的漏极电流 ID = 20 A 会导致 VDS = 8.75 V,而当 VGS 增加到 20 V 时,VDS = 3.75 V。将公式 (3) 和 (4) 的结果进行比较,可以发现在 VGS = 12 V 时电阻和导通损耗是在 VGS = 20V 时的 2.3 倍。

因此,当施加的最大栅极-源极电压在 18 V < VGS < 20 V 之间时,SiC MOSFET 的性能最佳,有些甚至可以高达 VGS = 25 V。SiC MOSFET 在低 VGS 下运行可能会导致热应力或可能由于高 RDS 而导致故障。与低 gm 相关的缓解效应非常重要。它直接影响在设计合适的栅极驱动电路时必须考虑的几个重要动态特性:特别是导通电阻、栅极电荷(米勒平台区域)和过流 (DESAT) 保护。

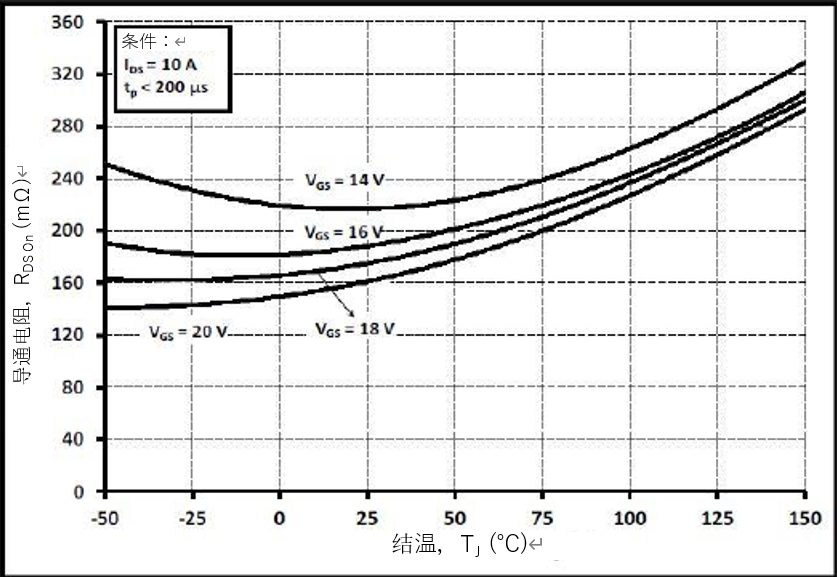

作为 WBG 半导体,SiC MOSFET 在给定电压下每单位面积的导通电阻较低。MOSFET 的导通电阻由几个内部的、与 VGS 有关的电阻元件组成。最值得注意的是通道电阻 (RCH)、JFET 电阻和漂移区域电阻 (RDRIFT)。RCH 具有负温度系数 (NTC),在较低的 VGS 下占据了 RDS 的主导地位。相反,RJ 和 RDRIFT 具有正温度系数 (PTC),在较高的 VGS 水平上占主导地位。对于 VGS > 18 V,导通电阻具有明显的 PTC 特性。然而,在较低的 VGS 下,导通电阻与结温特性呈现抛物线形状,如图 2 所示。具体而言,在 VGS = 14 V 时,RCH 占主导地位,RDS 呈现出 NTC 特性,即电阻随温度升高而降低。这种 SiC MOSFET 的特性直接归因于其低 gm。对于硅 MOSFET,只要 VGS > VTH,RDS 始终具有 PTC 特性。

图 2.SiC MOSFET 导通电阻与结温

对于大多数大电流应用案例,当两个或更多 MOSFET 并联放置时,PTC 属性在很大程度上依赖于均流。在并联运行期间,当一个 MOSFET 的结温升高时,PTC 会导致 RDS 增加、电流降低并迫使并联 MOSFET 承受额外的电流,直到出现自然平衡。如果两个或多个 SiC MOSFET 并联放置,同时以低 VGS(负 NTC)电压工作,结果将是灾难性的。因此,为确保可靠的 NTC 操作,只有当 VGS 足够高(通常 VGS > 18 V)时才建议使用 SiC MOSFET 之间的并联操作。

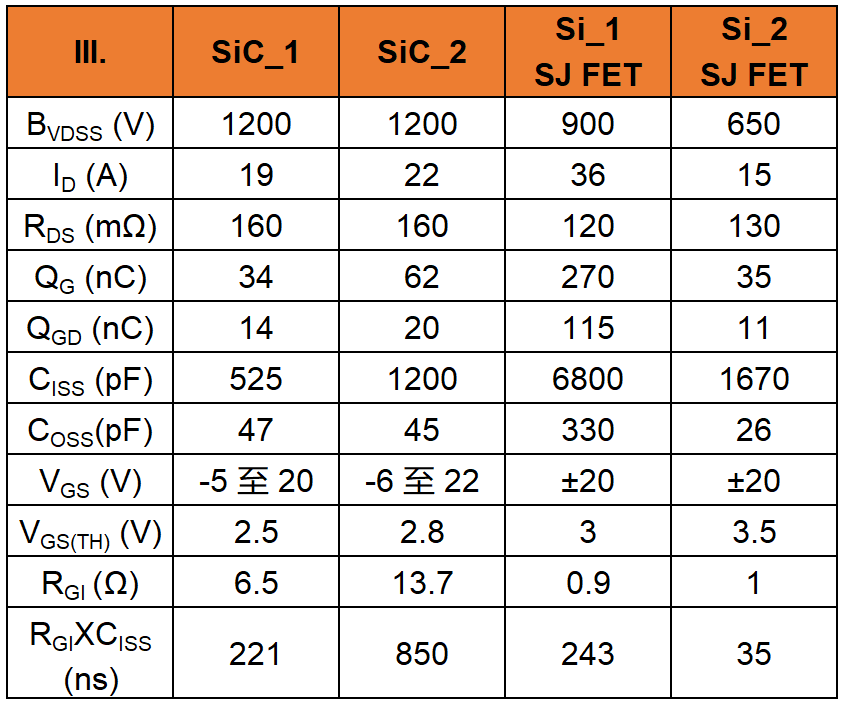

内部栅极电阻 RGI 与芯片尺寸成反比,对于给定的击穿电压,由于 SiC MOSFET 芯片与硅 MOSFET 芯片相比小得多,内部栅极电阻往往更高。更小的 SiC MOSFET 芯片的真正好处在于更低的输入电容 CISS,这意味着所需的栅极电荷 QG 更低。表 2 重点介绍了两个不同制造商的 SiC MOSFET(SiC_1 和 SiC_2)和两个出色的 900-V 和 650-V 超级结 Si MOSFET(Si_1 和 Si_2)之间的几个重要参数比较。

表 2. 半导体材料属性

从栅极驱动的角度来看,比较 RGIxCISS 时间常数是很有意义的。Si_2 器件具有极低的 35 ns 时间常数,但也是一个额定电流较低、额定电压较低的 MOSFET。出于比较目的,650-V、Si_2 MOSFET 很值得关注,因为 1200-V、SiC_1 样品的参数与之非常接近,但具有明显较低的 CISS 和几乎两倍的额定 BVDSS。在 BVDSS 方面,Si_1 样品与两个 SiC 样品之间更为接近。由于 SiC_1 的 QG 较低,因此 Si_1 和 SiC_1 之间的时间常数非常接近,即使 SiC_1 的内部栅极电阻是 Si_1 的 7 倍。

内部栅极电阻限制了可以注入 CISS 的栅极驱动电流。高性能 SiC 栅极驱动电路需要提供极低的输出阻抗,这样驱动器就不会因为已经很高的 RGI 而成为限制因素。这使得设计人员可以通过增加或减少外部栅极电阻来更加自由地控制 VDS 和 dV/dt 的转换。

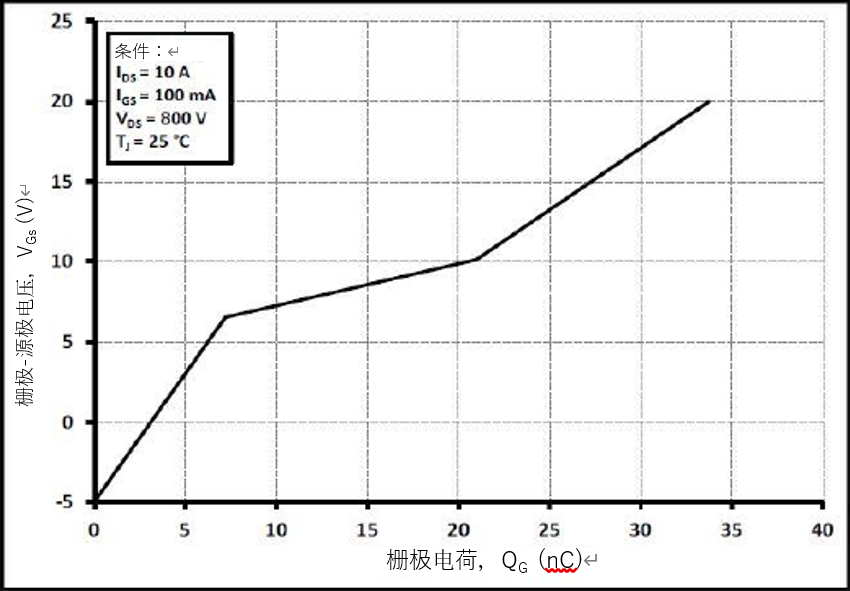

当施加 VGS 时,会传输一定量的电荷,以尽可能快地改变在 VGS(MIN) (VEE) 和 VGS(MAX) (VDD) 之间变化的栅极电压。由于 MOSFET 内部电容是非线性的,因此 VGS 与栅极电荷 (QG) 曲线有助于确定对于给定的 VGS 水平需要传递多少电荷。SiC MOSFET 的典型栅极电荷曲线如图 3 所示。

图 3.SiC MOSFET,栅极-源极电压与栅极电荷

有趣的是,SiC MOSFET 的米勒平台区域出现在更高的 VGS,并且不像硅 MOSFET 那样平坦。一个非平坦的米勒平台区域意味着 VGS 在相应的电荷范围 QG内不是恒定的。这是与 SiC MOSFET 相关的低 gm 引起的另一个结果。还值得注意的是,QG = 0 nC 并不出现在 VGS = 0 V 时。VGS 必须将电压拉低至负电压(在本例中为 -5 V)才能使 SiC MOSFET 的栅极完全放电。在关断期间将栅极切换为负极的第二个原因是最坏情况下的 VTH 可以低至 1 V。在 0V < VGS < VDD 之间切换 VGS 且 Vth ~ 1 V 的情况下,可以避免因意外的的栅极噪声或 VDS 导致不慎导通,即 dV/dt 造成的导通。因此,几乎所有 SiC MOSFET 都需要最低 VGS 处于 -5 V < VGS(min) < -2 V 的范围,但一些制造商规定最小为 -10 V。

DESAT 保护是一种过流检测,起源于驱动 IGBT 的电路。在导通期间,如果 IGBT 不能再保持饱和状态(“去饱和”),集电极-发射极电压将开始上升,同时全集电极电流流过。显然,这会对效率产生负面影响,或者在最坏的情况下,可能导致 IGBT 故障。造成这种情况的可能原因可能包括:由于 β 公差、温度影响、短路或过载导致的基极电流不足。所谓的“DESAT”功能的目的是监测 IGBT 的集电极-发射极电压,并检测何时存在这种潜在的破坏性条件。

尽管故障机制略有不同,但在最大 ID 流过时,SiC MOSFET 可能会遭受 VDS 上升的类似情况。如果导通过程中的最大 VGS 过低、栅极驱动导通过慢或存在短路或过载条件,则可能会出现这种不良情况。在最大 ID 存在的情况下,RDS 可能会增加,导致 VDS 意外但缓慢上升。

由于 SiC MOSFET 不在明确定义的饱和区工作,因此它永远不会作为恒流源出现。而因为大多数过流保护方案都依赖于 MOSFET 在过流条件下模拟非理想的恒流源,这种情况下可能就会有问题。当 SiC MOSFET 经历去饱和事件时,VDS 响应非常缓慢,而最大漏极电流继续流过不断增加的导通电阻。因此,在漏极-源极电压可以响应之前,漏极电流可能达到最大额定脉冲电流的 10-20 倍(在高 RDS 期间)。对于高频电源转换器,在识别出饱和故障之前,可能会发生许多开关周期。因此,DESAT 是一项重要且必要的保护功能,除了作为电源控制的过流保护之外,还应将其指定为栅极驱动电路的一部分。

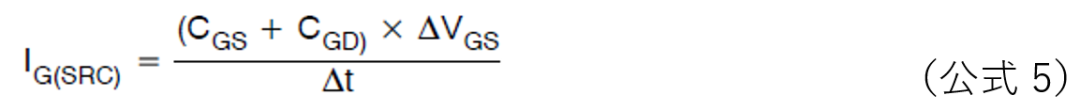

SiC MOSFET 的开关曲线与 Si MOSFET 非常相似,主要区别在于导通期间的 20 V 栅极驱动幅度以及关断期间栅极必须拉至地以下。导通转换需要一个大的峰值源电流,能够尽快为 SiC 内部栅极电容充电,以最大限度地减少开关损耗。根据估计,整个导通事件应在 ΔVGS = 30 V 和 CISS = CGS + CGD = 1000 pF(估计值)的情况下在 Δt < 10 ns 内完成,根据公式 (5),这将产生所需的峰值电流 IG(SRC)=3 A:

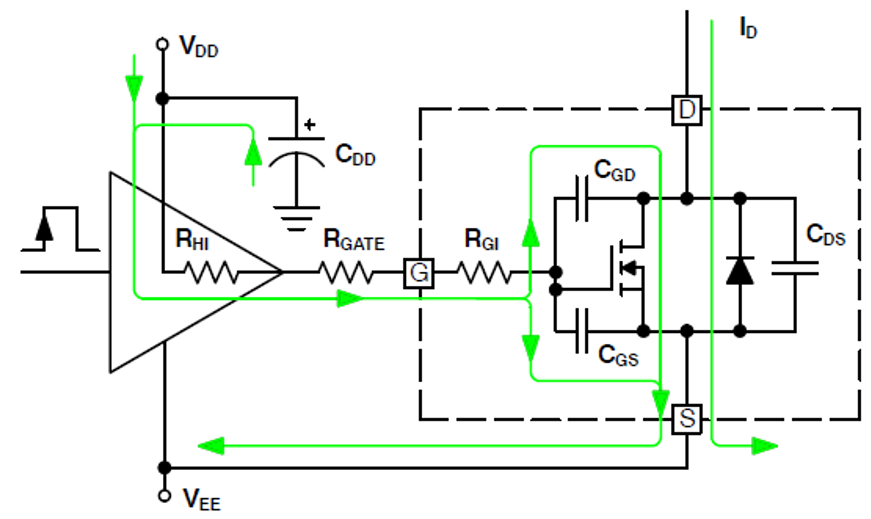

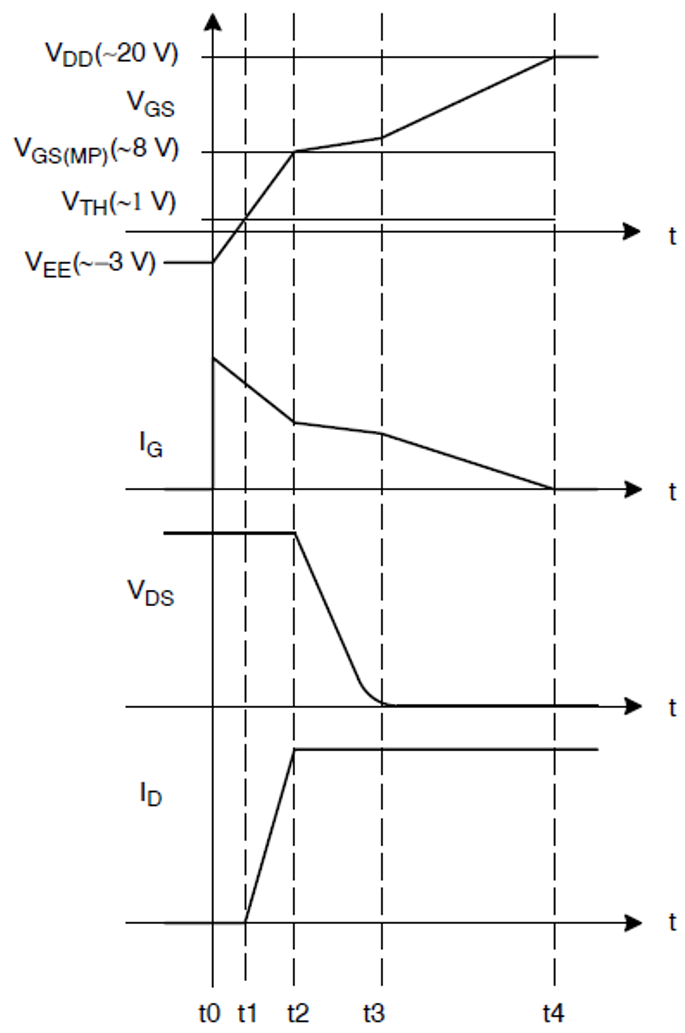

SiC MOSFET 的导通转换由四个不同的时间间隔定义,如图 5 所示。图 5 和图 7 中显示的时间间隔代表了理想箝位电感开关应用的预期时间,这是开关电源中使用的典型工作模式。

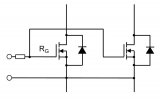

图 4.SiC MOSFET 源极电流

图 5.SiC MOSFET 导通顺序

t0→t1:VGS 从 VEE 逐渐上升到 Vth,因为栅极驱动电路必须提供大量瞬时栅极电流 IG(SRC),主要从栅极驱动器大容量电容 CVDD 中存储的电荷中供应。这个时间间隔通常被称为“导通延迟”,因为当 VGS 低于 VTH 时,ID 和 VDS 不受影响。大部分栅极电流用于为 CGS 和 CGD 充电。请注意图 4 中的原理图,源极电流通过三个电阻器流过:RHI、RGATE 和 RGI。其中,RHI 是驱动器源极的等效内部电阻,RGATE 是电路板上电阻阻抗加上任何附加的阻尼电阻,而 RGI 是 SiC MOSFET 内部的栅极电阻。RHI 和 RGATE 的阻值大约为几欧姆,但对于 SiC MOSFET,RGI 可能达到数十欧姆的数量级,比高压 Si MOSFET 高一个数量级。由于这三个电阻器与 SiC 内部栅极电容形成 RC 时间常数,因此需要提供足够的峰值栅极电流以确保栅极驱动信号的快速上升沿。

t1→t2:当 VGS 从 VTH 上升到米勒平台区域时,由于 RDS 通道电阻在低 VGS 时没有完全增强,因此 ID 通过 RJ + RDRIFT 开始增加。由于 SiC 本征体二极管尚未处于阻断状态且 RDS 的高电阻状态,因此 VDS 保持在最大水平。建议不要在 VGS < 13 V 的情况下操作 SiC MOSFET,因为在低 VGS 时 RDS 很高,存在热失控的风险。因此,至关重要的是栅极驱动电路能够尽快地从 VTH 过渡到 VGS > 13V。在 Vth < VGS < 13 V 的时间应该尽量少于几纳秒,以最小化 ID2xRDS 动态功率损耗。

t2→t3:VGS 处于米勒平台区域,对于 SiC MOSFET,该平台区域发生在 8 V 左右。在此期间,满载电流流过 RDS 并且本征体二极管不再处于阻断状态,从而使漏极电压下降。通道电阻继续下降,但 RDS 仍然由 RCH 主导。尽管满载电流流过 MOSFET 漏极,RDS 在这个 VGS 低点仍然很高。因此,当务之急是 VGS 尽快通过该区域过渡。由于这个过渡的速度由 IG 驱动,所以在米勒平坦区域 (~ 1/2 VDD) 的峰值驱动电流能力比任何栅极驱动器 IC 数据表中显示的峰值额定值更为重要。

t3→t4:在米勒平坦区域的末端附近的 VGS(MP) 处,VDS 下降到高于零点的 ID x RDS。当 VGS 从 ~8 V < VGS < 20 V 过渡时,通道电阻 RCH 继续下降,现在 RJ + RDRIFT 对 RCH 占主导地位,导致 VDS 成比例地下降。大多数 SiC MOSFET 在 VGS > 16 V 时变得完全增强,但最低 RDS 值最终由 VGS 的最大值确定。剩余的栅极电流 IG 被分割来为 CGD 和 CGS 完全充电。

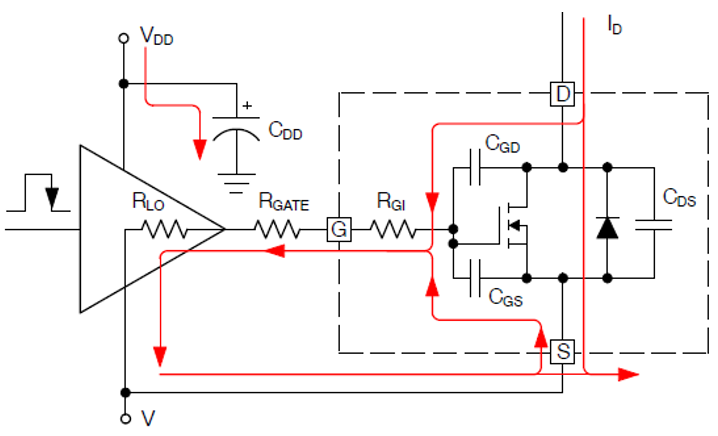

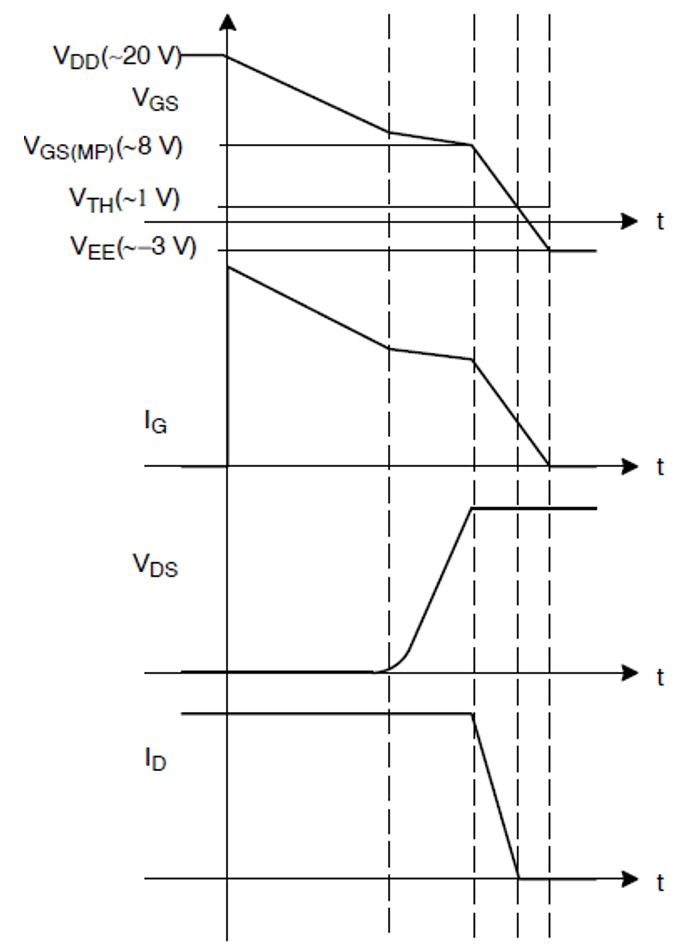

SiC MOSFET 的关断过程基本上与前面描述的导通顺序相反。栅极驱动电路的作用是灌入大量的峰值电流,能够对 SiC MOSFET 的 CGD 和 CGS 电容尽快放电。此外,关断期间的栅极驱动器阻抗必须尽可能低,以将 MOSFET 栅极保持在低电平。而由于SiC MOSFET的低VTH电压,这可能会特别麻烦。这不仅需要将 SiC 栅极拉至地以下,而且与额定源电流相比,栅极驱动器的灌电流能力也必须明显更高。栅极驱动电流 IG(SINK) 的流动如图 6 所示。

图 6.SiC MOSFET 灌电流

图 7.SiC MOSFET 关断顺序

t0→t1:VGS 从 VDD 下降到米勒平坦区域 VGS(MP)。灌电流 IG(SINK) 主要由存储在 CGD 和 CGS 中的电荷提供,而栅极驱动器的大容量电容 CVDD 则由 VDD 重新充电。漏极电流 ID 保持不变。随着 VGS 降低,通道电阻增加,导致 VDS 略微增加 IDxRDS 。除了可能在 t0→t1 时间末期附近可能会略微增加,VDS 的边际增加几乎不会被注意到。

t1→t2:在此时间间隔内,栅极电流的提供主要由 CGD 主导,因为 CGS 电容看到的几乎是恒定的 VGS。在米勒平台区域上,VDS 从 ID x RDS 增加到被SiC 本征体二极管钳位的 VDS 轨电压。漏极电流 ID 与前一个时间间隔相比保持不变。由于由于 VGS <1 3 V 和 VDS x ID 同时出现在 MOSFET 上,导致 RDS 增加,因此在此时间间隔内,栅极驱动电路的额定值应足以承受大量电流灌入。在关断期间,这是设计人员需要注意的栅极驱动电流部分,因为必须尽快过渡通过米勒平台区域。

t2→t3:随着 VGS 从米勒平坦区域向 VTH 继续降低,在此间隔期间 ID 逐渐下降至接近于零。此时,VDS 被 SiC 本征体二极管完全钳位到漏极电压轨,这意味着 CGD 电容器已充满电荷。因此,现在大部分灌电流通过 CGS 流过。

t3→t4:ID 和 VDS 保持不变。在最后的关断间隔期间,只有当 VGS 降至 0V 以下时,SiC 内部输入电容器才能完全放电。由于 VTH 仅约为 1V,为了完全放电 CISS,VGS 必须以负电压完成关断序列。重要的是,栅极驱动电路必须提供尽可能低的阻抗。对于高压半桥电源拓扑结构尤其如此,当高边 MOSFET 导通时,中点被高 dV/dt 上拉。低阻抗下拉对于防止 dV/dt 引起的意外导通至关重要。

总之,SiC MOSFET 的导通和关断开关状态涉及四个不同的时间间隔。图 5 和图 7 所示的动态开关波形代表了理想的操作条件。实际上,引线和键合线电感、寄生电容和 PCB 布局等封装寄生参数会对测量波形产生很大影响。在开关电源应用中使用 SiC MOSFET 时,正确的元件选择、PCB 布局优化以及精心设计的栅极驱动电路都是优化性能的关键。

点个星标,茫茫人海也能一眼看到我

原文标题:SiC MOSFET 器件特性知多少?

文章出处:【微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

-

安森美

+关注

关注

33文章

2172浏览量

95851

原文标题:SiC MOSFET 器件特性知多少?

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NVTFS005N04C MOSFET器件的特性与应用分析

一文看懂 | 中国华北、华东地区SiC功率器件厂商2026年最新动态【上】

碳化硅 (SiC) MOSFET 功率器件热设计基础与工程实践

三菱电机SiC MOSFET在工业电源中的应用

碳化硅 (SiC) MOSFET 分立器件与功率模块规格书深度解析与应用指南

倾佳电子碳化硅SiC MOSFET驱动特性与保护机制深度研究报告

派恩杰第三代1200V SiC MOSFET产品优势

浅谈SiC MOSFET器件的短路耐受能力

SiC MOSFET并联均流及串扰抑制驱动电路的研究

安森美SiC Combo JFET的静态特性和动态特性

硅基时代的黄昏:为何SiC MOSFET全面淘汰IGBT?

SiC MOSFET并联运行实现静态均流的基本要求和注意事项

基本半导体碳化硅(SiC)MOSFET低关断损耗(Eoff)特性的应用优势

SiC MOSFET 器件特性知多少?

SiC MOSFET 器件特性知多少?

评论